Сегодня в некоторой русско-американской группе по QA (я не даю ссылку потому что она закрытая, хотя и многочисленная) некий молодой человек задал вопроc как войти в Quality Assurance Automation. Я сказал, что могу показать путь в Design Verification, который является фактически специализированным QA в области проверки функциональности цифровых аппаратных блоков, спроектированных с помощью синтеза из кода на языке описания аппаратуры SystemVerilog (я их собственно и проектирую). Так как получить ответ захотело еще человек десять, я понял, что нужно писать пост. К счастью, я об этом писал более 10 лет, так что можно делать выжимки из предыдущих постов.

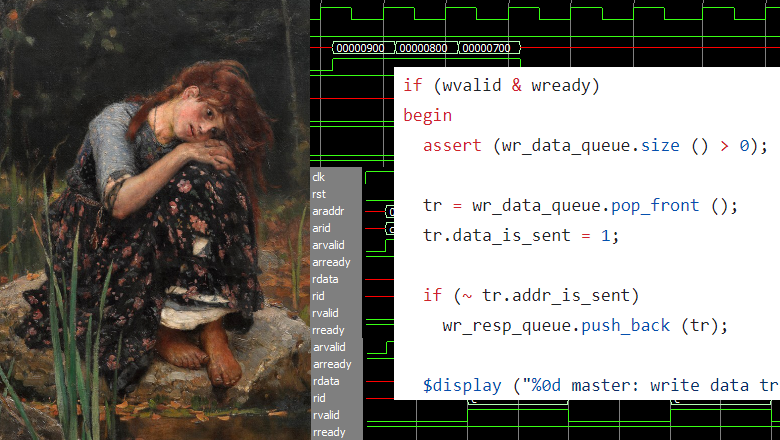

Карьера Design Verification Engineer с писанием сред тестирования на SystemVerilog может понравится опытным программистам, которые хотят сменить карьеру с например писания программ на Джаве. В SystemVerilog есть элементы объектно-ориентированного и симулированно-многопоточного программирования. Суть деятельности заключается в создание фреймворков, которые тестируют хардверные дизайны на прочность, бомбардируя их превдослучайными транзакциями и учитывая покрытие интересных сценариев (functional coverage).