Аннотация

Интерфейс MIPI сегодня становится всё более популярным интерфейсом для подключения камер и дисплеев. По этой причине всё больше отладочных комплектов на основе FPGA содержат на борту соединители интерфейса MIPI – как для подключения камер(ы) и дисплея(ев). Для того чтобы начать работать с новой технологией или просто посмотреть что она собой представляет разработчики пытаются отыскать на просторах интернета подходящее руководство, в котором были бы описаны соответствующие нюансы работы. С одной стороны тестовый пример должен достаточно просто подниматься на отладочном комплекте, а с другой стороны давать достаточно простое и широкое понимание происходящего в этом тестовом примере.

Цель статьи – показать, как начать работать с интерфейсом MIPI используя одну из новейших отладок от Xilinx – SP701, камеру с интерфейсом MIPI от компании Digilent PCAM-5C и среду разработки Vivado+VITIS(SDK) от компании Xilinx

Перечень оборудования

Начиная с первого релиза VITIS и Vivado 2019.2, компания Xilinx даёт разработчикам возможность сгенерировать тестовый пример для работы с MIPI интерфейсом на плате SP701. Ранее проект был доступен и для платы ZCU102, однако в виду того, что пример требовал достаточно специфической камеры, у нас не было возможности запустить тестовый проект. С выходом бюджетной SP701, к которой подключается также бюджетная камера PCAM-5C, такая возможность появилась.

PS0: в руководстве не будет рассказов о том, что такое MIPI, из чего он состоит, и прочей теории, которую можно найти на просторах всемирной паутины. Здесь мы сосредоточимся на том, как сгенерировать тестовый проект. Далее, используя этот проект, Вы самостоятельно можете прикрутить дополнительные модули и видеообработку, оговоренные в ТЗ Вашего проекта.

PS1: Мы не будем разглагольствовать, а сосредоточимся на деле. Только картинки, только хардкор.

Давайте приступим.

Требуемое ПО

Для этого руководства нам потребуется Vivado 2019.2 и VITIS, которые скачиваются по ссылке. VITIS содержит Vivado, поэтому нет необходимости скачивать и VITIS и Vivado, достаточно скачать и установить VITIS. Vivado будет установлена автоматически.

Шаг 1: Создаём проект Vivado

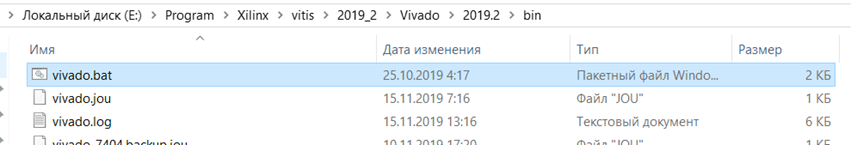

1. Запускаем Vivado 2019.2

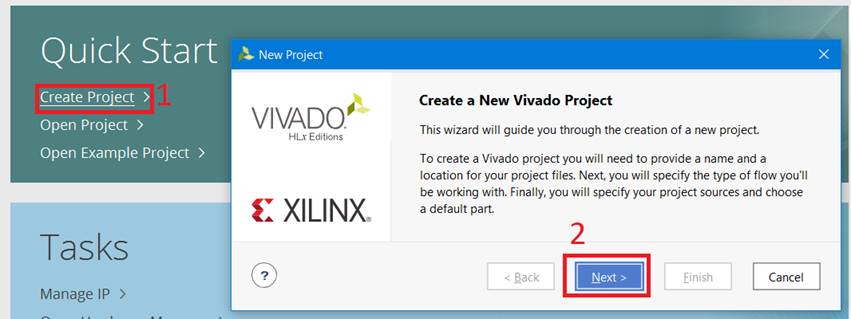

2. Нажимаем «Create project» (1) :: Нажимаем «Next» (2)

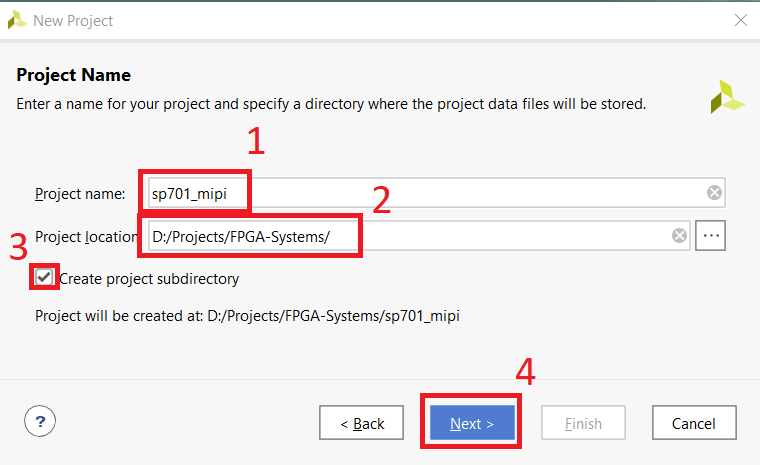

3. Указываем «Project name» (1) :: Указываем директорию проекта (2) :: Устанавливаем галочку (3) :: Нажимаем «Next» (4)

4. Выбираем тип проекта (1) :: Устанавливаем галку (2) :: Нажимаем «Next» (3)

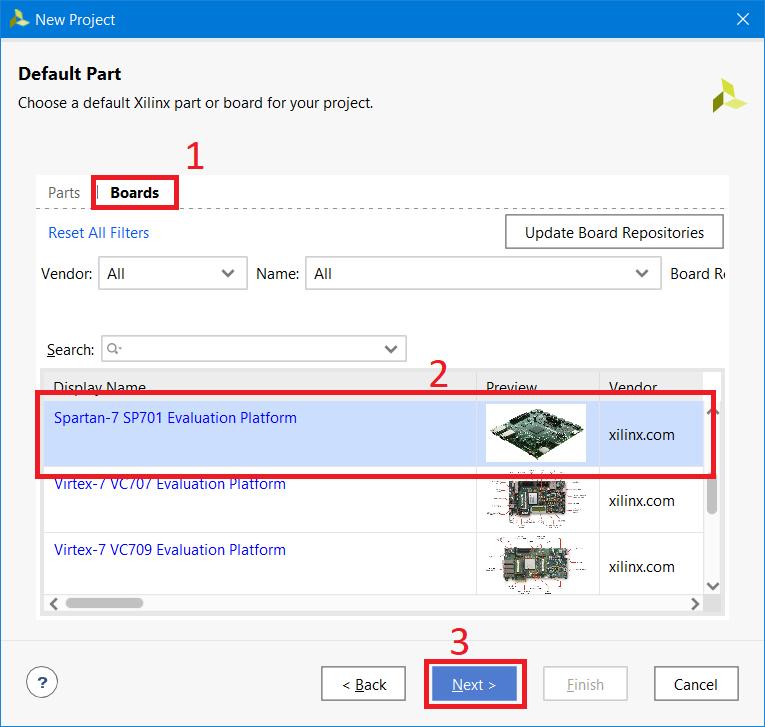

5. Переходим во вкладку«Boards» (1) :: Находим и выбираем SP701 (2) :: Нажимаем «Next» (3)

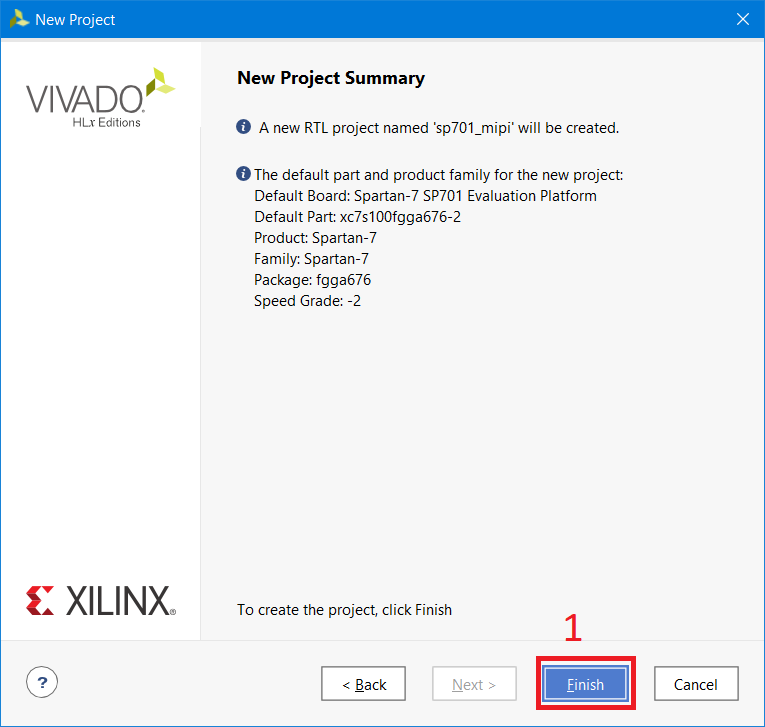

6. Нажимаем «Finish» (1)

Шаг 2: Установка лицензий

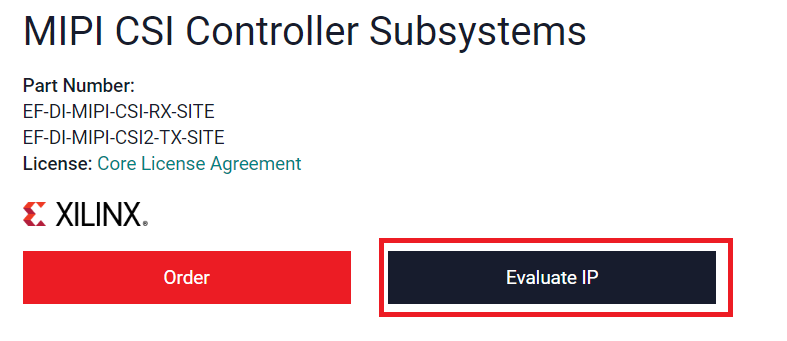

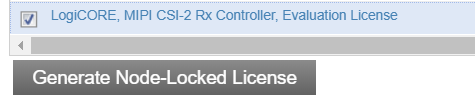

В виду того, что мы будем использовать IP Core, требующие лицензий, нам необходимо их сгенерировать и установить. Тестовый проект использует IP для подключения как камеры (MIPI CSI-Rx) так и дисплея (MIPI DSI-Tx), для которых Xilinx предлагает пробную лицензию со сроком на 120 дней.

P.S.: В тестовом проекте вывод изображения дублируется на интерфейс HDMI, наличие дисплея с интерфейсом MIPI не обязательно, но обязательно наличие лицензии на DSI-Tx.

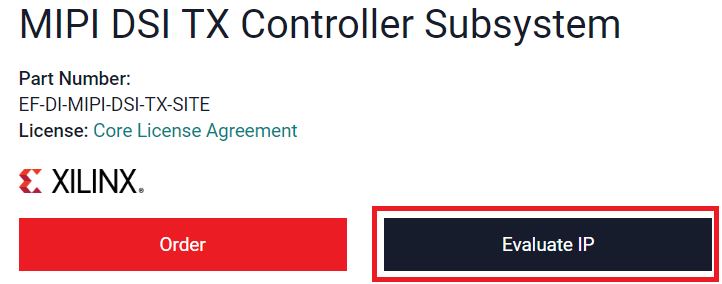

7. Получите лицензию на CSI-Rx (подключение камеры), перейдя по ссылке и нажмите «Evaluate IP». После чего следуйте инструкциям.

8. Получите лицензию на DSI-Tx (подключение дисплея), перейдя по ссылке и нажмите «Evaluate IP». После чего следуйте инструкциям.

9. Скачайте файлы лицензий.

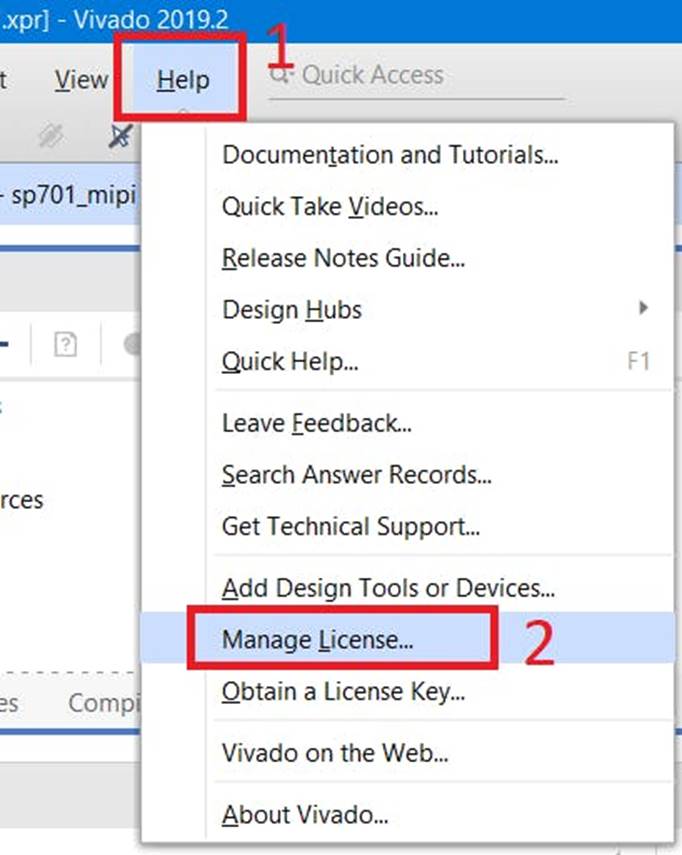

10. В окне Vivado нажмите «Help» (1) :: Выбирите «Manage Licence» (2)

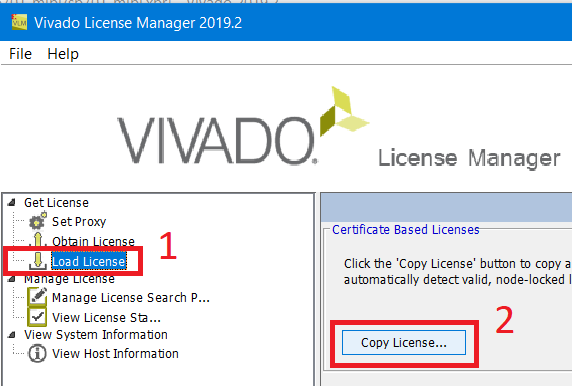

11. В менеджере лицензий выберите «Load licence» (1) :: Затем «Copy licence» (2). Выберите скаченные ".lic" файлы лицензий для CSI и DSI IP ядер

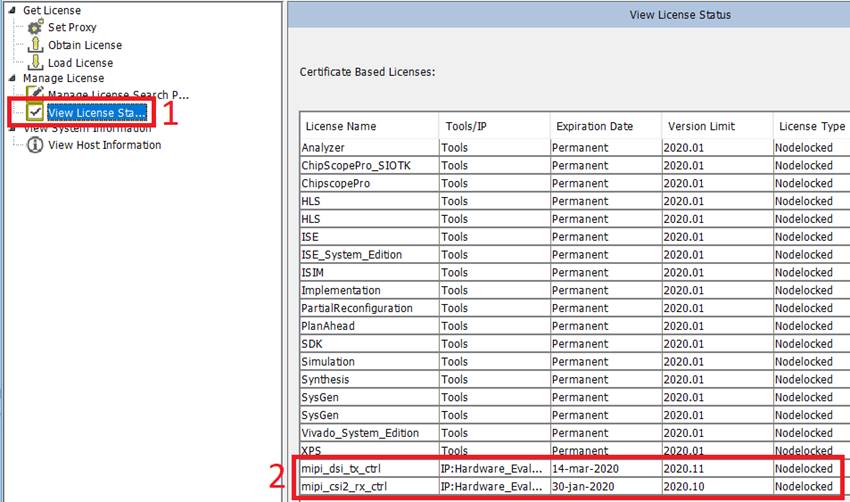

12. В менеджере лицензий выберите «View License Status» (1) :: Убедитесь, что лицензии подцепились корректно (2)

Шаг 3: Создание тестового проекта

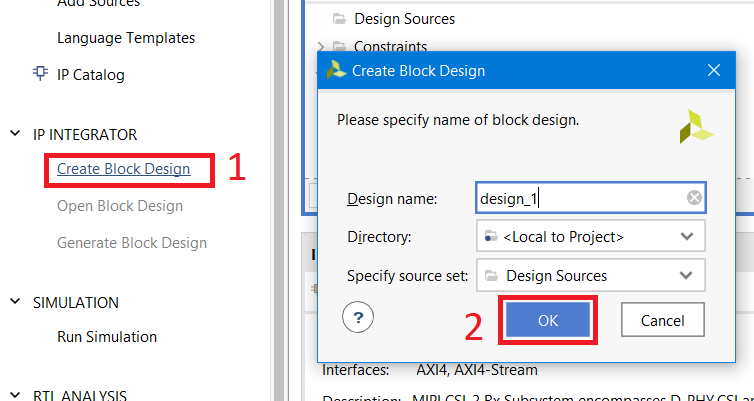

13. В Vivado нажмите «Create block design» (1) :: Нажмите «OK» (2)

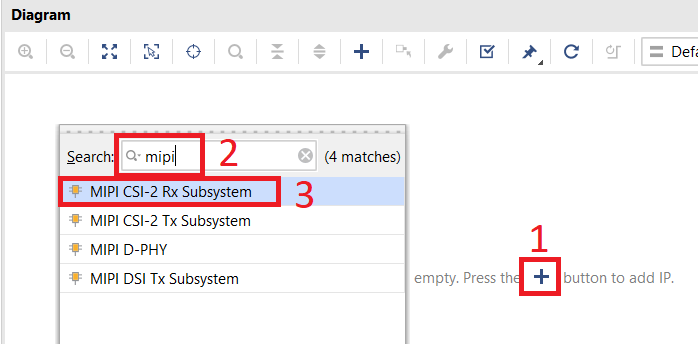

14. На поле IP Integrator нажмите "+" или «ctrl+i» (1) :: Напишите «mipi» в поле «Search» (2) :: Дважды кликните на «MIPI CSI-2 Rx Subsystem» (3)

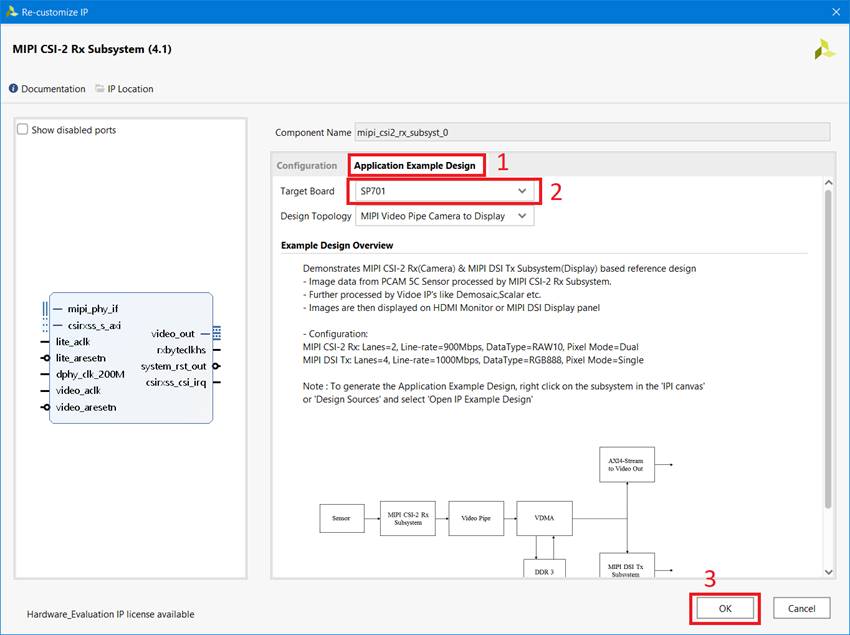

15. Клик правой кнопкой мыши по созданному IP (1) :: Выберите «Customize Block» (2)

16. Перейдите во вкладку «Application Example Design» (1) :: Выберите «SP701» (2) :: Нажмите «OK» (3)

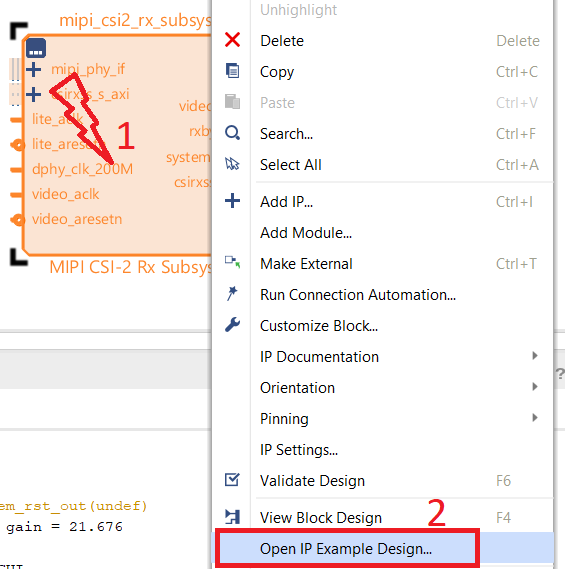

17. Кликните правой кнопкой по IP (1) :: Выберите «Open Example Design» (2)

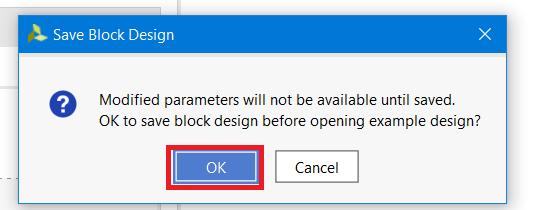

18. Нажмите «OK» для сохранения внесённых изменений проекта

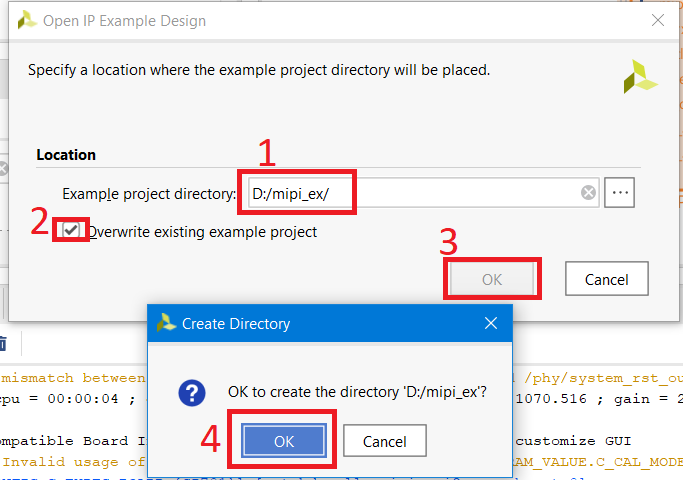

19. Укажите директорию, в которой будет располагаться тестовый проект (Обратите внимание, что для пользователей Windows путь к папке должен быть как можно короче, в противном случае длина пути к внутренним IP ядрам проекта может превысить 260 символов, что вызовет ошибку при создании проекта) (1) :: Установите галку (2) :: Нажмите «OK» (3) :: Нажмите «OK» (4)

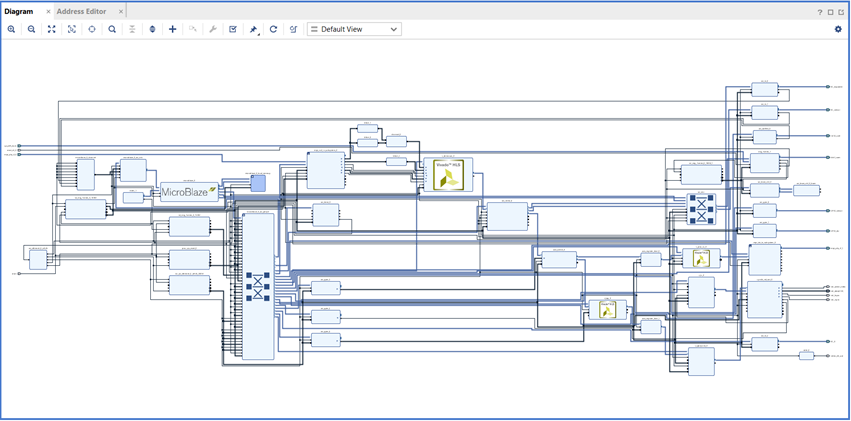

20. Тестовый проект будет открыт в новом окне Vivado. Дождитесь окончания создания проекта. Это займёт несколько минут.

21. В окне тестового проекта нажмите «Generate bitstream» (1) :: Нажмите «Yes» (2)

22. Выберите предпочитаемое количество одновременно синтезируемых IP (1) :: Нажмите «OK»

23. Дождитесь окончания создания файла прошивки ПЛИС (bitstream)

Шаг 4: Настройка и подключение

24. Подключите PCAM-5C камеру к соединителю MIPI CSI на плате SP701

25. Подключите HDMI монитор и/или MIPI дисплей к пате SP701

26. Подключите кабель uUSB к плате SP701

27. Включите питание платы SP701

28. Откройте приложение-терминал для последовательного порта (например Tera Term). Из-за того, что в Tera Term распознается три различных COM порта, мы открыли три разных сессии Tera Term. Скорость UART, в который будут сыпаться сообщения, имеет скорость 9600 (проверьте настройки IP uartlite в тестовом проекте)

Запуск и отладка

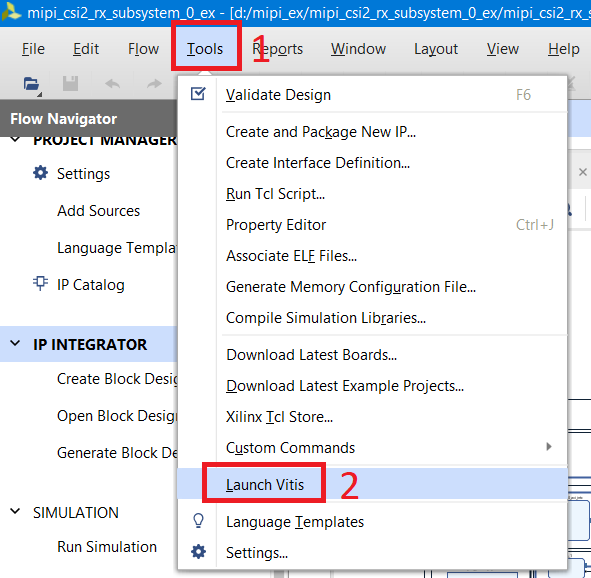

29. Запустите VITIS из Vivado. Нажмите «Tools» (1) :: Нажмите «Launch VITIS» (2)

30. Укажите рабочую директорию (workspace). Она расположена внутри директории тестового проекта «mipi_ex :: mipi_csi2_rx_subsystem_0_ex :: SW :: xmipi_app» (1) в нашем случае :: Нажмите «Launch» (2)

31. Закройте вкладку «Welcome» в VITIS

32. Теперь нам доступна программная составляющая нашего проекта, т.е. программа для софт-процессора MicroBlaze. Изучите код при желании.

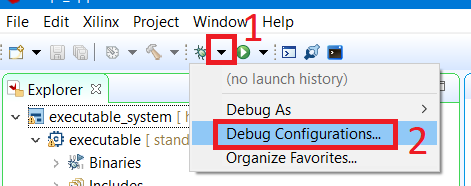

33. Нажмите стрелочку рядом со значком жучка (1) :: Нажмите «Debug Configurations» (2)

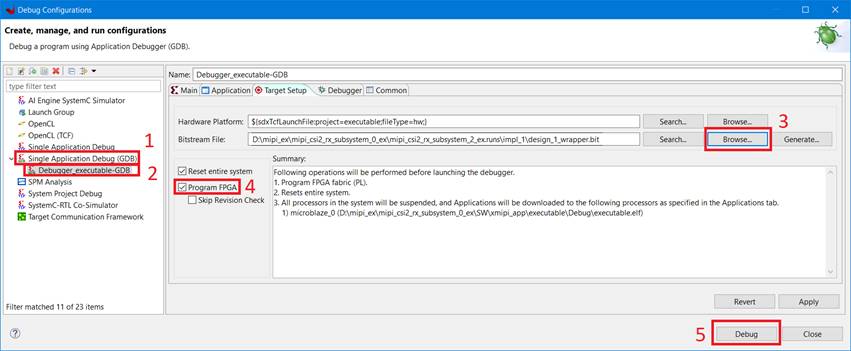

34. Дважды кликните по «Single Application Debug (GDB)» (1) :: Выберите «Debugger Executable» (2) :: Укажите файл прошивки ПЛИС (.bit), созданный Vivado (3) :: Установите галку (4) :: Нажмите «Debug» (5)

35. Нажмите кнопку запуска и следуйте инструкциям, появившемся в терминале Tera Term

36. На этом всё (не забудьте снять защитный колпачок с камеры ;)

Заключение

Как мы убедились, создать тестовый проект c MIPI интерфейсом достаточно просто. Потребовался только VITIS/Vivado и наличие соответствующих аппаратных средств (платы и камеры). Практически все IP ядра от Xilinx имеют возможность сгенерировать тестовый проект и в этой статье мы продемонстрировали, как это сделать.