Часы на ПЛИС Lattice

19 мин

Некоторое время назад, хаброжитель DmitrySpb79 написал статьи о создании электронных часов. В них он рассмотрел источники точного времени, а так-же элементную базу для создания электронных часов. Были упомянуты Arduino, STM, Raspberry PI, ESP8266, но совсем забыли про ПЛИС.

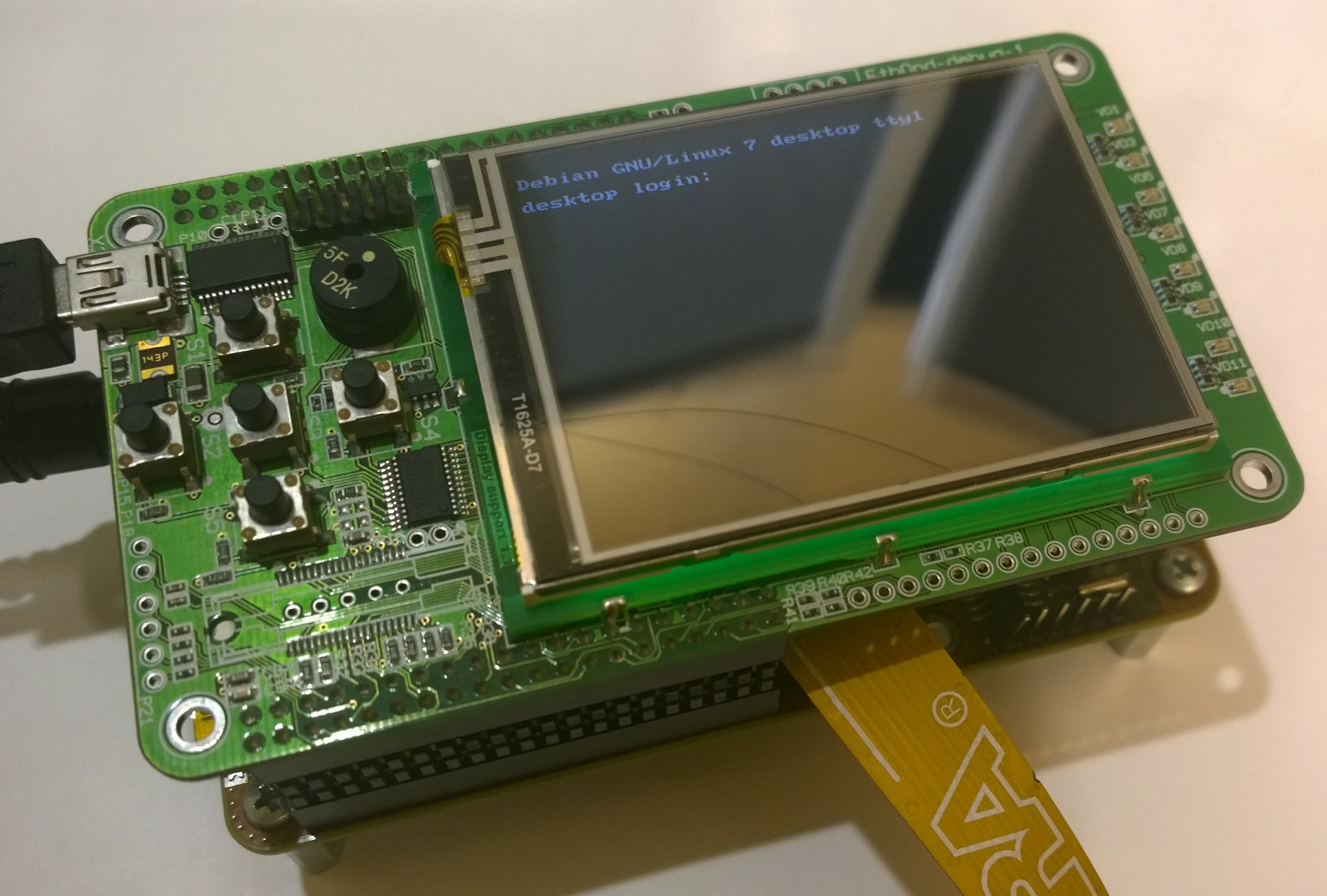

Некоторое время назад, хаброжитель DmitrySpb79 написал статьи о создании электронных часов. В них он рассмотрел источники точного времени, а так-же элементную базу для создания электронных часов. Были упомянуты Arduino, STM, Raspberry PI, ESP8266, но совсем забыли про ПЛИС. Давайте заполним этот небольшой пробел. Узнаем, на сколько просто сделать часы на ПЛИС и какие аппаратные ресурсы для этого потребуются. К тому же, мне подарили микросхему ПЛИС очень малого объема — 64 макроячейки. Это ПЛИС LC4064v фирмы Lattice с которыми я до этого никогда не работал. Я думаю, будет интересно!

Цели:

- попытаться уместить логику работы часов в ПЛИС малого размера (64 макроячейки);

- освоить статическую либо динамическую светодиодную индикацию на ПЛИС для вывода времени;

- собрать кучу граблей, связанных с самостоятельной разработкой схем и получить новый опыт;

- освоить новую среду разработки и программирования для ПЛИС фирмы Lattice, оценить сложность перехода

Меня ожидает несколько очень приятных вечеров, посвященных разработке на ПЛИС!