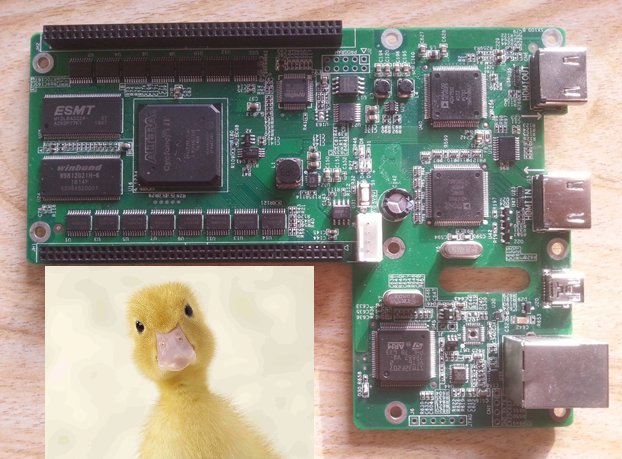

Полигон для творчества за 1500 р. Ч1: Позовите Кряка

Приветствую вас, друзья! Не знаю как вам, а мне нравится разбирать всякие штучки, узнавать, как они работают, и применять их в своих проектах. По ходу дела начинается настоящее увлекательнейшее расследование, технический детектив.

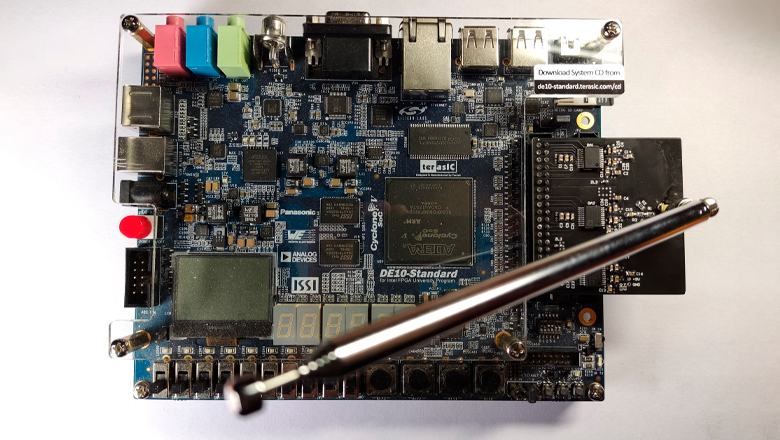

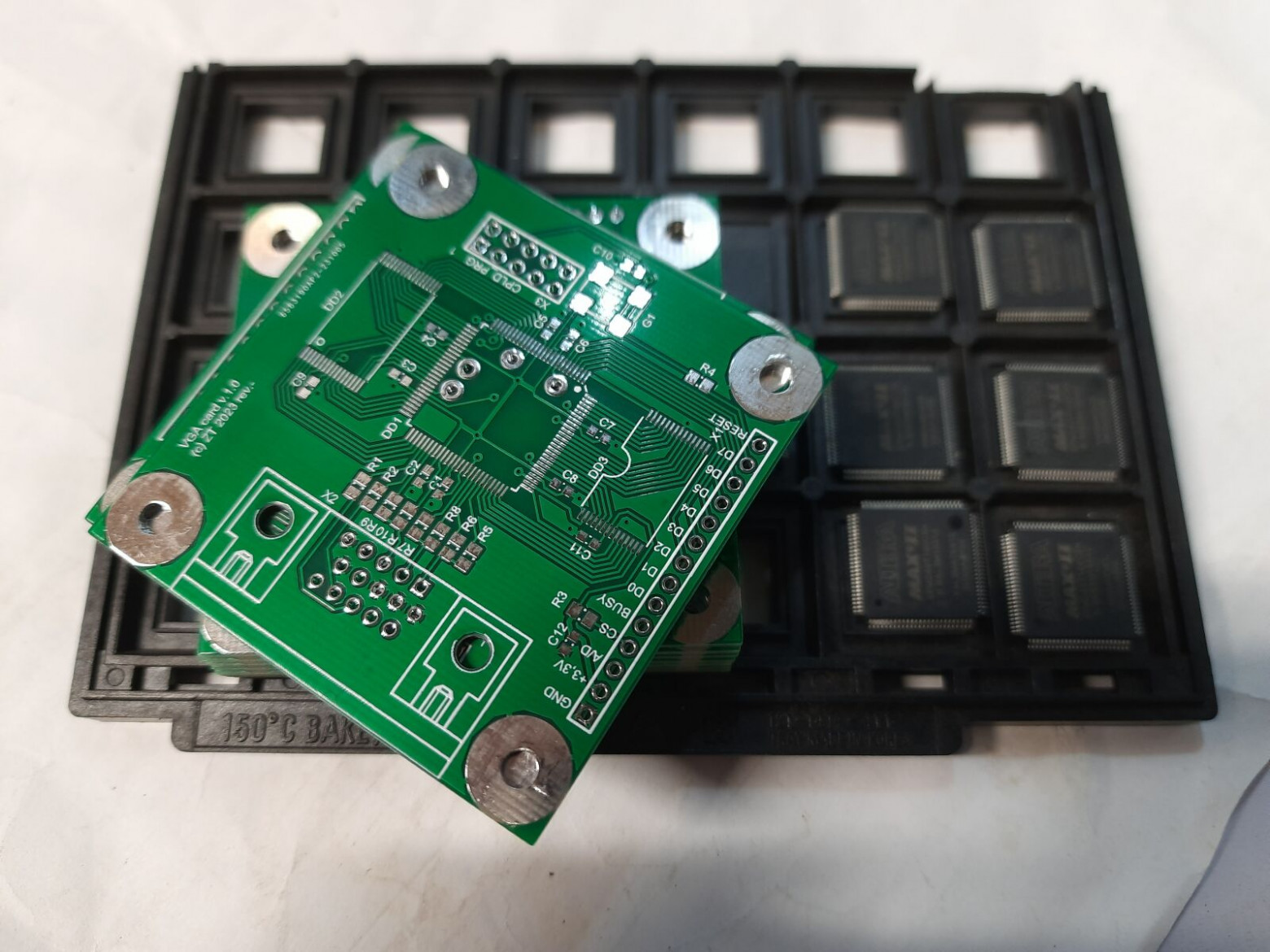

На этот раз меня заинтересовала плата с разными микросхемами, которые могут пригодиться во многих затеях. А может из неё вообще получится удобная отладка? В любом случае, это очень интересно. Это тот самый творческий процесс, приносящий радость и заметно повышающий наши навыки и умения. А ведь они часто самое ценное, что дал проект и работа над ним.

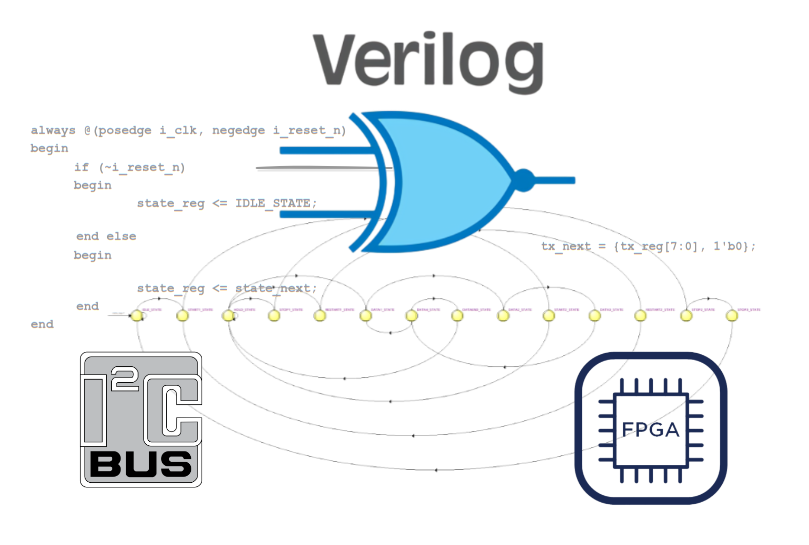

Проведём расследование, поищем JTAG, узнаем способы и отследим разводку BGA, поработаем с ПЛИС, … и много других действительно интересных вещей. Кряк уже заинтересовался!

Как там у нас обычно? «Сломать, а потом читать инструкцию». Инструкций и документации нет, поэтому будем экспериментировать