В этой статье мы поделимся практическим опытом в использовании периферийного (граничного) сканирования JTAG и расскажем про особенности и преимущества внедрения этой технологии на этапе тестирования опытных образцов. Особое внимание будет уделено типичным ошибкам, выявленным с помощью JTAG с использованием программного пакета Provision для тестирования различных узлов и микросхем платы.

Напомним, что периферийное сканирование (boundary scan) — это структурное тестирование печатной платы с установленными компонентами, которое основано на применении стандартов IEEE 1149.x. Результат сканирования — информация о наличии в электроцепях типичных неисправностей, возникающих в процессе производства печатных плат: коротких замыканий (bridges), непропаек (opens), западаний на 0 или 1 (stuck at 0, stuck at 1), обрывов дорожек.

JTAG-тестирование выполнятся на плате, которая пришла с производства.

JTAG-тестирование позволяет выявить непропай в BGA-корпусах, замыкания, обрывы, а так же нерабочие микросхемы с цифровыми интерфейсами. Выявить данные дефекты очень важно, так как если непроверенная плата попадает в руки программисту, начинаются проблемы с запуском памяти и прочей периферии. Часто непонятно, в чем причина: в неверных настройках, которые делает программист, или в дефекте монтажа. JTAG-тестирование способно выявить данные проблемы.

На этапе тестирования (перед первым включением) проверяется отсутствие короткого замыкания на платах. Далее подается напряжение питания и проверяется ток потребления, после этого проверяются основные питающие напряжения. Затем плата подвергается либо JTAG либо внутрисхемному (ICT) тестированию (как вариант — можно использовать два теста по очереди).

Так как JTAG — это самый первый тест, то выявленные им проблемы экономят трудозатраты в дальнейшем. Логично, что если проблемы будут обнаружены после сборки устройства, его придется разбирать и собирать заново.

На этапе JTAG-тестирования выявляется:

- непропай у микросхем с корпусами BGA, для которых реализовать ICT-тестирование не возможно в принципе;

- незапаянные резисторы pull-up/down;

- межвыводные КЗ.

Также с помощью технологии JTAG успешно проверяются микросхемы памяти: от SRAM до DDR3 (анализируется только правильность монтажа цепей, не сама память). Этот тест в совокупности с тестом flash-памяти позволяет отдать плату программисту для установки начального загрузчика, ОС и последующего брингапа (первого запуска).

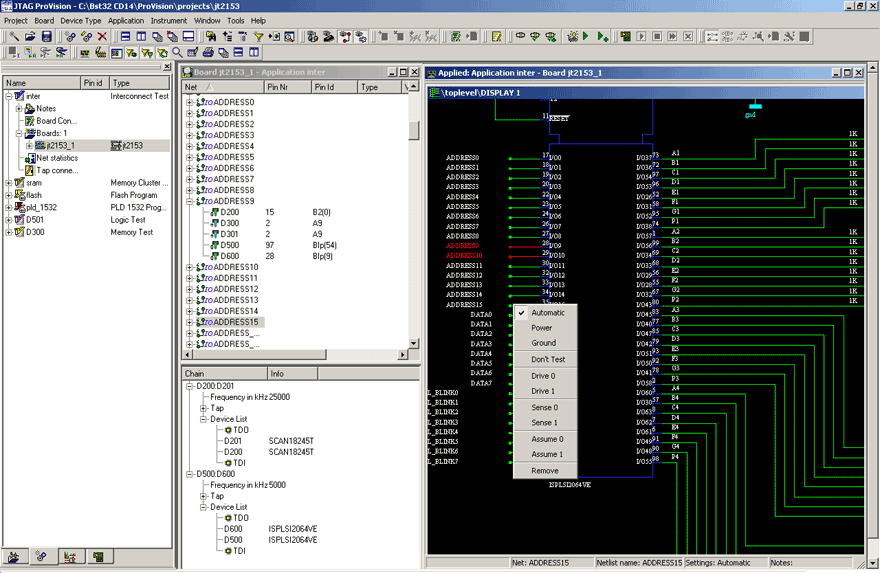

Использование тестов JTAG на примере ПО Provision для функционального тестирования печатных плат

Программный пакет Provision для проведения JTAG тестирования позволяет генерировать автоматические тесты, включает в себя обширную библиотеку моделей для тестирования микросхем, отличается хорошей тех. поддержкой и дружественным интерфейсом.

Мы использовали Provision для проведения тестирования в проектах с миниатюрной элементной базой, корпусами 0402 и BGA, высокой плотностью компоновки, платами более 4 слоев и гибко-жёсткими платами.

Рассмотрим применение технологи граничного сканирования на конкретных проектах:

Пример №1. VoIP-маршрутизатор

Задача: разработать устройство для VoIP-телефонии на базе процессора Blackfin BF527 с программным обеспечением на базе OC Linux.

В данном проекте тестировались микросхемы SDRAM, NAND, Ethernet switch. Также посредством JTAG была проверена корректность работы светодиодов и кнопок — для этого использовались функциональные тесты, написанные на языке Python. Это скриптовый язык, интегрированный в Provision. С его помощью можно тестировать различные цифровые интерфейсы и микросхемы, а также организовать гибкий диалог с пользователем.

Применение JTAG-тестирования позволило проверить корректность монтажа и работоспособность микросхем.

Пример №2. Plug-компьютер

Задача: разработать многофункциональное сетевое устройство (мини-сервер), предназначенное для работы в IP-сетях.

В данном проекте использовался процессор 88F6282 фирмы Marvell и память DDR2/DDR3. На плате ограниченных размеров применён двухсторонний монтаж и 7 микросхем с BGA-корпусами. В ходе подъема плат возникли проблемы с памятью, они проявлялось в виде зависаний плат во время загрузки или невозможности запуска U-boot. Были проведены оперативные тесты DDR2-памяти, которые выявили неприпаянные выводы на шине данных на линиях D0, D3, D7 одного из 4-х чипов памяти. Из-за этого дефекта данные в определённом адресном пространстве самопроизвольно менялись.

В версиях устройства с DDR3-памятью у программистов возникли проблемы с загрузкой ОС Linux. Было принято решение оперативно проверить качество монтажа данных чипов. В результате тестирования выяснилось, что все чипы исправные, а проблема крылась в неверно установленных таймингах.

В результате JTAG-тестирование помогло сэкономить значительное время на этапе брингапа, так как передавая платы программистам можно было с уверенностью сказать, что память запаяна верно.

В ходе данного проекта была оценена оперативность технической поддержки у JTAG Technologies.

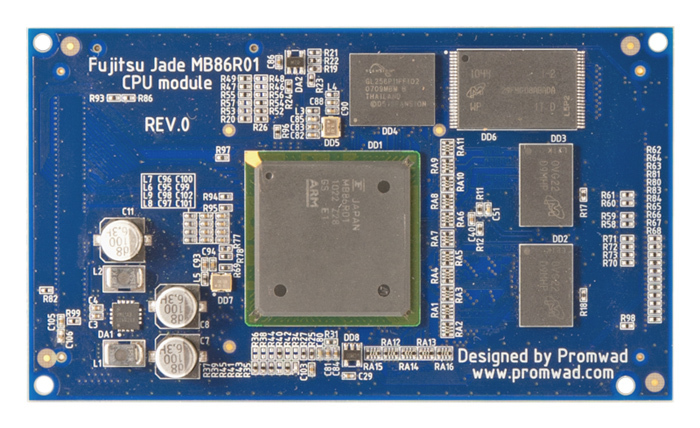

Пример №3. Процессорный модуль JADE на чипе Fujitsu JADE

Задача: разработать бортовой компьютер для управления, контроля и диагностики вспомогательного оборудования грузовых автомобилей и спецтранспорта.

Данный проект — двухплатный — процессорный модуль и материнская плата (на фото — только сам модуль). Акцент был сделан на тестировании связей между платами, также была проведена проверка наличия генерации у генераторов, корректность монтажа NAND и NOR памяти.

Во время проверки опытных образцов устройства было выявлено отсутствие генерации на одном из выводов. При визуальном осмотре обнаружилось, что при монтаже перепутали ключ на генераторе.

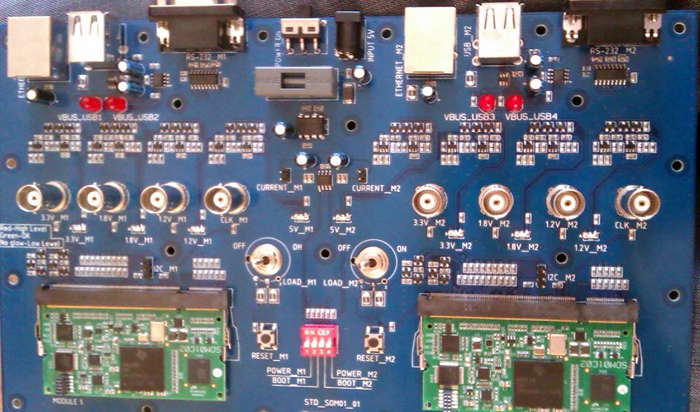

Пример №4. Одноплатный промышленный компьютер

Задача: разработка процессорной платы SOM01 на базе процессора TI AM1808 (ARM926, 456MHz).

Данное устройство представляет собой одноплатный компьютер, реализованный в форм-факторе SO-DIMM 200. Во время реализации данного проекта был сделан подробнейший DFT-анализ, определено покрытие и даны рекомендации по шагам для увеличения тестового покрытия. Для максимального покрытия платы JTAG-тестами был спроектирован стенд, который увеличивал покрытие до 98% (непокрытым оказался только интерфейс USB, так как TAP-контроллер не имеет доступа к этим выводам). Также данный стенд позволиляет прошить плату по Uart или Ethernet, контролировать напряжения и токи.

На фото: тестовый стенд с подключенными платами

Выводы

Технология пограничного сканирования JTAG может успешно применяться на производстве для контроля правильности монтажа, для проверки опытных образцов, на производстве серии.

Для внедрения данной технологии на производство необходимо приобрести пакет программного обеспечения и аппаратный адаптер. А для тестирования конкретной платы необходим набор скриптов, написанных в этой среде.

Преимущества JTAG-тестирования перед ICT-тестированием заключается в том, что нет необходимости в размещении дополнительных контактных площадок для ICT-тестера (более подробно об этом мы уже писали в статье «Как тестировать электронику на производстве: анализ современных технологий»).

Также с помощью JTAG тестирования можно тестировать правильность монтажа BGA-корпусов, что невозможно при внутрисхемном тестирования.

В результате технология JTAG позволяет значительно уменьшить время брингапа опытных образцов. Разработчик самостоятельно устройства пишет тесты на скриптовом языке, учитывая все нюансы работы каждой конкретной схемы.

Спасибо за внимание. Вопросы и комментарии приветствуются.