В данной статье будут описаны установка и применение бесплатного ПО для моделирования схем цифровой логики на языке Verilog как альтернативы коммерческих продуктов Incisve от компании Cadense и ModelSim от компании MentorGraphics. Сравнение моделирования в ModelSim и Verilator. Так же будет рассмотрена универсальная методолгия верификации — UVM.

Установка ПО для SystemC UVM

1. Верилятор

Одним из языков описания аппаратуры является verilog. На этом языке можно написать модуль.

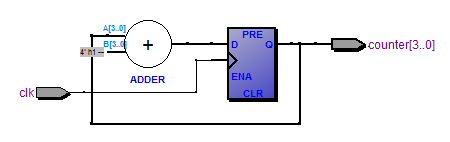

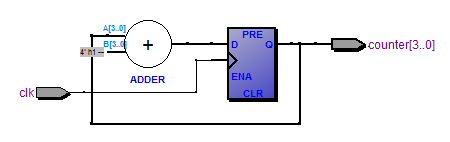

Например, есть схема счетика:

Его код будет выглядеть так:

reg [3:0]counter;

always @(posedge clk or posedge reset)

if(reset)

counter <= 4'd0;

else

counter <= counter + 1'd1;

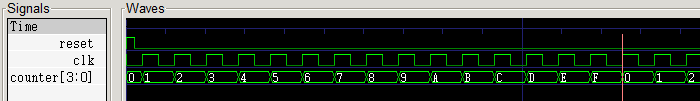

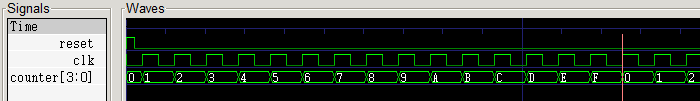

После симуляции получим вейвформы:

Видно, что по фронту тактовой частоты в регистры счетчика будет записываться очередное значение, на единицу большее, чем предыдущее.

Написанный модуль может иметь и более сложную структуру, проверить все состояния которого вручную будет сложно. Нам понадобится автоматизированное тестирование. Для этого необходимо разработать тестовое окружение на одном из языков программирования. Тестовое окружение даст нам возможность провести полную функциональную проверку устройства.

Для тестирование кода проекта помимо таких языков как Verilog, SystemVerilog, Python (для написания моделей), можно использовать язык

SystemC. SystemC — язык проектирования и верификации моделей системного уровня, реализованный в виде C++ библиотеки с открытым исходным кодом.

Один из способов верификации Verilog модулей с помощью SystemC является трансляция verilog файлов в С++. Поможет нам в этом Verilator.

Verilator — это самый быстрый бесплатный симулятор Verilog HDL, который превосходит большинство коммерческих симуляторов. Verilator компилирует синтезируемый SystemVerilog (обычно это не код тестового стенда), а также некоторые утверждения SystemVerilog и Synthesis в однопоточный или многопоточный код C ++ или SystemC. Verilator был разработан для больших проектов, где быстродействие симуляции имеет первостепенное значение, и особенно хорошо подходит для генерации исполняемых моделей процессоров для групп разработчиков встроенного программного обеспечения. Verilator используется для имитации многих очень больших многомиллионных конструкций шлюзов с тысячами модулей и поддерживается многими поставщиками IP-технологий, включая IP от Arm и всех известных поставщиков RISC-V IP.