FPGA *

Программируемые логические интегральные схемы

MIPSfpga и SDRAM. Часть 2

Ссылка на первую часть

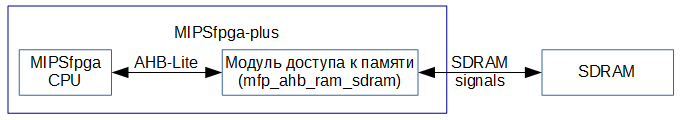

Рассматриваемая нами конфигурация состоит из следующих элементов:

Шина AHB-Lite

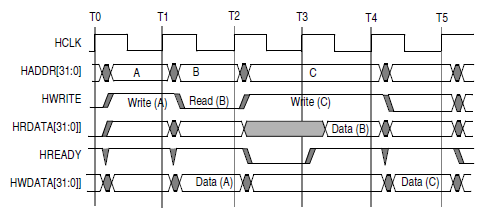

Является основным инструментом для общения ядра MIPSfpga с внешним миром. Из нее в модуль доступа к SDRAM поступают команды на чтение и запись информации, по ней же передаются считываемые и записываемые данные. Основная особенность: фаза адреса последующей команды совпадает по времени с фазой данных текущей команды. Лучше всего это видно на следующей диаграмме:

Краткое описание изображенных сигналов: HCLK — тактовый сигнал; HADDR — адрес, данные по которому мы хотим записать или прочитать на следующей фазе, задается мастером; HWRITE — при высоком уровне на следующей фазе должна быть произведена операция записи, выставляется мастером; HRDATA — прочитанные данные; HREADY — флаг завершения текущей операции; HWDATA — записываемые данные, выставляются мастером. Документация на шину, включая описание всех сигналов и их возможных комбинаций входит в состав пакета MIPSfpga.

MIPSfpga и SDRAM. Часть 1

На этой неделе я закончил работу по добавлению поддержки SDRAM в проект MIPSfpga-plus. Теперь при работе с MIPSFpga помимо блочной памяти, ограниченной ресурсами ПЛИС, доступно еще и внешнее ОЗУ.

Данная статья состоит из 2 частей:

Часть 1. Краткое описание модуля доступа к SDRAM. Пример использования.

Часть 2. Подробное описание работы с памятью, достаточное для того, чтобы в работе модуля смог разобраться человек, ранее не имевший дела с микросхемами ОЗУ. Список литературы.

Предполагается, что читатель как минимум:

- знаком с предметной областью в объеме учебника Харрис-энд-Харрис [1];

- имеет опыт программирования на C, ассемблере, использования gcc;

- имеет минимальный опыт работы с MIPSfpga. Не имея такого опыта, будет логичным начать с более простых вещей, и лишь затем думать о том, как использовать ОЗУ в своей системе.

Если вы уже опытный разработчик, то Часть 1 стоит пробежать глазами по диагонали, Часть 2 — не содержит для вас ничего нового. При этом вы можете принести несомненную пользу обществу, если добавите поддержку SDRAM для еще одной отладочной платы. На текущий момент она реализована только для Terasic DE10-Lite — одной из 9 плат, на которые в рамках проекта MIPSfpga-plus было портировано ядро MIPSfpga.

Верификация конечного автомата

Вообще в основе публикации лежит мой курсовой проект, который был оценен моим преподавателем по достоинству с предложением сделать публикацию на Хабре.

Основное на чем я хочу акцентировать внимание — это описания типичных блоков multilayer testbench и применение некоторых базовых конструкции языка SystemVerilog и верификации. В основе подхода, который я использовал лежит так называемая Open Verification Methodology (OVM) с изменениями, которые упрощали разработку проекта и были удобны персонально мне.

Итак, поехали!

Написание и запуск скрипта для симуляции Verilog-кода в ModelSim

Всем привет! Надеюсь, все хорошо провели праздники и готовы с новыми силами покорять высоты FPGA разработки.

Сегодня я хочу написать небольшой гайд по запуску тестбенчей на Verilog/SystemVerilog в ModelSim без использования GUI.

План будет такой:

- Добавление пути к ModelSim в PATH.

- Написание скрипта с объяснением команд.

- Запуск ModelSim с исполнением написанного скрипта.

Поехали!

Отладочная плата ПЛИС — Франкенштейн. Контроллер елочных гирлянд

Очередная серия про ПЛИС и отладочную плату Френки. Предыдущие серии 1, 2, 3.

Сделать контроллер елочных гирлянд не просто, а очень просто! Hello World на ПЛИС — это помигать светодиодом. А "С новым годом" на ПЛИС — это помигать несколькими светодиодами. Принцип прост, как и в предыдущих статьях: создаем счетчик, который делит частоту тактового генератора, выбираем биты из слова счетчика, для получения нужной скорости. Несколько бит из этого слова дадут нам определенный шаг отображения (в зависимости от количества выбранных бит 1, 2, 4, 8 и т.д. шагов). В зависимости от номера шага задаем значения для N светодиодов.

Сделать контроллер елочных гирлянд не просто, а очень просто! Hello World на ПЛИС — это помигать светодиодом. А "С новым годом" на ПЛИС — это помигать несколькими светодиодами. Принцип прост, как и в предыдущих статьях: создаем счетчик, который делит частоту тактового генератора, выбираем биты из слова счетчика, для получения нужной скорости. Несколько бит из этого слова дадут нам определенный шаг отображения (в зависимости от количества выбранных бит 1, 2, 4, 8 и т.д. шагов). В зависимости от номера шага задаем значения для N светодиодов.

Для управления реальной гирляндой, можно взять какой-нибудь shield с электромагнитным реле. У меня оказался вот такой, на 8 реле. Схема подключения. Принципиальная схема.

Отладочная плата ПЛИС — Франкенштейн. Звуки и музыка

Сегодня у нас самая предновогодняя серия про ПЛИС и отладочную плату Френки. Предыдущие серии 1, 2.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

Для этого подключим к ПЛИС обычный динамик. К Френки подключен генератор на 25.175 МГц. Если поделить эту частоту до диапазона слышимых частот и подать на вывод ПЛИС, то мы можем услышать звук. Меня частоту мы можем получить разные звуки.

Тестировать качество звучания будет самый лучший слухач в доме — Маша. Диапазон частот в 60 КГц — это вам не шутки! )))

Отладочная плата ПЛИС — Франкенштейн. Часы. Altera EPM7064 VS Lattice LC4064v

Продолжение предновогодней серии приключений маленькой ПЛИС Altera EPM7064 на отладочной плате — Франкенштейн. В предыдущей серии...

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

Как нам их сравнить? Попробуем решить на них одну и ту же задачу. Часы на Lattice LC4064v мы уже попробовали сделать и у нас получилось. Теперь попробуем сделать часы на Altera EPM7064 — на нашем Франкенштейне.

Отладочная плата ПЛИС — Франкенштейн. Телеграфный передатчик

Недавно мне потребовалось найти пару 1U корпусов под мой проект. И в качестве альтернативы новым, мы решили поискать старые приборы в 1U формате, внутренности выкинуть, а корпус использовать по назначению. Но, открыв корпус, я был приятно удивлен! Целых четыре ПЛИС от Altera, да к тому же 5 вольтовых. Я не смог удержаться, чтобы одну из них не попробовать в деле!

Паяльной станции у меня нет, ЛУТ технологию я не практикую. Поэтому я взял строительный фен на 250 градусов и отковырял микросхему ПЛИС от платы. Переходной платы для такого корпуса у меня тоже не было, поэтому я взял обычную макетку, впаял в нее стойки и с помощью накрутки и пайки, соединил выводы микросхемы со стойками. Вывел разъем JTAG и питания, прикрутил генератор. Это все, что нужно для начала работы с микросхемой

Что можно сделать из такой маленькой ПЛИС? Радиолюбители решают такую проблему очень просто: в любой непонятной ситуации мы делаем передатчики! Из чего? Да из чего угодно, что под руку попало в данный момент! А сегодня у нас Altera EPM7064.

Можно ли вычислять биткоины быстрее, проще или легче?

Все началось с того, что я решил поближе познакомиться с биткоинами. Хотелось понять, как их добывают. Статьи про биткоины и блокчейны последнее время встречаются часто, но таких, чтобы со всеми техническими подробностями, таких не очень много.

Самый простой способ разобраться во всех деталях — изучить открытые исходники. Я взялся изучать Verilog исходники FPGA-майнера. Это не единственный такой проект, есть еще несколько примеров на github, и все они, хоть и разных авторов, похоже работают приблизительно по одной схеме. Вполне возможно, что автор то у них всех изначально был один, просто разные разработчики адаптируют один и тот же код под разные чипы и разные платы… По крайней мере мне так показалось…

Вот и я, поизучав исходники Verilog, адаптировал проект с github к плате Марсоход3 на основе ПЛИС Altera MAX10, 50 тыс. логических элементов. Я смог запустить свой майнер и даже смог запустить процесс вычисления биткоинов, но бросил это дело через пол часа из-за бесперспективности. Слишком медленно по нынешним временам работает мой FPGA майнер. Ну и пусть.

Честно говоря, меня во всем этом проекте заинтересовали не сами биткоины (ну их, эти денежные суррогаты), но скорее математическая сторона алгоритма SHA256. Вот об этом я и хотел бы поговорить. Я провел несколько экспериментов с алгоритмом SHA256, может быть результаты этих экспериментов покажутся вам интересными.

Избранные места из популярного учебника микроэлектроники на русском, который наконец-то выходит на бумаге

При этом, электронное издание Харрис-энд-Харрис сформатировано для планшета, и уже после первых скачиваний посыпались емейлы, когда же учебник будет и на бумаге. И вот час настал — Учебник Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера» можно заказать на бумаге (выходит в новогоднюю ночь). В этом посте я покажу, чем этот учебник отличается от других. Бонус: фотки участников и участниц проекта!

Есть много учебников, которые хорошо вводят в цифровую логику на уровне триггеров и мультиплексоров, или в программирование готовых микроконтроллеров на ассемблере, или показывают красивые диаграммы процессорных конвейеров, или обучают синтаксису Verilog или VHDL. Но если учить скажем микроархитектуре без HDL, или если например пропускать уровни между триггером и программированием микроконтроллера, то получатся студенты, которые могут сдать экзамен и спорить умными словами в интернете, но ничего не могут сделать практически.

Учебник H&H решает эту проблему:

О метастабильности в электронике

Функциональные языки в разработке аппаратуры

Функциональные языки, как правило, не слишком подходят для низкоуровнеого программирования, хотя и применяются для кодогенерации.

Функциональные языки, как правило, не слишком подходят для низкоуровнеого программирования, хотя и применяются для кодогенерации. Но если спуститься еще ниже, на уровень аппаратуры, то неожиданно ФП оказывается очень кстати. Ведь блок комбитаторной логики не что иное, как функция из величин входящих сигналов в величины исходящих, а для последовательной логики достаточно добавить в параметры и результат старое и новое состояние.

Ближайшие события

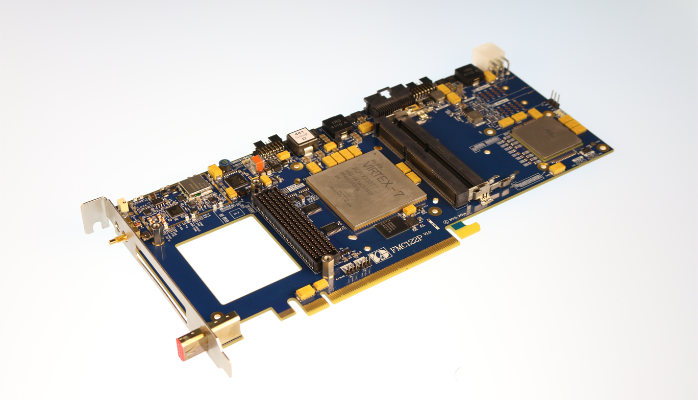

Реализация PCI Express v3.0 x16 на ПЛИС Virtex 7

В компьютерах уже давно есть шина PCI Express v3.0 x16; Тесты современных видеоадаптеров показывают на этой шине скорость около 12 Гбайт/с. Хотелось бы сделать модуль на ПЛИС который обладает такой же скоростью. Однако доступные ПЛИС имеют HARDWARE контроллер только для PCIe v3.0 x8; Реализации SOFT IP Core есть, но очень дорогие. Но выход есть.

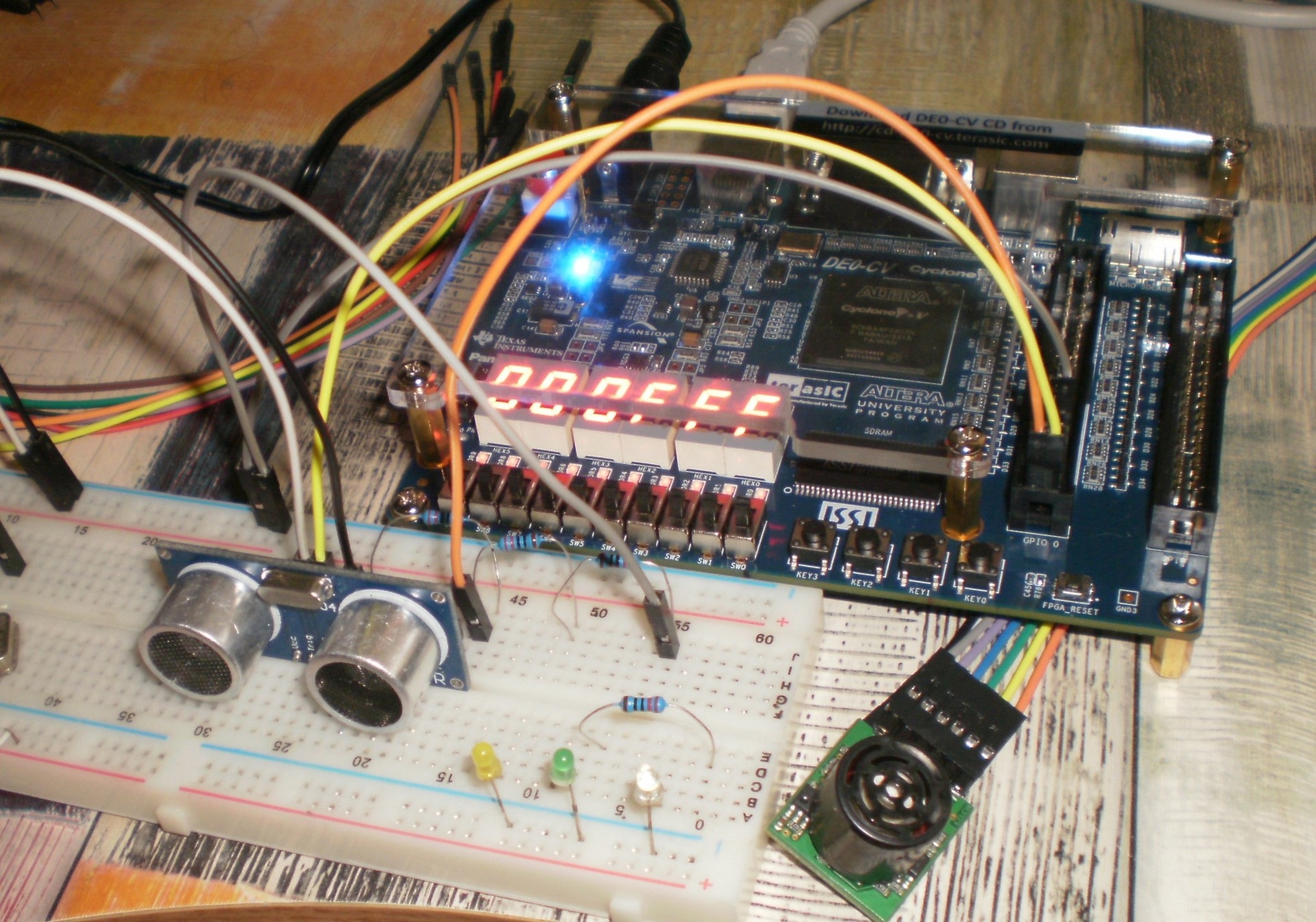

Подключение периферийных модулей к MIPSfpga, на примере ультразвуковых датчиков расстояния

Основываясь на моем примере вы сможете подключить ваши собственные модули, управлять ими при помощи программы. Создавать систему со своим набором периферии, на основе MIPSfpga.

Собственная платформа. Часть 0.1 Теория. Немного о процессорах

Здравствуй, мир! Сегодня у нас серия статьей для людей со средними знаниями о работе процессора в которой мы будем разбираться с процессорными архитектурами (у меня спелл чекер ругается на слово Архитектурами/Архитектур, надеюсь я пишу слово правильно), создавать собственную архитектуру процессора и многое другое.

Принимаются любые замечания!

Применение FPGA для расчета деполимеризации микротрубочки методом броуновской динамики

Все готово, чтобы рассказать Хабр аудитории о применении FPGA в сфере научных высокопроизводительных вычислений. И о том, как на данной задаче надо удалось значительно обскакать GPU (Nvidia K40) не только в метрике производительность на ватт, но и просто с точки зрения скорости вычисления. В качестве FPGA платформы использовался кристалл Xilinx Virtex-7 2000t, подключенный по PCIe к хост компьютеру. Для создания аппаратного вычислительного ядра использовался язык C++ (Vivado HLS).

Под катом текст нашей оригинальной статьи. Там, как обычно бывает, сначала идет долгое описание зачем это все надо и модели, если нет желания это читать, то можно переходить сразу к реализации, а модель посмотреть потом при необходимости. С другой стороны без хотя бы беглого ознакомления с моделью читатель не сможет получить впечатление о том, какие сложные вычисления можно реализовать на FPGA.

Знакомство и старт разработки на ПЛИС iCE40 от Lattice Semiconductor

Здравствуйте! Сегодня мы познакомимся с новым семейством дешевых и малопотребляющих ПЛИС от Lattice Semiconductor семейств iCE40LP/HX/LM, научимся работать с фирменным компилятором iCEcube2 и редактором кода Sublime Text 3, а также программировать чип на отладочной плате Lattice iCEstick с помощью прошивки, написанной на SystemVerilog.

Здравствуйте! Сегодня мы познакомимся с новым семейством дешевых и малопотребляющих ПЛИС от Lattice Semiconductor семейств iCE40LP/HX/LM, научимся работать с фирменным компилятором iCEcube2 и редактором кода Sublime Text 3, а также программировать чип на отладочной плате Lattice iCEstick с помощью прошивки, написанной на SystemVerilog. Все будет сопровождаться подробными инструкциями и скриншотами.

Наконец-то приличный отечественный процессор ЦОС – 1967BH28

Несмотря на стремительное развитие процессоров общего назначения (ARM, x86 и более экзотических), не теряют своей актуальности специализированные процессоры цифровой обработки сигналов (ЦОС). Одним из самых популярных процессоров ЦОС с плавающей точкой в родном отечестве стал процессор ADSP-TS201S фирмы Analog Devices. В свое время (10-15 лет назад) этот процессор не знал себе равных в высокопроизводительных системах ЦОС, работающих в реальном времени. Его основные характеристики:

- Частота процессора – 600 MГц

- Объем внутренней памяти – 3 МБайта

- 4 высокоскоростных порта – 600 Мбайт/сек

- Внешняя шина – 100 МГц

- Каналы DMA – 12 каналов

Решения на процессоре ADSP-TS201S хорошо себя зарекомендовали в широком классе аппаратуры как гражданского, так и не очень гражданского назначения. Но всему хорошему приходит

Можно скачать материалы семинара Nanometer ASIC (РОСНАНО / МИСиС / Imagination Technologies) — ликбез по всему про чипы

Несмотря на то, что для профессиональных спецов по использованию Synopsys IC Compiler семинар был слишком элементарный, но его вводный характер искупился его широтой — инженеры из всей цепочки проектирования и производства могли освежить в памяти области, которые они забыли, инвесторы в полупроводниковой индустрии смогли посмотреть что делают компании, в которые они инвестируют, студенты посмотрели, что им может нравится и так сказать куда копать (в полупроводниковой индустрии Silicon Valley молодые инженеры специализируются в логический / физический / аналоговый дизайн довольно рано в своей карьере).

Ведущий семинара, лектор Калифорнийского университета в Санта-Крус (отделение в Кремниевой долине) Чарльз Данчек (Charles Dancak) отвечает на вопросы:

Скачать все слайды на русском можно здесь.

Под катом — избранные слайды Nanometer ASIC (25 из 322):

Вклад авторов

YuriPanchul 3066.1andreyzaostrovnykh 923.0KeisN13 743.5nckma 626.0hukenovs 429.0Armleo 421.3ishevchuk 419.0yadro_team 371.0iliasam 283.0BarsMonster 281.0