Хардвер вторгается в софтвер на московской конференции SECR

3 мин

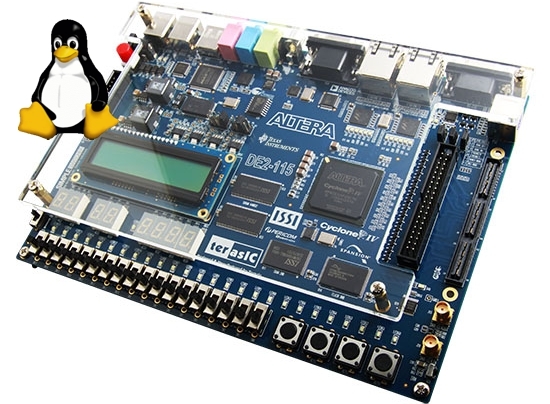

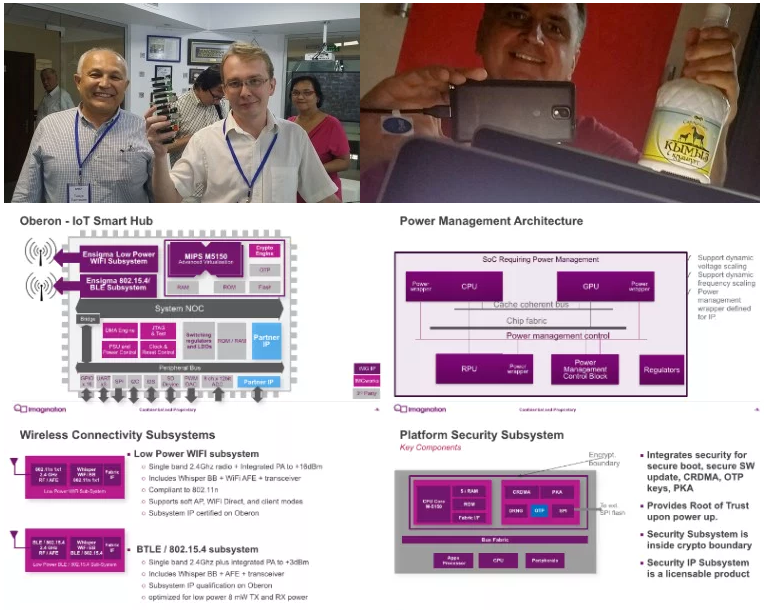

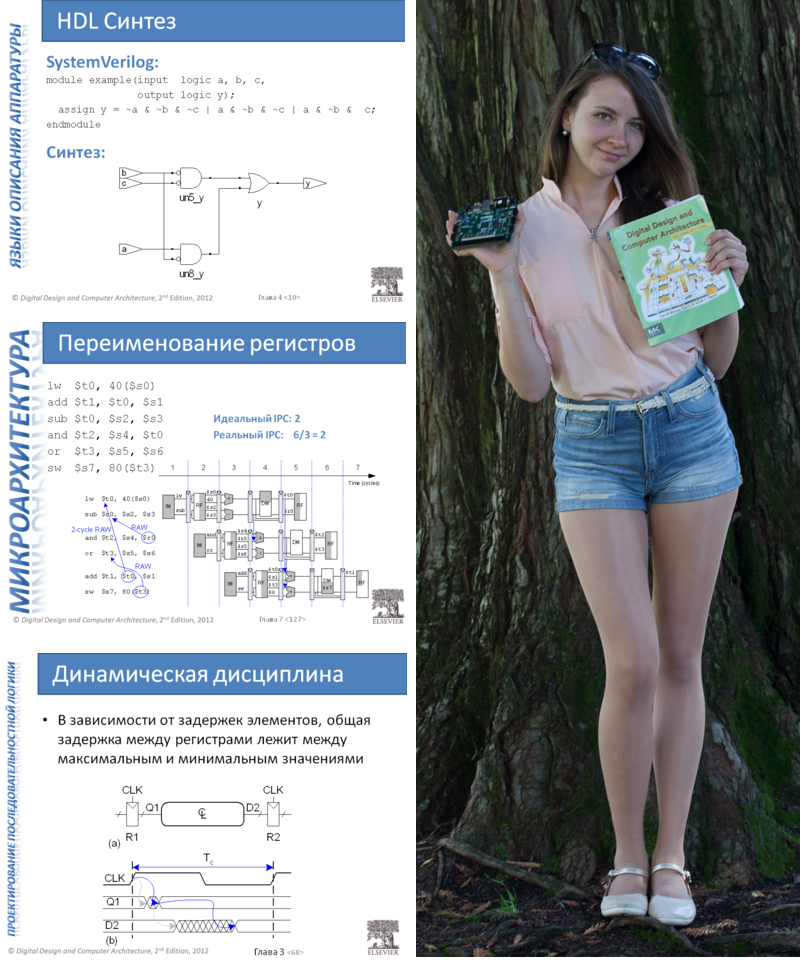

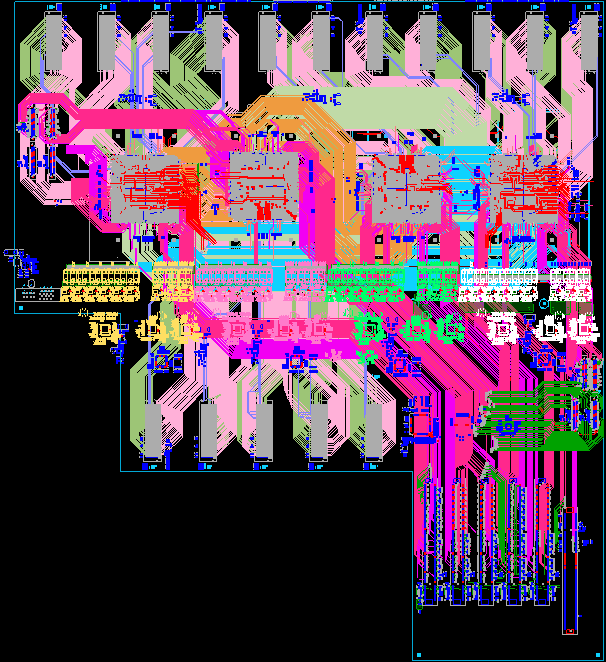

Традиционно московская конференция CEE-SECR (Central & Eastern European Software Engineering Conference in Russia) была про софтвер, но в этом году ее организаторы решили поэкспериментировать и впустить темных демонов хардвера. Причем не из чего-то народного типа Ардуино, а из уровней посуровее: микроархитектуры микропроцессоров, прототипирования систем на кристалле с помощью микросхем ПЛИС/FPGA, и автоматической генерации тестов для процессоров во время их разработки. Чтобы привязать данный материал к чему-то знакомому для программистов, в хардверной теме возникли приложения встроенных процессоров для интернета вещей, связь лицензируемых микропроцессорных ядер с российскими микропроцессорными проектами, обучение хардверу в российских университетах, а также российские встроенные операционные системы реального времени для тех применений, куда нельзя впускать длинный нос американского Госдепа.

Можно сказать, что хардверная тема на SECR-е удалась: вся комбинация докладов была сбалансированна и покрывала тему с разных сторон; людей в зале было не то что особенно много, но выше среднего; возникли интересные споры о достоинствах и недостатках открытых процессорных ядер супротив частично открытых, но шире используемых в промышленности.

Можно сказать, что хардверная тема на SECR-е удалась: вся комбинация докладов была сбалансированна и покрывала тему с разных сторон; людей в зале было не то что особенно много, но выше среднего; возникли интересные споры о достоинствах и недостатках открытых процессорных ядер супротив частично открытых, но шире используемых в промышленности.

Давным-давно, ещё в девяностых годах прошлого века, набирающий обороты автомобильный рынок остро нуждался в появлении серьёзных противоугонных систем (далее по тексту — иммобилайзеров). Для автоугонщиков в те времена не было особых препятствий, мешавших завести двигатель механической копией ключа или даже совсем без ключа — простым замыканием проводов. Нужны были иммобилайзеры, способные значительно затруднить процесс старта двигателя и дальнейшего угона автомобиля без родного ключа зажигания.

Давным-давно, ещё в девяностых годах прошлого века, набирающий обороты автомобильный рынок остро нуждался в появлении серьёзных противоугонных систем (далее по тексту — иммобилайзеров). Для автоугонщиков в те времена не было особых препятствий, мешавших завести двигатель механической копией ключа или даже совсем без ключа — простым замыканием проводов. Нужны были иммобилайзеры, способные значительно затруднить процесс старта двигателя и дальнейшего угона автомобиля без родного ключа зажигания. Всем привет! Одно из видений

Всем привет! Одно из видений