Zynq 7000. HDMI для платы Zynq Mini для baremetal

Я давно носил идею проверки HDMI на платах Zynq, и вот наконец-то дошли руки до этого интересного топика. В этой статье я покажу, что вывод изображения через HDMI достаточно прост, но ограничусь только рассмотрением вывода изображения из baremetal-приложений, а вопросы про Linux оставлю для следующей статьи. В первую очередь изучим возможность простого вывода изображения в HDMI из генератора тестовых изображений с использованием Test Pattern Generator в PL-логике, а затем коснёмся применения AXI Video DMA.

Всем интересующимся добро пожаловать под кат!

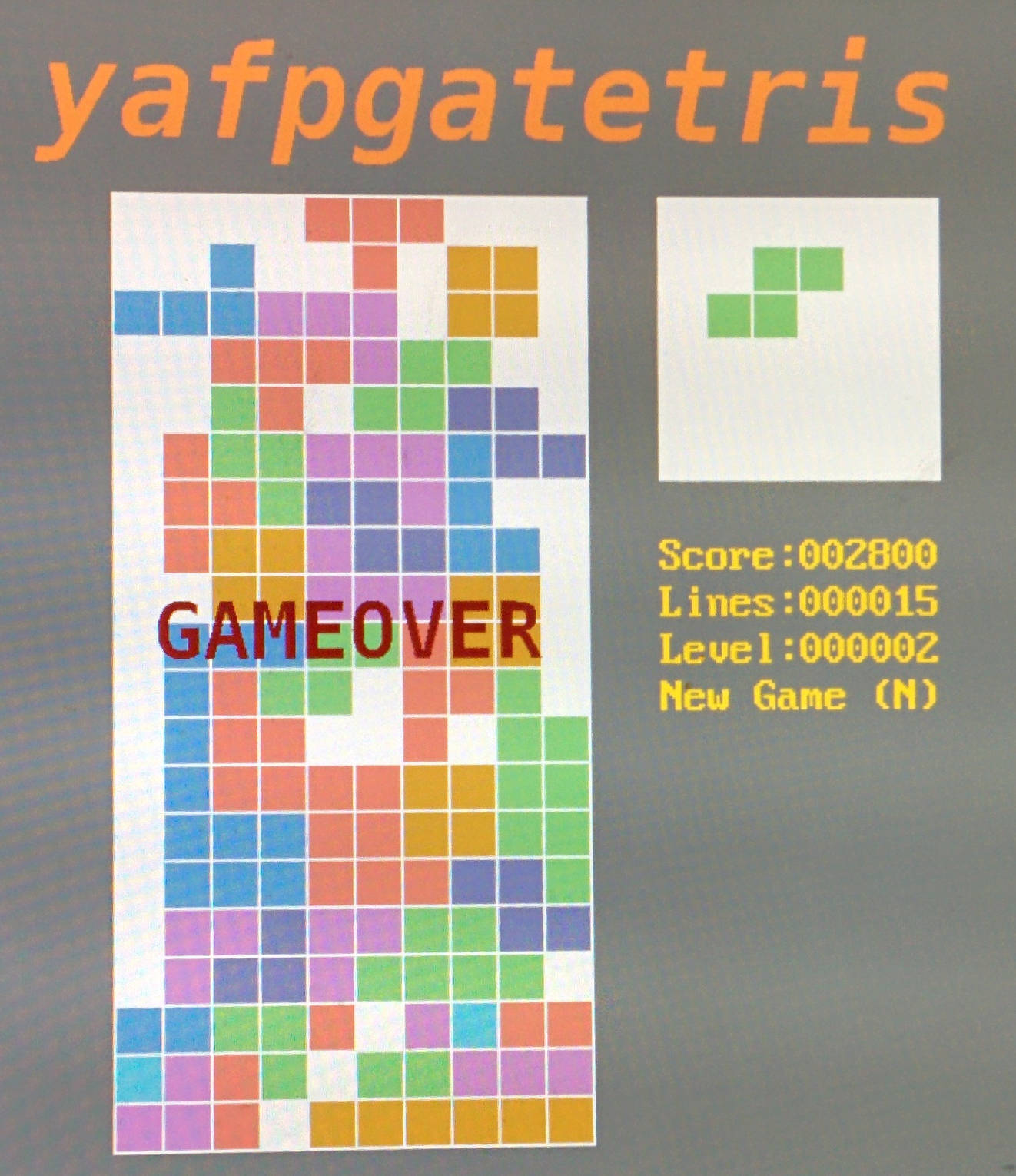

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на

На этих долгих новогодних выходных я задался вопросом: насколько легко написать какую-то простенькую игрушку на FPGA с выводом на дисплей и управлением с клавиатуры. Так родилась еще одна реализация тетриса на