Comments 28

Коллеги из Казани, конечно, в курсе забегов ispd? http://www.ispd.cc/?page=contests

Можно сравниваться с международными командами. Плюс брать инфроструктуру.

Как это делается: Алгоритм волновой трассировки.

Не вводите людей в заблуждение. Для трассировки рядов стандартных ячеек используется канальная трассировка.

«Хотя этот метод не для стандартных ячеек выстроенных в ряды, а для менее упорядоченного случая с небольшим числом компонент»

«Несмотря на то, что современные программы автоматической трассировки используют другие алгоритмы, алгоритм Ли остается отличным упражнением для тех, кто недавно освоил программирование и хочет написать небольшую программу трассировки сам.»

Далее, в сценарии роснановского курса, который я цитирую, есть и про канальную трассировку:

2.9. Трассировка

Трассировка — это создание геометрических чертежей расположения соединений между элементами микросхемы. Современные алгоритмы трассировки приспособлены к современной организации микросхем, на основе рядов из стандартных ячеек одинаковой высоты. Эта организация позволяет упростить задачу трассировки для очень больших микросхем за счет разбиения ее на подзадачи: сначала делается глобальная трассировка на уровне всего чипа (global routing), потом локальные трассировки внутри каждого канала (channel routing). Кроме этого есть подзадача трассировки областей так называемых коробок переключений (switchbox), которые находятся на пересечении каналов, расположенных в перпендикулярных направлениях.

Алгоритмы трассировки, как и алгоритмы размещения, пробуют ортимизировать общую длину соединений и задержки сигналов на критическом пути. Не все соединения проходят только между двумя выводами стандартных ячеек. Часть соединяет три, четыре или более выводов.

Алгоритмы трассировки следят за соблюдений правил проектирования (design rules). Эти правила программы проектирования берут из набора файлов под названием Process design kit (PDK), который разрабатывает полупроводниковая фабрика. К правилам проектирования относятся минимальные расстояния между соединениями и частями транзистора в разных ситуациях. Также алгоритмы трассировки смотрят, чтобы не возникали проблемы с электрическими помехами, которые возникают, когда соединения находятся слишком близко друг к другу (по-английски это называется crosstalk).

Одно из направлений развития программ трассировки — это трассировка трехмерных чипов. Уже сейчас трассировка учитывает соединения в нескольких слоях, то есть не является чисто двухмерной задачей. Но одновременно возникают и экспериментальные чипы с транзисторами и памятью на разных слоях, либо в «этажерке» из нескольких кристаллов, либо в монолитном трехмерном чипе. Для таких структур нужны новые методы трассировки.

И ни одного упоминания в статье таких инструментов, как graywolf и qrouter. Как так?

Разного рода мелких задачек в полноценном маршруте, которые можно улучшить — вагон и маленькая тележка. Например, «Standard Cell Pin Access and Physical Design in Advanced Lithography», чтобы далеко от задач роутинга не ходить.

Ещё некий Verilog to Routing (VTR) на Гитхабе периодически проскакивает — это не аналогичный проект?

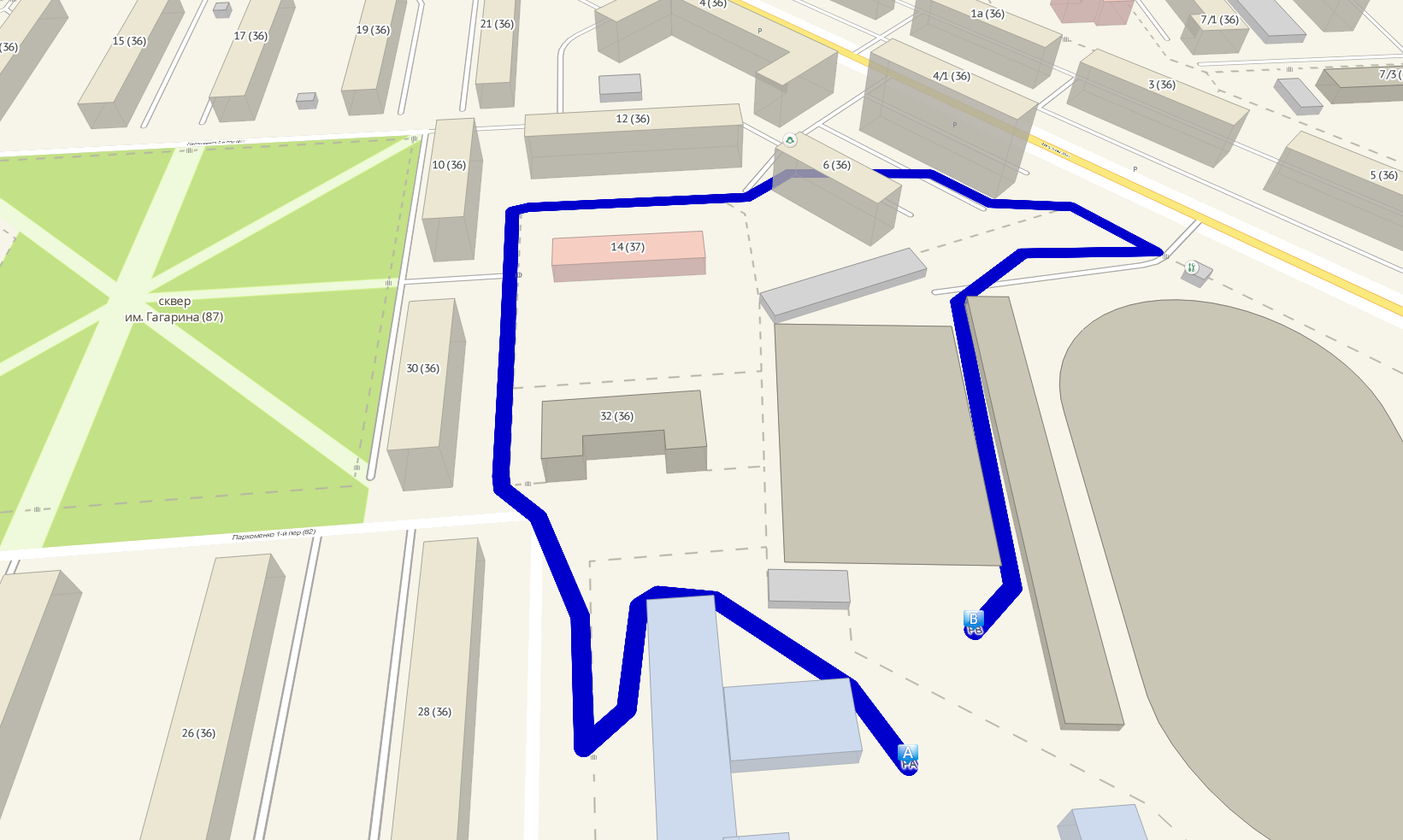

В такой простейшей постановке задача трассировки весьма подходит для применения Q-learning (нахождение оптимальной траектории + достижение конечной цели). Как водится, штраф за 1 ход + бонус за достижение конечной точки. И для разнообразия — штраф за изменение направления — тогда агент будет стараться избегать поворотов.

Ну почти как здесь, только надо запретить по диагонали ходить:

1.«Уничтожить монополию Америки в ЕDA.»

2."… простейшую программу Place & Route может написать студент за выходные, но вот на продвинутую потребуются десятилетия работы сотен людей и миллиарды долларов на R&D."

3."… Россия крупнее Армении и наверное может создать свой Synopsys. В конце-концов, программистов в России много, математиков тоже, а текущая рыночная капитализация Synopsys + Cadence примерно равна затратам на сочинскую олимпиаду."

Другое дело, что для покрытия e2e процессов надо иметь полное портфолио тулов — и тут да, несколько тысяч людей, десятки купленных стартапов, миллиарды долларов.

В результате сейчас _весь_мир_ может позволить себе содержать только Кейденс, Синопсис и Ментор Сименс бизнес. В существенной части это результат того, что производство микросхем тоже сконцентрировано сейчас до предела.

Из open-source есть http://opencircuitdesign.com/qflow/ и насколько я понимаю уже весь toolchain есть для FPGA/ASIC http://www.clifford.at/yosys/. Verilator успешно использовали в Tesla для их FSD чипа: Used Verilator, 50x faster than commercial simulators

Также помимо EDA тулов наверное есть смысл делать эмуляторы на FPGA и софт к ним. Как я понимаю без эмулирования дизайна на условном Synopsys ZeBu чип не выпустить. Юрий, у вас нет планов рассказать про эмуляцию и тестирование уже готового чипа ?

Эмуляторы на FPGA — это, что ли вроде FireSim? Кстати, а чем это отличается просто от синтеза под FPGA? Или это синтез под одну FPGA, будто это другая FPGA с другими скоростными характеристиками?

Для понимания масштаба, последний Spectre X умеет разворачиваться в амазоновском облаке и запускаться на большом количестве мультсокетных машин. При этом моделирование может идти от нескольких часов до десятков дней.

На этом фоне скорость цифрового моделирования не интересует вообще никого.

Когда тест на VCS работает в 60 раз быстрее чем на Icarus Verilog, это сильно меняет дело. Так как в первом случае regression идет overnight, а во втором случае это бы заняло 1 месяц. Ночь или месяц — большая разница.

Ну и если все же рассуждать про большие дизайны, то значит про UVM. Как дела у икаруса с этим делом? Подозреваю, что примерно никак, потому что UVM нынче в основном бегает на SV, а поддержки SV(SystemVerilog) у него нету.

Лист недочётов икаруса для коммерческой разработки можно продолжать бесконечно, но совершенно бесмысслено. Равно как и сильно вкладываться в движки для цифры, когда аналог моделируется на порядки дольше, а этого самого аналога нынче в самом захудалом SoC — вагон.

Ну и упреждая возможный вопрос про моделирование на GPU — пока никто не хочет в это вкладываться, потому что фермы с CPU уже у всех больших компаний есть, а тратится на фермы GPU для какого-то одного конкретного тула экономически невыгодно.

Ну и общий тренд на моделирование в облаке сильно упрощает жизнь всяким стартапам, значительно снижая капитальные инвестиции и затраты на обслуживание. А мощностей в облаке, как водится, больше нужного.

Уничтожить монополию Америки в EDA. Иннополис делает первый шаг