Это вторая и заключительная часть большой статьи. Ознакомиться с первой частью можно по ссылке.

Основная прелесть использования ПЛИС, на мой взгляд, состоит в том, что разработка аппаратуры превращается в программирование со всеми его свойствами: написание и отладка кода как текста на специализированных языках описания аппаратуры (HDL); код распространяется в виде параметризованных модулей (IP-блоков), что позволяет его легко переиспользовать в других проектах; распределенная разработка обширным коллективом разработчиков с системой контроля версий, такой же, как у программистов (Git); и, как и в программировании, ничтожно низкая стоимость ошибки.

Последнее очень важно, так как если при разработке устройства классическим методом разработчик несет вполне существенные затраты на сборку и производство изделия, и любая схемотехническая ошибка или ошибка трассировки печатной платы — это всегда выход на очередную итерацию и попадание на деньги, то при работе с ПЛИС ошибки ничтожны по своей стоимости и легко устранимы. И даже если в серийном изделии обнаруживается ошибка, то её во многих случаях можно устранить очередным апгрейдом прошивки «в поле» без замены изделия. Короче, с приходом ПЛИС разработка цифровой аппаратуры все больше и больше выглядит как ��рограммирование, а это, помимо всего прочего, существенно понижает порог вхождения в тему, и все больше программистов становятся разработчиками «железа». А новые люди, в свою очередь, приносят с собой в индустрию новые подходы и принципы.

В этой статье я хочу поделиться своим небольшим опытом «программирования» микросхем ПЛИС и тем, как я постепенно погружался в тему ПЛИСоводства. Изначально я собирался написать небольшую заметку про открытый тулчейн для синтеза Yosys. Потом — про язык SpinalHDL и синтезируемое микропроцессорное ядро VexRiscv, на нём написанное. Потом — про замену микроконтроллеров микросхемами ПЛИС на примере моей отладочной платы «Карно». Но в процессе я погрузился в историю появления Hardware Description Languages (HDL), и когда я начал писать, Остапа, как это часто бывает, понесло... В общем, получилось то, что получилось.

СОДЕРЖАНИЕ

1. Краткий экскурс в историю

2. Появления программируемых логических устройств

3. Производители микросхем ПЛИС

4. Синтез цифровых схем для ПЛИС

5. Yosys Open SYnthesis Suite

6. Как установить утилиты тулчейна Yosys

7. Пример использования открытого тулчейна Yosys

7.1. Установка и настройка «basics-graphics-music»

7.2 Лабораторная работа «01_and_or_not_xor_de_morgan»

7.3 Загрузка битстрима в микросхему ПЛИС

8. Типовой Makefile для синтеза с помощью Yosys

9. Файл описания внешних сигналов и ограничений (LPF, PCF, CST)

10. Особенности синтаксиса Yosys

10.1 Макро YOSYS

10.2 Многомерные массивы сигналов

10.3 Функция возведения в степень ($POW) и оператор **

10.4 Функция не может иметь доступ к сигналу, описанному за её пределами

10.5 Сигналы нулевой или отрицательной размерности

10.6 Сложные битовые манипуляции иногда могут выдавать ошибку о loopback-ах

10.7 Глобализация сигналов

11. Анализируем сообщения от тулов

11.1 Сообщения от утилиты yosys

11.2 Сообщения от утилиты nextpnr

12. Синтезируемая ЭВМ

12.1 Синтезируемое вычислительное ядро VexRiscv

12.2 Синтезируемые системы-на-кристалле на базе VexRiscv

13. Язык описания аппаратуры SpinalHDL

13.1 Базовые конструкции языка SpinalHDL

13.2 FSM, потоки, конвейеры, тактовые домены

13.3 Установка SpinalHDL

13.4 Разбор шаблона SpinalTemplateSbt

13.5 Подготовка Makefile-а для синтеза из SpinalHDL в битстрим

13.6 Анализируем вывод сообщений SpinalHDL

13.7 Симуляция и верификация в SpinalHDL

14. Синтез вычислительного ядра VexRiscv

14.1 Знакомство с репозиторием VexRiscv

14.2 Установка компилятора для архитектуры RISC-V

14.3 Подготавливаем Makefile, LPF и toplevel.v

14.4 Добавляем точку входа для генерации СнК Murax для платы «Карно»

14.5 Модифицируем код программы «hello_world»

14.6 Сборка СнК Murax и ядра VexRiscv

14.7 Запускаем СнК Murax на ПЛИС и тестируем «hello_world»

15. Устройство синтезируемого СнК Murax и ядра VexRiscv

15.2 Структура вычислительного ядра VexRiscv

15.3 Плагины вычислительного ядра VexRiscv

16. Эксперименты с ядром VexRiscv и СнК Murax

16.1 Оптимизация на примере плагина RegFilePlugin

16.2 Увеличиваем тактовую частоту ядра используя встроенный PLL

16.3 Увеличиваем производительность инструкций сдвига

17. Добавляем свои аппаратные блоки (IP-блоки)

17.1 Микросекундный машинный таймер MTIME

17.2 Подключаем микросхему SRAM

17.2.1 Разрабатываем контроллер SRAM

17.2.2 Тестируем память и контроллер SRAM

17.2.3 Используем SRAM с функцией malloc

17.2.4 Добавляем блоки вычислителей Div и Mul

17.2.5 Задействуем функцию printf

17.3 Подключаем контроллер прерываний PLIC

17.3.1 Разрабатываем простейший контроллер прерываний MicroPLIC

17.3.2 Задействуем контроллер прерываний MicroPLIC из Си программы

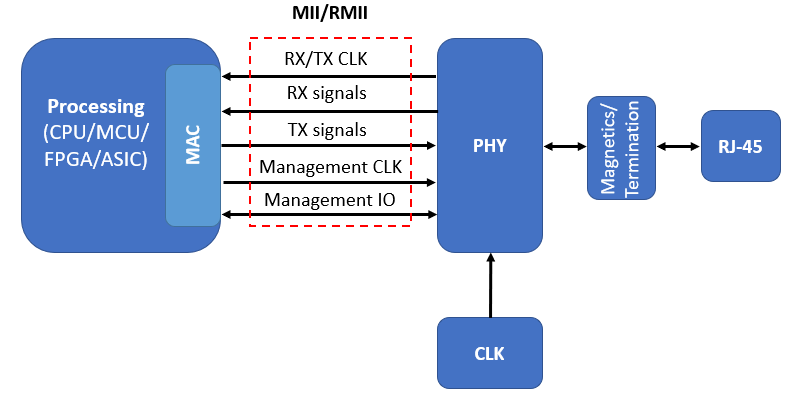

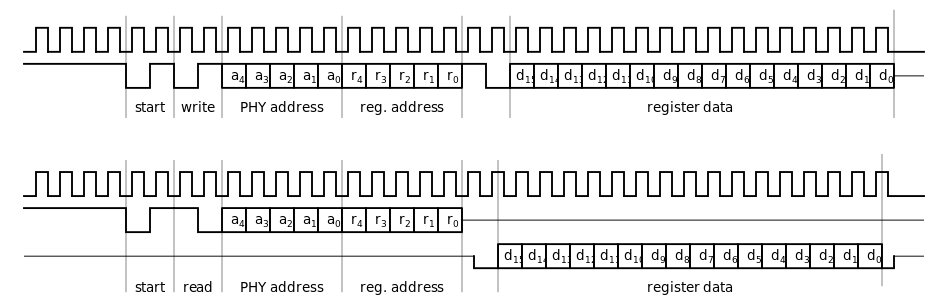

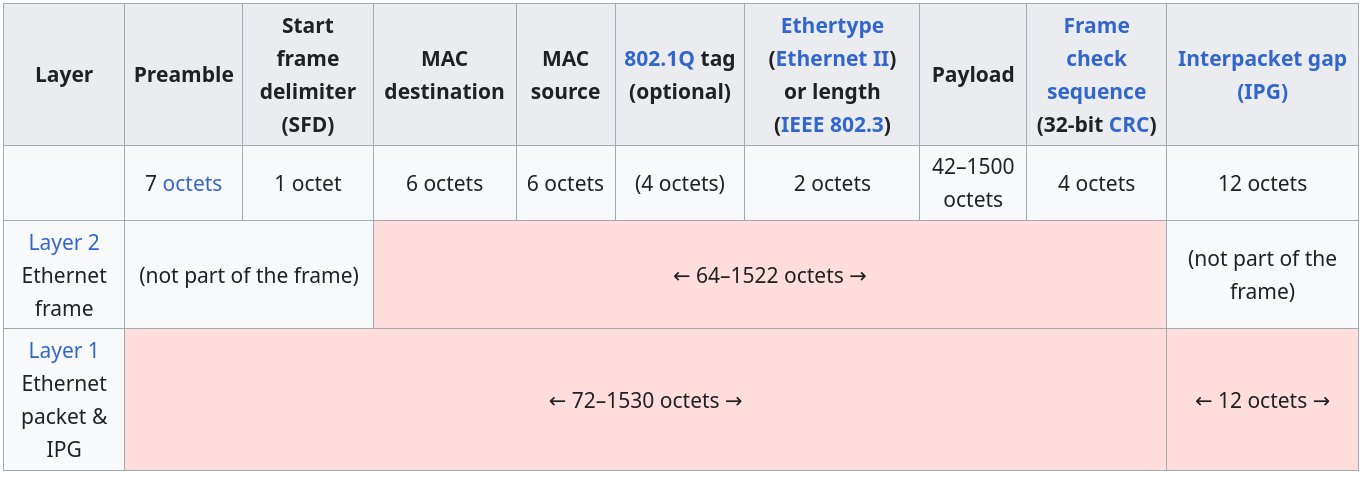

17.4 Подключаем контроллер FastEthernet (MAC)

17.4.2 Подключаем компонент MacEth

17.4.3 Разрабатываем драйвер для компонента MacEth

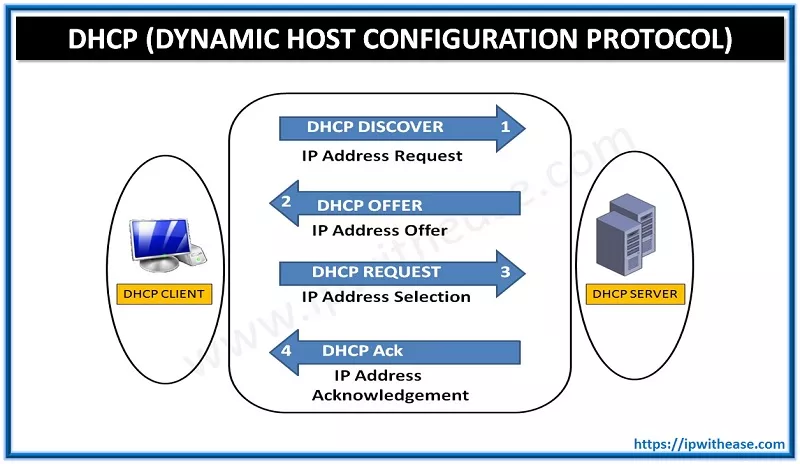

17.4.4 Отправляем запрос в DHCP сервер

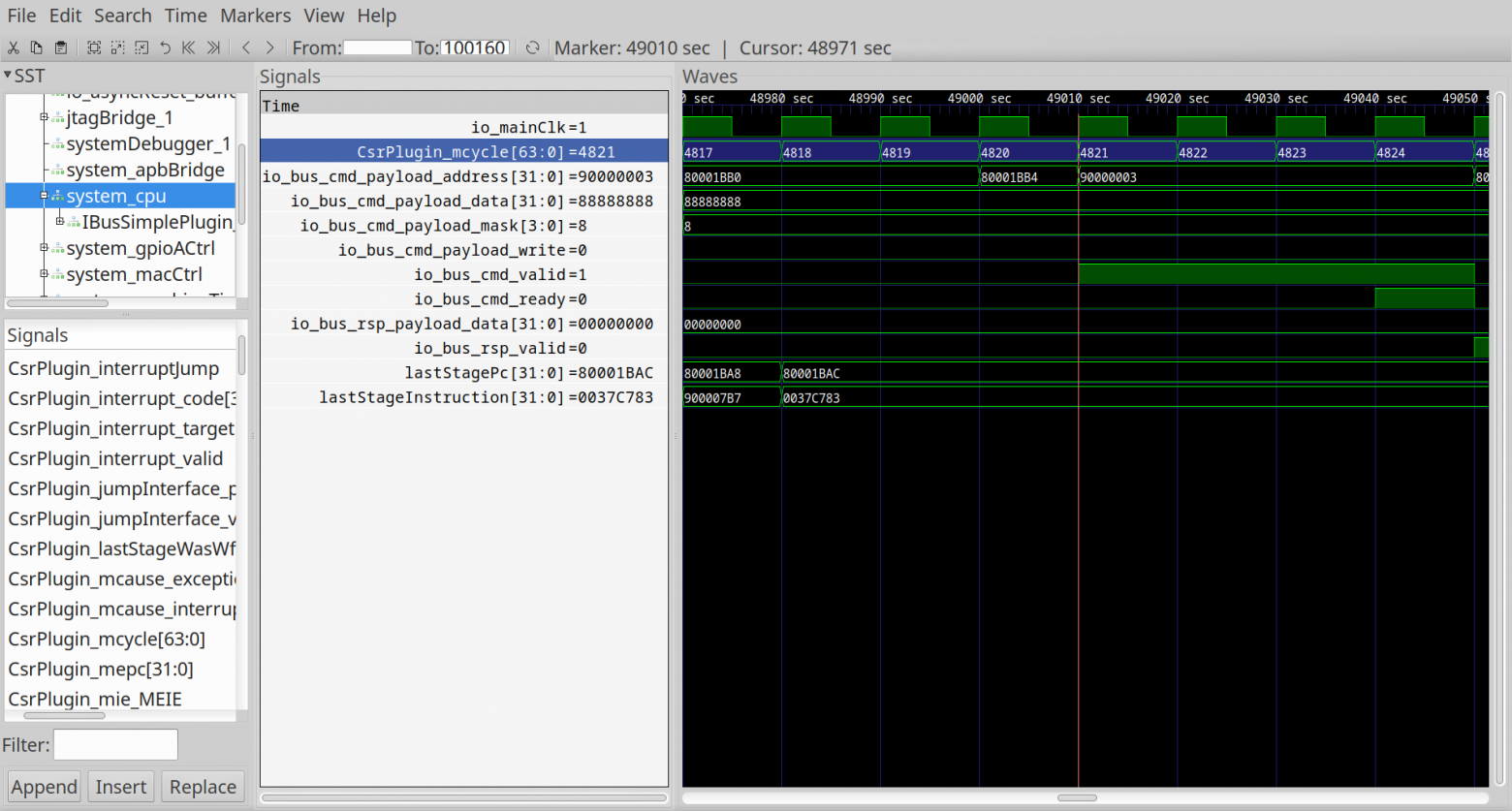

18. Потактовая симуляция СнК Murax

19. Более сложный пример: VexRiscvWithHUB12ForKarnix

15. Устройство синтезируемого СнК Murax и ядра VexRiscv

Теперь, когда у нас есть возможность модифицировать, собирать и пересобирать СнК Murax и Сишный код программы для него, настало время погрузиться в детали и посмотреть, как код СнК выглядит на языке SpinalHDL, как задается конфигурация ядра VexRiscv и как к нему подключается различная периферия.

15.1 Структура СнК Murax

Напомню, что код СнК Murax находится в файле ./src/main/scala/vexriscv/demo/Murax.scala, выше мы уже добавляли свой код в этот файл — дополнительную точку входа для сборки. Сейчас посмотрим немного глубже.

СнК Murax по структуре очень похож на СнК Briey, структура которого изображена рис. 20, но вместо AxiCrossbar в СнК Murax используется PipelinedMemoryBus.

Весь код СнК Murax описывается одним классом Murax, который является наследником класса Component, т. е. Murax является аппаратным компонентом. Конструктор класса Murax имеет параметр config, который является структурой типа MuraxConfig, содержащей дефолтные параметры СнК (тактовую частоту, размер ОЗУ и т.д.)

case class Murax(config : MuraxConfig) extends Component{ import config._ ...

Как и у всякого компонента, у Murax есть внешние сигналы ввода/вывода, сигналы сброса и тактирования:

val io = new Bundle { //Clocks / reset val asyncReset = in Bool() val mainClk = in Bool() //Main components IO val jtag = slave(Jtag()) //Peripherals IO val gpioA = master(TriStateArray(gpioWidth bits)) val uart = master(Uart()) val xip = ifGen(genXip)(master(SpiXdrMaster(xipConfig.ctrl.spi))) }

Конструкция ifGen(genXip) добавит генерацию следующего за ней кода, если параметр genXip будет установлен в значение True. XiP это флэш память с SPI интерфейсом и функцией «eXecution In Place» — возможностью исполнения кода прямо из флэш памяти. В данном случае она не задействована.

Murax содержит два домена тактирования:

val systemClockDomain = ClockDomain( clock = io.mainClk, reset = resetCtrl.systemReset, frequency = FixedFrequency(coreFrequency) ) val debugClockDomain = ClockDomain( clock = io.mainClk, reset = resetCtrl.mainClkReset, frequency = FixedFrequency(coreFrequency) )

Домен тактирования debugClockDomain содержит JTAG интерфейс и все что с ним связано. Вся остальная периферия, а также ядро VexRiscv находятся в домене systemClockDomain. Далее будем рассматривать только домен systemClockDomain.

Центральным элементом в системном до��ене является шина, которая называется PipelinedMemoryBus, управляет которой шинный арбитр MuraxMasterArbiter:

val mainBusArbiter = new MuraxMasterArbiter(pipelinedMemoryBusConfig, bigEndianDBus)

Арбитр имеет три порта: два ведомых (slave) порта для подключения к ядру VexRiscv (порт инструкций iBus и порт данных dBus) и один порт мастер MainBus.

val mainBusMapping = ArrayBuffer[(PipelinedMemoryBus,SizeMapping)]()

Подключение ядра VexRiscv к арбитру осуществляется следующим затейливым образом. Сначала инстанциируется класс VexRiscv с передачей ему большой структуры с настройками VexRiscvConfig — она содержит описание того, какие плагины и функции должны быть включены/выключены:

//Instanciate the CPU val cpu = new VexRiscv( config = VexRiscvConfig( plugins = cpuPlugins += new DebugPlugin(debugClockDomain, hardwareBreakpointCount) ) )

После этого, в цикле перебираются все подключенные в данный момент плагины из которых состоит ядро VexRiscv, и каждый плагин линкуется с шинами iBus и dBus - они являются объектами типа Stream. Напомню, что Stream состоит из комплексного сигнала cmd для передачи запроса и комплексного сигнала rsp для ответа. Линковка происходит операторами <>, << или >>, вот так:

//Checkout plugins used to instanciate the CPU to connect them to the SoC val timerInterrupt = False val externalInterrupt = False for(plugin <- cpu.plugins) plugin match{ case plugin : IBusSimplePlugin => mainBusArbiter.io.iBus.cmd <> plugin.iBus.cmd mainBusArbiter.io.iBus.rsp <> plugin.iBus.rsp case plugin : DBusSimplePlugin => { if(!pipelineDBus) mainBusArbiter.io.dBus <> plugin.dBus else { mainBusArbiter.io.dBus.cmd << plugin.dBus.cmd.halfPipe() mainBusArbiter.io.dBus.rsp <> plugin.dBus.rsp } } case plugin : CsrPlugin => { plugin.externalInterrupt := externalInterrupt plugin.timerInterrupt := timerInterrupt } case plugin : DebugPlugin => plugin.debugClockDomain{ resetCtrl.systemReset setWhen(RegNext(plugin.io.resetOut)) io.jtag <> plugin.io.bus.fromJtag() } case _ => }

Для специфических плагинов, таких как CsrPlugin и DebugPlugin производится линковка дополнительных сигналов, в данном случае это сигналы externalInterrupt, timerInterrupt и io.jtag.

С другой стороны арбитра к шине MainBus подключается шина набортного ОЗУ ram типа MuraxPipelinedMemoryBusRam и мост apbBridge типа PipelinedMemoryBusToApbBridge

//****** MainBus slaves ******** val mainBusMapping = ArrayBuffer[(PipelinedMemoryBus,SizeMapping)]() val ram = new MuraxPipelinedMemoryBusRam( onChipRamSize = onChipRamSize, onChipRamHexFile = onChipRamHexFile, pipelinedMemoryBusConfig = pipelinedMemoryBusConfig, bigEndian = bigEndianDBus ) mainBusMapping += ram.io.bus -> (0x80000000l, onChipRamSize) val apbBridge = new PipelinedMemoryBusToApbBridge( apb3Config = Apb3Config( addressWidth = 20, dataWidth = 32 ), pipelineBridge = pipelineApbBridge, pipelinedMemoryBusConfig = pipelinedMemoryBusConfig ) mainBusMapping += apbBridge.io.pipelinedMemoryBus -> (0xF0000000l, 1 MB)

Шине ОЗУ выделяется область адресного пространства, начиная с 0x80000000 и длиной onChipRamSize. Переменная оnChipRamSize — это член класса, которая задается при инстанциировании класса Murax в точке входа. В нашем случае, для платы «Карно», она установлена в 96 КБ (см. главу «14.4 Добавляем точку входа для генерации СнК Murax для платы «Карно»).

Для моста apbBridge резервируется адресное пространство, начиная с 0xF0000000 и размером 1 М��. Через мост apbBridge подключается вся стандартная периферия:

//******** APB peripherals ********* val apbMapping = ArrayBuffer[(Apb3, SizeMapping)]() val gpioACtrl = Apb3Gpio(gpioWidth = gpioWidth, withReadSync = true) io.gpioA <> gpioACtrl.io.gpio apbMapping += gpioACtrl.io.apb -> (0x00000, 4 kB) val uartCtrl = Apb3UartCtrl(uartCtrlConfig) uartCtrl.io.uart <> io.uart externalInterrupt setWhen(uartCtrl.io.interrupt) apbMapping += uartCtrl.io.apb -> (0x10000, 4 kB) val timer = new MuraxApb3Timer() timerInterrupt setWhen(timer.io.interrupt) apbMapping += timer.io.apb -> (0x20000, 4 kB) ...

Каждому компоненту на шине apbBrigde резервируется своё адресное пространство для регистров управления. Из кода выше видно, что регистры периферийного порта gpioA будут расположены начиная с адреса 0xF0000000 + 0x00000, а регистры UART будут находиться с адреса 0xF0000000 + 0x10000, и т. д.

На этом код СнК Murax заканчивается.

Если мы заходим создать свой периферийный компонент, то нам потребуется сделать его наследником класса Component, содержащего интерфейс определяемый классом Apb3, после чего подключить его к шине apbBrigde в этом же месте и аналогичным образом. Далее я покажу, как это сделать на нескольких примерах.

15.2 Структура вычислительного ядра VexRiscv

Как уже было отмечено выше, вычислительное ядро VexRisсv — это обычный компонент, т. е. является наследником класса Component, описан в файле ./src/main/scala/vexriscv/VexRiscv.scala и инстанциируется строкой кода вида:

val cpu = new VexRiscv( config = VexRiscvConfig( ...) )

где параметр config задает настройки вычислительно ядра, описываемые классом VexRiscvConfig. Посмотрим на структуру этого конфигурационного класса, чтобы понять, какие «цапы» мы можем крутить и в какой степени мы можем изменять структуру ядра VecRiscv:

case class VexRiscvConfig(){ var withMemoryStage = true var withWriteBackStage = true val plugins = ArrayBuffer[Plugin[VexRiscv]]() ...

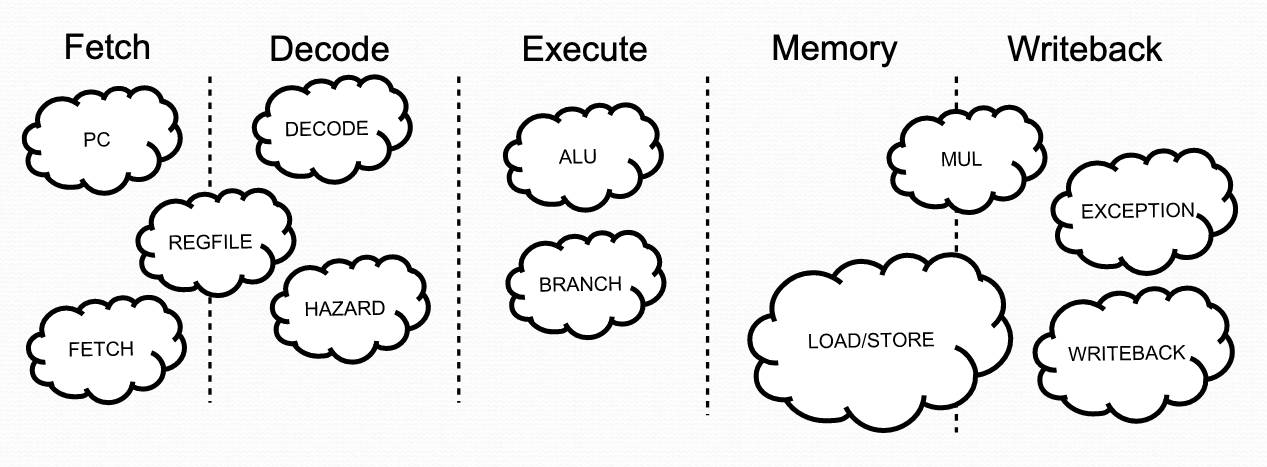

На первый взгляд, настроек немного: две булевых переменных withMemoryStage и withWriteBackStage, и переменная plugins описывающая массив абстрактных интерфейсных объектов типа Plugin[VexRiscv]. Булевы переменные задают возможность подключения двух ступеней конвейера: Memory и WriteBack. Напомню, что ядро VexRiscv является конвейерной реализацией архитектуры RISC-V, в которой конвейер может содержать от двух до пяти ступеней: [Fetch], Decode, Execute, [Memory], [WriteBack]. Таким образом, ступени Memory и WriteBack можно включать/выключать, изменяя переменные withMemoryStage и withWriteBackStage. Что касается ступени Fetch, то она подключается при необходимости как плагин добавлением в массив plugins. Плагины — это то, что делает VexRiscv расширяемым, интересным и уникальным. На рис. 27 приведено обобщенное изображение структуры конвейера VexRiscv и того, как некоторые плагины распределены между его ступенями.

15.3 Плагины вычислительного ядра VexRiscv

Посмотрим, какими плагинами на данный момент мы располагаем и какими индивидуальными настройками они обладают. Весь код плагинов находится в подкаталоге ./src/main/scala/vexriscv/plugin/, по одному файлу на плагин:

rz@devbox:~/VexRiscv$ ls -w 120 ./src/main/scala/vexriscv/plugin/ AesPlugin.scala FpuPlugin.scala NoPipeliningPlugin.scala BranchPlugin.scala HaltOnExceptionPlugin.scala PcManagerSimplePlugin.scala CfuPlugin.scala HazardPessimisticPlugin.scala Plugin.scala CsrPlugin.scala HazardSimplePlugin.scala PmpPlugin.scala DBusCachedPlugin.scala IBusCachedPlugin.scala PmpPluginNapot.scala DBusSimplePlugin.scala IBusSimplePlugin.scala RegFilePlugin.scala DebugPlugin.scala IntAluPlugin.scala ShiftPlugins.scala DecoderSimplePlugin.scala MemoryTranslatorPlugin.scala SingleInstructionLimiterPlugin.scala DivPlugin.scala Misc.scala SrcPlugin.scala DummyFencePlugin.scala MmuPlugin.scala StaticMemoryTranslatorPlugin.scala EmbeddedRiscvJtag.scala Mul16Plugin.scala VfuPlugin.scala ExternalInterruptArrayPlugin.scala MulDivIterativePlugin.scala YamlPlugin.scala Fetcher.scala MulPlugin.scala FormalPlugin.scala MulSimplePlugin.scala

Детальное описание большинства плагинов можно найти в README файле в репозитории VexRiscv по ссылке.

Ниже я приведу описания только части наиболее важных и часто используемых плагинов с некоторыми поясняющими комментариями. С этими плагинами мы далее проведем ряд экспериментов.

DBusSimplePlugin — создает шину данных для вычислительного ядра, без кеширования данных. Позволяет подключать ядро к шинам вида Axi4Shared, Avalon, Withbone, AhbLite3, Bmb, PipelinedMemoryBus. Последняя является самой простой и используется в СнК Murax.

Ниже приведено определение класса DBusSimplePlugin, из которого можно понять, какими фичами обладает данный плагин.

class DBusSimplePlugin(catchAddressMisaligned : Boolean = false, catchAccessFault : Boolean = false, earlyInjection : Boolean = false, /*, idempotentRegions : (UInt) => Bool = (x) => False*/ emitCmdInMemoryStage : Boolean = false, onlyLoadWords : Boolean = false, withLrSc : Boolean = false, val bigEndian : Boolean = false, memoryTranslatorPortConfig : Any = null) extends Plugin[VexRiscv] with DbusAccessService

Видно, что DBusSimplePlugin имеет порт для подключения транслятора адресного пространства памяти (MMU), который тоже является отдельным плагином.

DBusCachedPlugin — создает шину данных для вычислительно ядра, но с организацией кеша данных. Позволяет подключать ядро к шинам: Axi4Shared, Avalon, Withbone, Bmb и PipelinedMemoryBus. Используется в СнК Briey с шиной Axi4Shared. Как и его упрощенный собрат имеет порт для подключения транслятора адресного пространства памяти (MMU).

Определение класса DBusCachedPlugin и его параметров следующее:

class DBusCachedPlugin(val config : DataCacheConfig, memoryTranslatorPortConfig : Any = null, var dBusCmdMasterPipe : Boolean = false, dBusCmdSlavePipe : Boolean = false, dBusRspSlavePipe : Boolean = false, relaxedMemoryTranslationRegister : Boolean = false, csrInfo : Boolean = false, tightlyCoupledAddressStage : Boolean = false) extends Plugin[VexRiscv] with DBusAccessService with DBusEncoding Service with VexRiscvRegressionArg

Данный плагин, используя сервис от плагина CsrPlugin, может экспортировать читаемый csrInfo регистр 0xCC0 с двумя полями [7:0] и [27:20] содержащий информацию о кеше:

if(csrInfo){ val csr = service(classOf[CsrPlugin]) csr.r(0xCC0, 0 -> U(cacheSize/wayCount), 20 -> U(bytePerLine)) }

IBusSimplePlugin — обеспечивает шину для передачи инструкций в вычислительное ядро, без организации кеша. Позволяет подключать ядро к шинам вида Avalon, Withbone, AhbLite3, Bmb, PipelinedMemoryBus и Axi4ReadOnly. Используется в СнК Murax. По сути, данный плагин является Fetch ступенью конвейера.

Описание класса IBusSimplePlugin и его параметров выглядит следующим образом:

class IBusSimplePlugin( resetVector : BigInt, val cmdForkOnSecondStage : Boolean, val cmdForkPersistence : Boolean, val catchAccessFault : Boolean = false, prediction : BranchPrediction = NONE, historyRamSizeLog2 : Int = 10, keepPcPlus4 : Boolean = false, compressedGen : Boolean = false, val busLatencyMin : Int = 1, val pendingMax : Int = 7, injectorStage : Boolean = true, val rspHoldValue : Boolean = false, val singleInstructionPipeline : Boolean = false, val memoryTranslatorPortConfig : Any = null, relaxPredictorAddress : Boolean = true, predictionBuffer : Boolean = true, bigEndian : Boolean = false, vecRspBuffer : Boolean = false ) extends IbusFetcherImpl

Данный плагин имеет множество интересных параметров. Например, параметр resetVector задает адрес в памяти, с которого вычислительное ядро начнет исполнение программы; параметр compressedGen позволяет подключить код для декодера сжатого набора инструкций RV32C; параметр prediction позволяет подключать код предсказателя ветвлений, тоже в виде отдельного плагина.

IBusCachedPlugin — обеспечивает шину для передачи инструкций в вычислительный модуль с использованием кеша. Функционал этого плагина аналогичен IBusSimplePlugin. Объявление класса IBusCachedPlugin выглядит следующим образом:

class IBusCachedPlugin(resetVector : BigInt = 0x80000000l, relaxedPcCalculation : Boolean = false, prediction : BranchPrediction = NONE, historyRamSizeLog2 : Int = 10, compressedGen : Boolean = false, keepPcPlus4 : Boolean = false, val config : InstructionCacheConfig, memoryTranslatorPortConfig : Any = null, injectorStage : Boolean = false, withoutInjectorStage : Boolean = false, relaxPredictorAddress : Boolean = true, predictionBuffer : Boolean = true) extends IbusFetcherImpl

DecoderSimplePlugin — обеспечивает другие плагины сервисом дешифрации инструкций.

class DecoderSimplePlugin(catchIllegalInstruction : Boolean = false, throwIllegalInstruction : Boolean = false, assertIllegalInstruction : Boolean = false, forceLegalInstructionComputation : Boolean = false, decoderIsolationBench : Boolean = false, stupidDecoder : Boolean = false) extends Plugin[VexRiscv] with DecoderService

Имеет опции для включения/отключения отлова нелегальных (нереализованных) инструкций: если параметр catchIllegalInstruction установлен в True, то ядро будет формировать trap и соответствующее исключение, если на вход дешифратора попадет инструкция несоответствующая текущему набору.

Добавление инструкций в дешифратор осуществляется вызовом метода decoderService.add следующим образом:

decoderService.add( //Bit pattern of the new instruction key = M"0000011----------000-----0110011", //Decoding specification when the 'key' pattern is recognized in the instruction List( IS_SIMD_ADD -> True, //Inform the pipeline that the current instruction is a SIMD_ADD instruction REGFILE_WRITE_VALID -> True, //Notify the hazard management unit that this instruction writes to the register file BYPASSABLE_EXECUTE_STAGE -> True, //Notify the hazard management unit that the instruction result is already accessible in the EXECUTE stage (Bypass ready) BYPASSABLE_MEMORY_STAGE -> True, //Same as above but for the memory stage RS1_USE -> True, //Notify the hazard management unit that this instruction uses the RS1 value RS2_USE -> True //Same than above but for RS2. ) )

RegFilePlugin — обеспечивает стандартный регистровый файл согласно спецификации RISC-V. Описание класса RegFilePlugin следующее:

class RegFilePlugin(regFileReadyKind : RegFileReadKind, zeroBoot : Boolean = false, x0Init : Boolean = true, writeRfInMemoryStage : Boolean = false, readInExecute : Boolean = false, syncUpdateOnStall : Boolean = true, rv32e : Boolean = false, withShadow : Boolean = false //shadow registers aren't transition hazard free ) extends Plugin[VexRiscv] with RegFileService

Данный плагин имеет ряд опций для оптимизации. Параметр regFileReadyKind задает тип используемых ячеек памяти для регистров: SYNC или ASYNС. Первый вариант (SYNC) — будут задействованы синхронные D-триггеры (задержка в 1 такт), хорошо ложится на стандартные LUT ячейки ПЛИС. Вариант ASYNC позволяет использовать асинхронные ячейки памяти SRAM и BRAM (без задержки), подходит для проектирования микросхем (ASIC).

HazardSimplePlugin — реализует очень важный для конвейерных процессоров механизм называемый «Hazard», суть которого состоит в том, чтобы отслеживать взаимозависимости между разными инструкциями, исполняемыми на разных ступенях конвейера в один и тот же момент времени. В случае выявления зависимостей, данный плагин может придержать (остановить) исполнение инструкции в ступени дешифратора (Decoder) или, если есть такая возможность, передать результат с более поздних ступеней, чтобы не задерживать исполнение. Описание класса HazardSimplePlugin и его параметров приведено ниже:

class HazardSimplePlugin(bypassExecute : Boolean = false, bypassMemory: Boolean = false, bypassWriteBack: Boolean = false, bypassWriteBackBuffer : Boolean = false, pessimisticUseSrc : Boolean = false, pessimisticWriteRegFile : Boolean = false, pessimisticAddressMatch : Boolean = false) extends Plugin[VexRiscv] with HazardService

Параметры bypassExecute, bypassMemory, bypassWriteBack разрешают передачу результата из соответствующих ступеней на стадию (ступень) Decoder.

IntAluPlugin — плагин, реализующий целочисленное АЛУ. Встраивается в стадию Execute и реализует такие инструкции как ADD, SUB, SLT, SLTU, XOR, OR, AND, LUI и AUIPC. Это очень простой плагин не имеющий параметров, определение класса IntAluPlugin выглядит следующим образом:

class IntAluPlugin extends Plugin[VexRiscv]

LightShifterPlugin и FullBarrelShifterPlugin — эти плагины реализуют инструкции побитного сдвига SLL, SRL и SRA. Плагин LightShifterPlugin является простой многотактовой реализацией сдвига, выполняющий задачу за N тактов, где N — число бит на которое требуется выполнить сдвиг. FullBarrelShifterPlugin — выполняет полный сдвиг на заданное число бит за один такт. Полная реализация является очень ресурсоемкой (требует большого количества логических элементов) и вносит большую задержку в исполнение, а значит существенно уменьшает максимальную тактовую частоту ядра. Определения классов:

class FullBarrelShifterPlugin(earlyInjection : Boolean = false) extends Plugin[VexRiscv]

и

class LightShifterPlugin extends Plugin[VexRiscv]

FpuPlugin — плагин, реализующий инструкции с плавающей запятой («Floating Point Unit» - FPU). Блок FPU может быть как встроенным в конвейер, так и использовать внешний FPU блок (внешний сопроцессор). Описание класса FpuPlugin выглядит следующим образом:

class FpuPlugin(externalFpu : Boolean = false, var simHalt : Boolean = false, val p : FpuParameter) extends Plugin[VexRiscv] with VexRiscvRegressionArg

Параметр p является сложной структурой с настройками блока FPU, определение этой структуры выглядит следующим образом:

case class FpuParameter( withDouble : Boolean, asyncRegFile : Boolean = false, mulWidthA : Int = 18, mulWidthB : Int = 18, schedulerM2sPipe : Boolean = false, sim : Boolean = false, withAdd : Boolean = true, withMul : Boolean = true, withDivSqrt : Boolean = false, withDiv : Boolean = true, withSqrt : Boolean = true, withShortPipMisc : Boolean = true)

В файле README.md репозитория VexRiscv приводится детальное описание устройства блока FPU и его настроек. Ознакомиться можно по ссылке.

PcManagerSimplePlugin — простой плагин реализует регистр счетчика команд (PC). Данный плагин в текущей версии ядра не используется, а регистр счетчика команд интегрирован в базовый функционал ядра, в класс VexRiscv.

BranchPlugin — данный плагин осуществляется предсказание ветвлений с целью оптимизации хода исполнения программы, так как каждый «промах» (загрузка неверной инструкции в декодер) может иметь стоимость в 2 или 4 такта. Этот плагин уменьшает негативное влияния команд ветвления на кеш инструкций. Плагин реализует все инструкции ветвления: JAL, JALR, BEQ, BNE, BLT, BGE, BLTU и BGEU. Определение класса BranchPlugin:

class BranchPlugin(earlyBranch : Boolean, catchAddressMisaligned : Boolean = false, fenceiGenAsAJump : Boolean = false, fenceiGenAsANop : Boolean = false, decodeBranchSrc2 : Boolean = false) extends Plugin[VexRiscv] with PredictionInterface

В VexRiscv реализованы следующие алгоритмы предсказания ветвлений, которые задаются параметром prediction и плагина IBusSimplePlugin или IBusCachedPlugin (напомню, что эти два плагина реализуют Fetch ступень конвейера):

NONE — без предсказания, любое изменение регистра PC инструкциями ветвления приводит к полному набору «штрафных» циклов (от 2 до 4).

STATIC — спекулятивное предсказание, фактически всегда выбирается одна и та же ветвь выполнения инструкции ветвления. Если предсказание сбылось, то «штраф» уменьшается до одного дополнительного такта, иначе «штраф» будет полным.

DYNAMIC — для предсказания используется статистика, т. н. BHT кеш, который определяет какое из направлений ветвления будет более вероятным.

DYNAMIC_TARGET — использует для предсказания т. н. «целевой буфер ветвления с прямым отображением» (BTB) в ступени Fetch, который сохраняет значение регистра PC, где расположена инструкция ветвления, значение PC по которому был осуществлен переход и два бита истории/вероятности. Это наиболее эффективный вариант предсказания ветвлений, так как если предсказание угадано, то никаких «штрафных» тактов не происходит. Существенным недостатком является очень длинная комбинационная цепочка тянущаяся от кеша предсказаний до регистра счетчика команд, проходящая через интерфейс ветвлений. Эта комбинационная цепочка существенно ограничивает максимальную тактовую частоту ядра.

На этом я закончу обзор плагинов вычислительного ядра VexRiscv, желающие узнать больше — могут почерпнуть информацию из документации, расположенной в репозитории этого проекта, ссылки на которую я приводил уже несколько раз выше по тексту.

16. Эксперименты с ядром VexRiscv и СнК Murax

Теперь, когда мы немного ознакомились с внутренним устройством вычислительного ядра VexRiscv, настало время немного поэкспериментировать с различными параметрами ядра VexRiscv и СнК Murax, то есть начать его модифицировать под свои нужны.

Далее я буду последовательно модифицировать код мастер репозитория VexRiscv, демонстрируя как действовал я, добавляя новые возможности в СнК и постепенно адаптируя его под поставленные задачи. Все внесенные мной изменения можно получить из отдельного репозитория на Github-е: по ссылке.

16.1 Оптимизация на примере плагина RegFilePlugin

Напомню, что у плагина RegFilePlugin имеется параметр, позволяющий задавать тип используемой памяти для организации регистрового файла. В СнК Murax по умолчанию используется синхронный вариант построения регистров, т. е. regFileReadyKind установлена в значение SYNC. Так как микросхема ПЛИС Lattice ECP5 имеет распределенные блоки двухпортовой статической памяти, из которых можно соорудить асинхронный регистровый файл, то резонно проверить насколько это может быть (или не быть) эффективным.

Отредактируем файл Murax.scala — найдем в нем добавление плагина, и заменим строку кода:

new RegFilePlugin( regFileReadyKind = plugin.SYNC, zeroBoot = false ),

на строку:

new RegFilePlugin( regFileReadyKind = plugin.ASYNC, zeroBoot = false ),

Запустим пересборку проекта командой make и понаблюдаем за статистикой утилизируемых ресурсов и рассчитываемых максимальных значений тактовых частот. Вот что мы должны увидеть:

Для режима ASYNC:

Info: Device utilisation: .. Info: TRELLIS_FF: 1325/24288 5% Info: TRELLIS_COMB: 2284/24288 9% Info: TRELLIS_RAMW: 36/ 3036 1% Info: Max frequency for clock 'io_clk2574.47 MHz (PASS at 25.00 MHz) Info: Max frequency for clock '" class="formula inline">glbnetTRELLIS_IO_IN': 128.97 MHz (PASS at 12.00 MHz)

Сравним эти же показатели для режима SYNC который используется по умолчанию:

Info: TRELLIS_FF: 1379/24288 5% Info: TRELLIS_COMB: 2346/24288 9% Info: TRELLIS_RAMW: 36/ 3036 1% Info: Max frequency for clock 'io_clk2569.80 MHz (PASS at 25.00 MHz) Info: Max frequency for clock '" class="formula inline">glbnetTRELLIS_IO_IN': 149.30 MHz (PASS at 12.00 MHz)

Видно, что в режиме ASYNC уменьшился расход Flip-Flop триггеров и комбинационных ячеек LUT-4. Также видно, что максимально допустимая частота для основного тактового сигнала io_clk25 существенно подросла — с 69.80 МГц до 74.47. МГц. Это означает, что мы, теоретически, имеем возможность увеличить частоту тактирования ядра до 74 МГц или даже немного выше! Это можно сделать, не изменяя кварцевого осциллятора, путем преобразования частоты с помощью встроенного в микросхему ПЛИС блока PLL.

16.2 Увеличиваем тактовую частоту ядра используя встроенный PLL

Если кратко, то PLL или «Phase-locked Loop» («Фазовая автоподстройка частоты», «ФАПЧ») это такой блок аппаратуры, который, используя ряд аналоговых ухищрений, позволяет делить и умножать тактовые частоты в определенных пределах и с определенной точностью. Микросхема ПЛИС Lattice ECP5 содержит два таких аппаратных блока, которые называются EHXPLLL. Тулчейн Yosys поддерживает эти блоки, а значит, мы можем задействовать один из них для преобразования частоты, поступающей от кварцевого осциллятора распаянного на плате «Карно» номиналом 25.0 МГц в (почти) любую другую частоту. В этом примере я продемонстрирую, как добавить PLL, настроить его, получить на выходе тактовый сигнал частотой 75.0 МГц и тактировать от него СнК Murax и вычислительное ядро в его составе.

PLL — это достаточно сложный блок аппаратуры, имеющий ряд параметров, изменяя которые можно получать разные характеристики выходного тактового сигнала. Чтобы облегчить работу дизайнеру, в составе тулчейна Yosys имеется утилита ecppll, задав которой пару исходных параметров (значения частоты входного и выходного сигнала), можно получить код на языке Verilog. Этот код при синтезе с помощью Yosys подключит и задействует один из аппаратных блоков EHXPLLL.

Запустим ecppll со следующими параметрами:

rz@devbox:~/VexRiscv/scripts/Murax/Karnix$ ecppll --clkin_name in_clk25 -i 25 --clkout0_name out_clk75 -o 75 -f pll25to75.v Pll parameters: Refclk divisor: 1 Feedback divisor: 3 clkout0 divisor: 8 clkout0 frequency: 75 MHz VCO frequency: 600

Здесь мы указываем утилите номиналы входной и выходной частоты, а также наименования сигнальных линий для входа и выхода. Утилита ecppll сформирует и запишет код на языке Verilog для модуля PLL, с использованием встроенного блока EHXPLLL, в файл pll25to75.v.

Посмотрим на его содержимое:

pll25to75.v

// diamond 3.7 accepts this PLL // diamond 3.8-3.9 is untested // diamond 3.10 or higher is likely to abort with error about unable to use feedback signal // cause of this could be from wrong CPHASE/FPHASE parameters module pll ( input in_clk25, // 25 MHz, 0 deg output out_clk75, // 75 MHz, 0 deg output locked ); (* FREQUENCY_PIN_CLKI="25" *) (* FREQUENCY_PIN_CLKOP="75" *) (* ICP_CURRENT="12" *) (* LPF_RESISTOR="8" *) (* MFG_ENABLE_FILTEROPAMP="1" *) (* MFG_GMCREF_SEL="2" *) EHXPLLL #( .PLLRST_ENA("DISABLED"), .INTFB_WAKE("DISABLED"), .STDBY_ENABLE("DISABLED"), .DPHASE_SOURCE("DISABLED"), .OUTDIVIDER_MUXA("DIVA"), .OUTDIVIDER_MUXB("DIVB"), .OUTDIVIDER_MUXC("DIVC"), .OUTDIVIDER_MUXD("DIVD"), .CLKI_DIV(1), .CLKOP_ENABLE("ENABLED"), .CLKOP_DIV(8), .CLKOP_CPHASE(4), .CLKOP_FPHASE(0), .FEEDBK_PATH("CLKOP"), .CLKFB_DIV(3) ) pll_i ( .RST(1'b0), .STDBY(1'b0), .CLKI(io_clk25), .CLKOP(clk75), .CLKFB(clk75), .CLKINTFB(), .PHASESEL0(1'b0), .PHASESEL1(1'b0), .PHASEDIR(1'b1), .PHASESTEP(1'b1), .PHASELOADREG(1'b1), .PLLWAKESYNC(1'b0), .ENCLKOP(1'b0), .LOCK(locked) ); endmodule

Видно, что утилита ecppll произвела расчет значений большого числа параметров и подставила их в модуль EHXPLLL. Описание всех параметров доступно в документации на микросхему, но рассчитать их значения вручную будет не просто.

Теперь осталось подключить этот файл в toplevel.v и произвести коммутацию тактовых сигналов: внешний сигнал io_clk25 необходимо подать на вход in_clk25 модуля pll, а выходной сигнал out_clk75 через дополнительный проводник clk75 подсоединить к сигналу тактирования mainClk модуля Murax. На Verilog-е это выглядит так:

toplevel.v

`timescale 1ns / 1ps `include "pll25to75.v" module toplevel( input io_clk25, input [3:0] io_key, output [3:0] io_led, input io_core_jtag_tck, output io_core_jtag_tdo, input io_core_jtag_tdi, input io_core_jtag_tms, output io_uart_debug_txd, input io_uart_debug_rxd ); assign io_led[0] = io_gpioA_write[0]; assign io_led[1] = io_gpioA_write[1]; assign io_led[2] = io_gpioA_write[2]; assign io_led[3] = io_gpioA_write[3]; wire [31:0] io_gpioA_read; wire [31:0] io_gpioA_write; wire [31:0] io_gpioA_writeEnable; assign io_gpioA_read[0] = io_key[0]; assign io_gpioA_read[1] = io_key[1]; assign io_gpioA_read[2] = io_key[2]; assign io_gpioA_read[3] = io_key[3]; wire clk75; pll i_pll(.in_clk25(io_clk25), .out_clk75(clk75)); Murax murax ( .io_asyncReset(io_key[3]), //.io_mainClk (io_clk25), .io_mainClk (clk75), .io_jtag_tck(io_core_jtag_tck), .io_jtag_tdi(io_core_jtag_tdi), .io_jtag_tdo(io_core_jtag_tdo), .io_jtag_tms(io_core_jtag_tms), .io_gpioA_read (io_gpioA_read), .io_gpioA_write (io_gpioA_write), .io_gpioA_writeEnable(io_gpioA_writeEnable), .io_uart_txd(io_uart_debug_txd), .io_uart_rxd(io_uart_debug_rxd) ); endmodule

Далее, укажем программе «hello_world» на тот факт, что тактовая частота процессора изменилась, это требуется для правильного расчета задержек в программе. Для этого в файле ./src/main/c/murax/hello_world/src/murax.h заменим значение константы SYSTEM_CLOCK_HZ на 75000000L и выполним пересборку Си программы:

rz@devbox:~/VexRiscv/src/main/c/murax/hello_world$ make clean && make

Не забываем установить regFileReadyKind = plugin.ASYNC для плагина RegFilePlugin (см. предыдущую главу), а также указать для СнК Murax новую частоту в параметре coreFrequency = 75 Mhz, после чего запускаем сборку проекта и наблюдаем:

rz@devbox:~/VexRiscvWithKarnix/scripts/Murax/Karnix$ make ... Info: Device utilisation: Info: TRELLIS_IO: 15/ 197 7% Info: DCCA: 2/ 56 3% Info: DP16KD: 48/ 56 85% ... Info: EHXPLLL: 1/ 2 50% ... Info: TRELLIS_FF: 1325/24288 5% Info: TRELLIS_COMB: 2270/24288 9% Info: TRELLIS_RAMW: 36/ 3036 1% ... Info: Routing globals... Info: routing clock net io_core_jtag_tckInfo: routing clock net $glbnet" class="formula inline">clk75 using global 1 ... Info: Max frequency for clock 'clk75': 75.55 MHz (PASS at 75.00 MHz) Info: Max frequency for clock 'io_core_jtag_tck$TRELLIS_IO_IN': 124.66 MHz (PASS at 12.00 MHz)

Хохо! Наш дизайн прошел контроль STA по самому краешку — 75.00 МГц из 75.55 МГц разрешенных.

Подключаем плату «Карно», загружаем битстрим командой make upload и наблюдаем за тем, как «пляшут» светодиоды в три раза быстрее прежнего.

16.3 Увеличиваем производительность инструкций сдвига

В главе «15.3 Плагины вычислительного ядра VexRiscv» я упоминал о том, что автор VexRiscv снабдил своё вычислительное ядро двумя реализациями (двумя плагинами) инструкций побитового сдвига: LightShifterPlugin — многотактовая реализация, выполняющая сдвиг на N бит за N тактов, и FullBarrelShifterPlugin — полная реализация («бочковой сдвигатель»), выполняющая операции сдвига на N бит за 1 такт. Очевидно, что последний является более интересным с точки зрения производительности, но имеет существенный недостаток — потребляет большое количество логических элементов и имеет достаточно длинную цепочку комбинационной логики (длинный критический путь), что может существенно увеличить время работы стадии конвейера Execute и сократить максимальную частоту тактирования ядра. По умолчанию в СнК Murax используется облегченный вариант, сделано это с целью экономии ресурсов микросхемы и демонстрации минимально возможного варианта. Давайте же перенастроим наше вычислительное ядро на использование полной реализации сдвигателя и посмотрим, во что это выливается.

Прежде чем мы приступим к модификации аппаратуры, нам необходимо добавить небольшой код на языке Си в программу «hello_world», для измерения производительности инструкций сдвига. Для этого воспользуемся уже имеющимся в СнК Murax блоком таймеров MuraxApb3Timer, который состоит из двух 16-ти битных таймеров timerA и timerB и одного общего 16-ти битного прескейлера (делителя частоты). Проинициализируем прескейлер так, чтобы таймер вел расчет в миллисекундах, т. е. занесем в прескейлер значение (SYSTEM_CLOCK_HZ / 1000000 - 1). Далее, добавим в код функции delay() ассемблерную инструкцию сдвига на 16, а время исполнения функции delay() будем измерять одним из таймеров и выводить в порт UART в виде шестнадцатеричного числа.

Файл main.c программы «hello_world» примет следующие изменения:

main.c

void delay(uint32_t loops){ for(int i=0;i<loops;i++){ //int tmp = GPIO_A->OUTPUT; asm volatile ("slli t1,t1,0x10"); } } void printhex(unsigned int number){ unsigned int mask = 0xf0000000; static char hex_digits[11] = {0,0,0,0,0,0,0,0,'\r','\n','\0'}; for(int i = 0; i < 8; i++) { int digit = (number & mask) >> 4*(7-i); if(digit < 0x0a) hex_digits[i] = digit + 0x30; else hex_digits[i] = (digit - 0x0a) + 'A'; mask = mask >> 4; } print(hex_digits); } const int nleds = 4; const int nloops = 1000000; TIMER_PRESCALER->LIMIT = 0xFFFF; // Set max possible clock divider while(1){ unsigned int shift_time; println("Hello world, this is VexRiscv!"); for(unsigned int i=0;i<nleds-1;i++){ GPIO_A->OUTPUT = 1<<i; TIMER_A->CLEARS_TICKS = 0x00020002; TIMER_A->LIMIT = 0xFFFF; delay(nloops); shift_time = TIMER_A->VALUE; } for(unsigned int i=0;i<nleds-1;i++){ GPIO_A->OUTPUT = (1<<(nleds-1))>>i; delay(nloops); } printhex(shift_time); }

Жирным шрифтом показаны новые или измененные строки кода. Запускаем сборку и проверяем что у нас получилось:

rz@devbox:~/VexRiscv/scripts/Murax/Karnix$ make clean && make

Если все прошло успешно, т. е. в программе нет синтаксических ошибок, то произойдет компиляция, синтез и полная сборка битстрима.

Как обычно, подключаем плату «Карно» и загружаем битстрим командой make upload. После этого подключаемся к отладочному UART с помощью терминала minicom и наблюдаем сообщения вида:

rz@butterfly:~ % sudo minicom -b 115200 -D /dev/ttyU1 Hello world, this is VexRiscv! 000001AC Hello world, this is VexRiscv! 000001AC Hello world, this is VexRiscv! 000001AB Hello world, this is VexRiscv! 000001AB

Выводимое шестнадцатеричное число — это количество отсчетов таймера, которое произошло за момент выполнения модифицированной функции delay(). Мы можем приближенно пересчитать во сколько тактов исполняется одна итерация цикла внутри этой функции: (0xFFFF+1) * 0x01AC / 1000000 = 28 тактов на цикл. Где 0xFFFF — делитель (прескейлер), а 1000000 число итераций цикла.

Теперь модифицируем СнК Murax и вместо LightShifterPlugin подключим FullBarrelShifterPlugin. Для этого отредактируем файл Murax.scala, найдем в нём переменную cpuPlugins, которой присваивается инициализированный массив плагинов, закомментируем плагин LightShifterPlugin и добавим FullBarrelShifterPlugin:

cpuPlugins = ArrayBuffer( new IBusSimplePlugin( ... ), new SrcPlugin( ... ), //new LightShifterPlugin, new FullBarrelShifterPlugin, new HazardSimplePlugin( ... ),

Еще раз пересоберем проект командой make clean && make, по окончанию сборки загрузим битстрим командой make upload, подключим minicom и наблюдаем сообщения вида:

Hello world, this is VexRiscv! 000000C7 Hello world, this is VexRiscv! 000000C7 Hello world, this is VexRiscv! 000000C6 Hello world, this is VexRiscv! 000000C6 Hello world, this is VexRiscv! 000000C7

Видно, что число отсчетов таймера значительно сократилось, а значит функция delay() стала работать быстрее. Пересчитаем в количество тактов: (0xFFFF+1) * 0x00C7 / 1000000 = 13. Т.е. время исполнения одной итерации цикла внутри delay() сократилось на 15 тактов. И это полностью соответствует теории: машинная команда slli t1,t1,0x10 которая составляет тело цикла, выполняет сдвиг регистра t1 (временный регистр #1) влево на 16 бит. В первом случае она исполняется за 16 тактов, во втором — за один такт, т. е. на 15 тактов быстрее!

А сейчас посмотрим на статистику, полученную при синтезе.

При использовании плагина LightShifterPlugin, выполняющего облегченный вариант сдвига на N бит за N ��актов:

Info: Device utilisation: Info: TRELLIS_IO: 15/ 197 7% Info: DCCA: 2/ 56 3% Info: DP16KD: 48/ 56 85% ... Info: EHXPLLL: 1/ 2 50% ... Info: TRELLIS_FF: 1325/24288 5% Info: TRELLIS_COMB: 2255/24288 9% Info: TRELLIS_RAMW: 36/ 3036 1% Info: Max frequency for clock '$glbnet$clk75': 77.29 MHz (PASS at 75.00 MHz) Info: Max frequency for clock '$glbnet$io_core_jtag_tck$TRELLIS_IO_IN': 118.46 MHz (PASS at 12.00 MHz)

При использовании «полного бочкового сдвигателя», реализуемого плагином FullBarrelShifterPlugin, получаем следующую статистику:

Info: Device utilisation: Info: TRELLIS_IO: 15/ 197 7% Info: DCCA: 2/ 56 3% Info: DP16KD: 48/ 56 85% ... Info: EHXPLLL: 1/ 2 50% ... Info: TRELLIS_FF: 1353/24288 5% Info: TRELLIS_COMB: 2447/24288 10% Info: TRELLIS_RAMW: 36/ 3036 1% Info: Max frequency for clock 'clk75': 79.73 MHz (PASS at 75.00 MHz) Info: Max frequency for clock 'io_core_jtag_tck$TRELLIS_IO_IN': 124.01 MHz (PASS at 12.00 MHz)

Такое поведение тулчейна мне объяснить сложно. Моё предположение состоит в том, что код «бочкового сдвигателя» хорошо оптимизируется и синтезатором и плейсером. Отчасти это подтверждается статистикой, полученной после выполнения размещения (до оптимизации маршрутов) — уже на этом этапе видно, что «бочковой сдвигатель» более эффективен с точки зрения STA.

Статистика до оптимизации:

Для LightShifterPlugin:

Info: Max frequency for clock '$glbnet$clk75': 49.10 MHz (FAIL at 75.00 MHz) Info: Max frequency for clock '$glbnet$io_core_jtag_tck$TRELLIS_IO_IN': 156.32 MHz (PASS at 12.00 MHz)

Для FullBarrelShifterPlugin:

Info: Max frequency for clock '$glbnet$clk75': 51.05 MHz (FAIL at 75.00 MHz) Info: Max frequency for clock '$glbnet$io_core_jtag_tck$TRELLIS_IO_IN': 124.73 MHz (PASS at 12.00 MHz)

17. Добавляем свои аппаратные блоки (IP-блоки)

Конфигурация СнК Murax и ядра VexRiscv в его составе, которая представлена по умолчанию в репозитории VexRiscv, служит для целей демонстрации и имеет очень ограниченные возможности. Настало время посмотреть, как можно расширить функционал Murax и создать свою СнК, подходящую для решения широкого спектра практических задач.

17.1 Микросекундный машинный таймер MTIME

Для дальнейшего исследования и экспериментов нам понадобится микросекундный машинный таймер, который монотонно возрастает и никогда не переполняется (или делает это очень редко). С таким таймером удобно работать при проведении измерений производительности, как, например, в предыдущей главе. Добавить такой таймер не сложно, язык SpinalHDL уже содержит все необходимые примитивы, требуется только сложить их вместе и подвязать получившийся IP-блок к периферийной шине Apb3. Сейчас мы это и проделаем.

Схема нашего машинного микросекундного таймера будет содержать два регистра-счетчика. Первый счетчик, counter размером 8 бит, будет отсчитывать число тактов до полной микросекунды, опираясь на значение параметра clockMHz, который будет задаваться извне и содержать значение частоты системного клока в мегагерцах. В нашем случае, при частоте clockMHz = 75.0 МГц, этот счетчик будет принимать максимальное значение 75 - 1 = 74. Второй регистр-счетчик, microCounter размерностью 32 бита, это собственно наш микросекундный таймер, который будет прирастать на единицу каждый раз когда первый счетчик достигает значения clockMHz — 1. Сигнал io.micros будет ссылаться на значение счетчика microCounter и представлять внешний интерфейс (сигнал) нашего машинного таймера. Вот как это выглядит на языке SpinalHDL:

package mylib import spinal.core._ import spinal.lib._ import spinal.lib.bus.amba3.apb._ import spinal.lib.bus.misc._ case class MachineTimer(clockMHz: Int = 25) extends Component { val io = new Bundle { val micros = out UInt(32 bits) } val counter = Reg(UInt(8 bits)) val microCounter = Reg(UInt(32 bits)) io.micros := microCounter counter := counter + 1 when (counter === clockMHz - 1) { counter := 0; microCounter := microCounter + 1 } def driveFrom(busCtrl : BusSlaveFactory, baseAddress : Int = 0) () = new Area { busCtrl.read(io.micros, baseAddress) } }

Метод driveFrom() обеспечивает привязку интерфейсного сигнала io.micros к шине BusSlaveFactory при чтении слова по адресу baseAddress. BusSlaveFactory является внешней шиной для моста Apb3, смотрящей в сторону периферии, а наше новое устройство будет являться слэйвом на этой шине.

Для привязки нашего нового компонента потребуется создать еще один, оберточный, компонент Apb3MachineTimer - он будет инкапсулировать в себя компонент MachineTimer и интерфейсный класс Apb3SlaveFactory. Apb3SlaveFactory является интерфейсом для моста Apb3. Оберточный компонент также будет содержать одну строку кода, обеспечивающую связь между новым компонентом и Apb3. Код для этого оберточного компонента на SpinalHDL выглядит следующим образом:

case class Apb3MachineTimer(clockMHz : Int = 25) extends Component { val io = new Bundle { val apb = slave(Apb3(Apb3Config(addressWidth = 8, dataWidth = 32))) } val busCtrl = Apb3SlaveFactory(io.apb) val mtCtrl = MachineTimerCtrl(clockMHz) mtCtrl.driveFrom(busCtrl)() // connect component to the bus }

Строго говоря, этот оберточный компонент не является обязательным, но тогда нам пришлось бы вытащить этот код на верхний уровень, в Murax, что не очень эстетично.

Разместим весь этот код в одном файле ./src/main/scala/mylib/MachineTimer.scala, при этом подкаталог ./src/main/scala/mylib потребуется создать.

Теперь, для того чтобы подключить наш новый компонент к шине Apb3 внутри СнК Murax, наравне с другой периферией, необходимо добавить его в ассоциативный список, содержащийся в переменной apbMapping, указав адрес привязки 0xB0000. Вставим выделенный жирным код сразу после подключения уже существующего таймера:

val timer = new MuraxApb3Timer() timerInterrupt setWhen(timer.io.interrupt) apbMapping += timer.io.apb -> (0x20000, 4 kB) val machineTimer = Apb3MachineTimer(coreFrequency.toInt / 1000000) apbMapping += machineTimer.io.apb -> (0xB0000, 4 kB)

Таким образом, регистр нашего микросекундного таймера будет доступен из программы при чтении 32-х битного слова по адресу: 0xF0000000 + 0xB0000 = 0xF00B0000. Для того, чтобы при сборке SBT нашел код нашего нового компонента, поможем ему в этом, добавив в заголовке файла Murax.scala следующу строку:

import mylib.Apb3MachineTimer

Чтобы проверить, как работает созданный нами машинный микросекундный таймер, добавим в файл src/murax.h макро MTIME для доступа к регистру:

#define MTIME (*(volatile unsigned long*)(0xF00B0000))

А в код программы «hello_world» добавим измерение времени выполнения функции delay() с помощью микросекундного таймера. Модифицированный Си код в файле src/main.c приведен ниже:

while(1){ unsigned int shift_time; unsigned int t1, t2; println("Hello world, this is VexRiscv!"); for(unsigned int i=0;i<nleds-1;i++){ GPIO_A->OUTPUT = 1<<i; TIMER_A->CLEARS_TICKS = 0x00020002; TIMER_A->LIMIT = 0xFFFF; t1 = MTIME; delay(nloops); t2 = MTIME; shift_time = TIMER_A->VALUE; } for(unsigned int i=0;i<nleds-1;i++){ GPIO_A->OUTPUT = (1<<(nleds-1))>>i; delay(nloops); } printhex(shift_time); printhex(t2 - t1); }

Как обычно, выполняем сборку проекта командой make clean && make, устраняем все синтаксические ошибки и опечатки, подключаем плату «Карно» и загружаем полученный битстрим. Запускаем эмулятор терминала minicom и наблюдаем в порту следующие строки:

Hello world, this is VexRiscv! 000000C7 0002A516 Hello world, this is VexRiscv! 000000C6 0002A515 Hello world, this is VexRiscv! 000000C6 0002A515

Здесь первое число — это измерение числа тактов (умноженное на 65536), выполненное таймером TIMER_A, а второе число — результат замеров с помощью микросекундного таймера. Число 0002A515 есть не что иное как 173333 микросекунд, которые требуются для выполнения функции delay(1000000).

Теперь, когда у нас есть микросекундный таймер, мы можем легко соорудить сервисные функции delay_us() и delay_ms(), осуществляющие задержку исполнения программы на заданное количество микро- и миллисекунд:

void delay_us(unsigned int us){ unsigned int t = MTIME; while(MTIME - t < us); } void delay_ms(unsigned int ms){ for(int i = 0; i < ms; i++) delay_us(1000); }

17.2 Подключаем микросхему SRAM

На плате «Карно» имеется распаянная и подключенная к ПЛИС микросхема статической памяти K6R4016V1D-10 объемом 16x256 КБ (512 КБ) и было бы очень неплохо задействовать эту память в своих программах, исполняемых на синтезированном ядре. Эта микросхема имеет стандартный набор сигнальных линий:

A0-A9 (линии выбора строки) и A10-A17 (линии выбора столбца) вместе формируют адрес 16-битного слова, т. е. микросхема содержит всего 262144 слов по 16 бит.

D0-D15 — линии данных.

#CS — сигнал выбора микросхемы, лог «0» — выбрана.

#WE — сигнал разрешения записи в память, лог «0» - запись, лог «1» - чтение.

#OE — сигнал разрешения выставить данные на выходную шину данных. Лог «0» - данные на выходе активны, лог «1» - линии данных находятся в состоянии высокого импеданса.

#LB — сигнал, разрешающий запись младшего байта.

#UB — сигнал, разрешающий запись старшего байта.

Опишем эти сигнальные линии в LPF файле, чтобы ими можно было пользоваться, добавим в файл karnix_cabga256.lpf следующие строки:

Дополнительные сигналы io_sram к karnix_cabga256.lpf

LOCATE COMP "io_sram_cs" SITE "H15"; # SRAM #CS IOBUF PORT "io_sram_cs" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_we" SITE "K14"; # SRAM #WE IOBUF PORT "io_sram_we" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_oe" SITE "J14"; # SRAM #OE IOBUF PORT "io_sram_oe" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_bhe" SITE "J16"; # SRAM #BHE IOBUF PORT "io_sram_bhe" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_ble" SITE "J15"; # SRAM #BLE IOBUF PORT "io_sram_ble" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[0]" SITE "L16"; # SRAM D00 IOBUF PORT "io_sram_dat[0]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[1]" SITE "L15"; # SRAM D01 IOBUF PORT "io_sram_dat[1]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[2]" SITE "M16"; # SRAM D02 IOBUF PORT "io_sram_dat[2]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[3]" SITE "M15"; # SRAM D03 IOBUF PORT "io_sram_dat[3]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[4]" SITE "K13"; # SRAM D04 IOBUF PORT "io_sram_dat[4]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[5]" SITE "K12"; # SRAM D05 IOBUF PORT "io_sram_dat[5]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[6]" SITE "L13"; # SRAM D06 IOBUF PORT "io_sram_dat[6]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[7]" SITE "L12"; # SRAM D07 IOBUF PORT "io_sram_dat[7]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[8]" SITE "N16"; # SRAM D08 IOBUF PORT "io_sram_dat[8]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[9]" SITE "P15"; # SRAM D09 IOBUF PORT "io_sram_dat[9]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[10]" SITE "L14"; # SRAM D10 IOBUF PORT "io_sram_dat[10]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[11]" SITE "M14"; # SRAM D11 IOBUF PORT "io_sram_dat[11]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[12]" SITE "P16"; # SRAM D12 IOBUF PORT "io_sram_dat[12]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[13]" SITE "R16"; # SRAM D13 IOBUF PORT "io_sram_dat[13]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[14]" SITE "M13"; # SRAM D14 IOBUF PORT "io_sram_dat[14]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_dat[15]" SITE "N14"; # SRAM D15 IOBUF PORT "io_sram_dat[15]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[0]" SITE "N13"; # SRAM A00 IOBUF PORT "io_sram_addr[0]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[1]" SITE "P14"; # SRAM A01 IOBUF PORT "io_sram_addr[1]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[2]" SITE "R15"; # SRAM A02 IOBUF PORT "io_sram_addr[2]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[3]" SITE "T15"; # SRAM A03 IOBUF PORT "io_sram_addr[3]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[4]" SITE "P13"; # SRAM A04 IOBUF PORT "io_sram_addr[4]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[5]" SITE "R14"; # SRAM A05 IOBUF PORT "io_sram_addr[5]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[6]" SITE "R13"; # SRAM A06 IOBUF PORT "io_sram_addr[6]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[7]" SITE "T14"; # SRAM A07 IOBUF PORT "io_sram_addr[7]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[8]" SITE "R12"; # SRAM A08 IOBUF PORT "io_sram_addr[8]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[9]" SITE "T13"; # SRAM A09 IOBUF PORT "io_sram_addr[9]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[10]" SITE "M12"; # SRAM A10 IOBUF PORT "io_sram_addr[10]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[11]" SITE "N12"; # SRAM A11 IOBUF PORT "io_sram_addr[11]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[12]" SITE "M11"; # SRAM A12 IOBUF PORT "io_sram_addr[12]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[13]" SITE "N11"; # SRAM A13 IOBUF PORT "io_sram_addr[13]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[14]" SITE "P11"; # SRAM A14 IOBUF PORT "io_sram_addr[14]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[15]" SITE "P12"; # SRAM A15 IOBUF PORT "io_sram_addr[15]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[16]" SITE "K16"; # SRAM A16 IOBUF PORT "io_sram_addr[16]" IO_TYPE=LVCMOS33; LOCATE COMP "io_sram_addr[17]" SITE "K15"; # SRAM A17 IOBUF PORT "io_sram_addr[17]" IO_TYPE=LVCMOS33;

И передадим эти сигналы из модуля toplevel в модуль Murax в оберточном файле toplevel.v, как показано в выдержке ниже:

Дополнительные сигналы io_sram к toplevel.v

module toplevel( input io_clk25, input [3:0] io_key, output [3:0] io_led, input io_core_jtag_tck, output io_core_jtag_tdo, input io_core_jtag_tdi, input io_core_jtag_tms, output io_uart_debug_txd, input io_uart_debug_rxd, output io_sram_cs, // #CS output io_sram_we, // #WE output io_sram_oe, // #OE output io_sram_bhe, // #UB output io_sram_ble, // #LB output [17:0] io_sram_addr, // A0-A17 inout [15:0] io_sram_dat // D0-D15 ); ... Murax murax ( .io_asyncReset(io_key[3]), //.io_mainClk (io_clk25), .io_mainClk (clk75), .io_jtag_tck(io_core_jtag_tck), .io_jtag_tdi(io_core_jtag_tdi), .io_jtag_tdo(io_core_jtag_tdo), .io_jtag_tms(io_core_jtag_tms), .io_gpioA_read (io_gpioA_read), .io_gpioA_write (io_gpioA_write), .io_gpioA_writeEnable(io_gpioA_writeEnable), .io_uart_txd(io_uart_debug_txd), .io_uart_rxd(io_uart_debug_rxd), .io_sram_cs(io_sram_cs), .io_sram_we(io_sram_we), .io_sram_oe(io_sram_oe), .io_sram_bhe(io_sram_bhe), .io_sram_ble(io_sram_ble), .io_sram_addr(io_sram_addr), .io_sram_dat(io_sram_dat) );

17.2.1 Разрабатываем контроллер SRAM

А теперь подумаем вот о чем. У нас есть типовой набор сигналов для интерфейса к микросхеме SRAM. Чтобы не таскать далее по всему коду эту пачку сигналов, имеет смысл описать её как комплексный сигнал, и тогда нам будет достаточно передавать одну переменную. На SpinalHDL такой комплексный сигнал можно описать следующим образом.

Создадим класс SramInterface с двойным наследованием: от класса Bundle (сложная структура сигналов) и от класса IMasterSlave. Последний позволяет изменять направления действия сигналов в зависимости от амплуа компонента, который будет использовать наш интерфейсный класс: «мастер» (ведущий) или «слэйв» (ведомый).

Так как наш интерфейс по большей части будет выступать в амплуа «мастер», то мы переопределим абстрактный метод asMaster(), он будет использовать сервисные функции out() и inout(), унаследованные от класса Bundle, для изменения направленности сигналов.

Для того, чтобы сделать наш интерфейс чуть более гибким, нам необходимо добавить к нему пару параметров, а именно — параметры, задающие размерность шины адреса и шины данных. Сделаем это с помощью простой структуры SramLayout:

case class SramLayout(addressWidth: Int, dataWidth : Int){ def bytePerWord = dataWidth/8 def capacity = BigInt(1) << addressWidth }

Тогда описание нашего интерфейсного класса примет следующий вид:

case class SramInterface(g : SramLayout) extends Bundle with IMasterSlave{ val addr = inout(Analog(Bits(g.addressWidth bits))) val dat = inout(Analog(Bits(g.dataWidth bits))) val cs = Bool val we = Bool val oe = Bool val ble = Bool val bhe = Bool override def asMaster(): Unit = { out(cs,we,oe,ble,bhe) inout(dat, addr) } }

Поместим все это дело в файл ./src/main/scala/mylib/Sram.scala, то есть в тот же каталог, где располагается ранее созданный компонент MachineTimer. В заголовке файла также укажем имя пакета и перечень используемых библиотек:

package mylib import spinal.core._ import spinal.lib._ import spinal.lib.bus.simple._ import spinal.lib.io.TriState

Теперь можно описать комплексный сигнал sram на входе компонента Murax, представляющего синтезируемый СнК. Отредактируем файл Murax.scala следующим образом:

Во-первых, подключим наши новые классы, добавив в заголовок следующую строку:

import mylib.Apb3MachineTimer import mylib.{SramInterface,SramLayout,PipelinedMemoryBusSram}

Во-вторых, найдем описание внешних сигналов компонента Murax и добавим новый сигнал sram, сразу указав параметры шин адреса и данных:

case class Murax(config : MuraxConfig) extends Component{ import config._ val io = new Bundle { //Clocks / reset val asyncReset = in Bool() val mainClk = in Bool() //Main components IO val jtag = slave(Jtag()) ... val sram = master(SramInterface(SramLayout(addressWidth = 18, dataWidth = 16))) }

С интерфейсом разобрались. Теперь нужно реализовать компонент «контроллера» микросхемы SRAM, который, с одной стороны, будет выступать «мастером» и взаимодействовать с микросхемой памяти через описанный выше интерфейс, а с другой — выступать в роли «слэйв» устройства на шине MainBus. Напомню, что шина MainBus является в СнК Murax основой для интерконнекта с его частями и определяется классом PipelinedMemoryBus. Тогда код «заготовки» нашего контроллера, назовем его PipelinedMemoryBusSram, будет выглядеть следующим образом:

case class PipelinedMemoryBusSram(pipelinedMemoryBusConfig: PipelinedMemoryBusConfig, sramLayout : SramLayout) extends Component{ val io = new Bundle{ val bus = slave(PipelinedMemoryBus(pipelinedMemoryBusConfig)) val sram = master(SramInterface(sramLayout)) } ... // здесь будет имплементация контроллера SRAM }

Настало время подумать о логике работы нашего контроллера микросхемы SRAM.

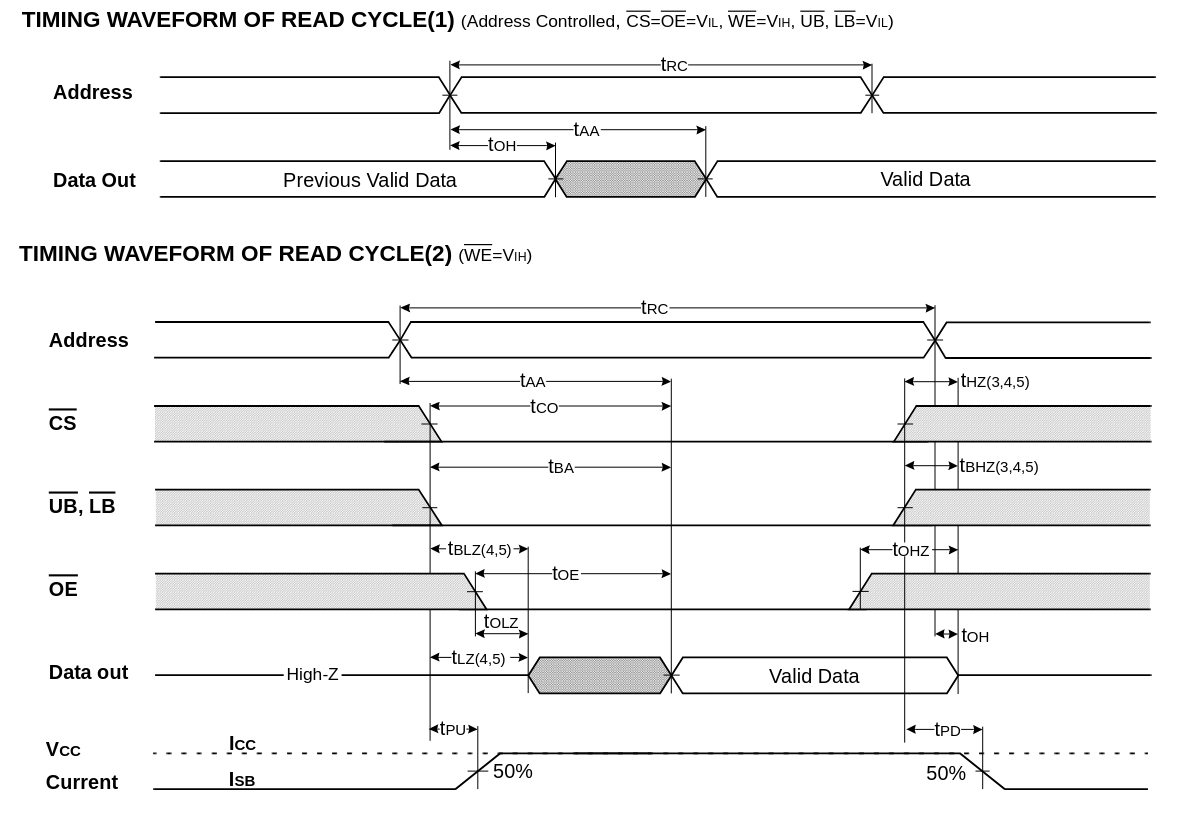

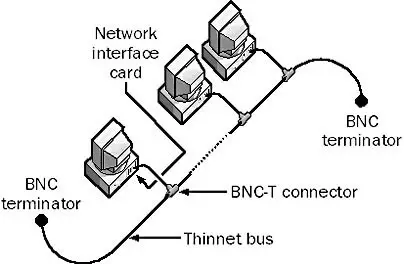

Для тех, кто не в курсе особенностей, микросхема статической памяти (Static Random Access Memory) работает асинхронно, то есть не имеет тактирования — чтение и запись в ячейки осуществляется после подачи на микросхему набора разрешающих сигналов (#CS — chip-select, #WE — write-enable, #OE - output enable) и занимает какое-то время. Это время, требуемое микросхеме на выполнения операции, обозначается в спецификации как «Read Cycle Time» (trc)и «Write Cycle Time» (twc). Заглянув в спецификацию на микросхему K6R4016V1D мы увидим, что оба этих параметра имеют одинаковое значение — от 10нс, а это означает, что данная микросхема способна выполнять почти 100 млн операций записи и чтения в секунду. Микросхема оперирует 16-ти битными словами, т. е. за одну операцию записывает или считывает по 16 бит данных, которые подаются или снимаются с шины данных (сигналы D0-D15), а адрес слова, которое будет записано или считано, предварительно подается на шину адреса (сигналы A0-A17).

Если посмотреть на временные диаграммы на рис. 28, то можно увидеть, что адрес подается с небольшим опережением сигналов разрешения, но если длительность удержания сигналов достаточно большая, то адрес можно подавать вместе с разрешающими сигналами. В нашем дизайне частота тактового сигнала составляет 75 МГц или иными словами, тактовый сигнал имеет длительность 13нс. Этого времени, теоретически, должно быть достаточно, чтобы осуществлять операции чтения и записи в микросхему SRAM за один такт, подавая все необходимые сигналы сразу. То есть за один системный такт мы могли бы читать или записывать по 16 бит данных в SRAM. Однако, опыт показал, что на частоте 60 МГц и выше, при чтении возникают множественный битфлипы (искажения данных), при этом запись на частоте 75 МГц производится без ошибок. Я не стал вдаваться в подробности почему так происходит, но пришел к выводу, что для надежного чтения каждого 16-битного слова в реальности потребуется два такта.

Вычислительное ядро VexRiscv является 32-х битным, а это означает, что ядро за один такт считывает или записывает в шину PipelinedMemoryBus слова размерностью 32 бита и тут возникает дополнительная сложность. Чтобы выполнять операции чтения/записи с данной микросхемой SRAM, нам потребуется разбивать операцию записи на две части (два такта), а операцию чтения — на четыре. При чтении придется «склеивать» полученный результат в 32-битное слово перед выдачей его в шину.

Еще один момент состоит в том, что вычислительное ядро может потребовать записать не все 32 б��та, а только часть из них, например младшие 8 бит (младший байт) или старшие 8 бит любого полуслова, или комбинацию из них. Для того, чтобы наш контроллер SRAM понял, какую именно часть данных требуется записать, шина PipelinedMemoryBus передает набор из четырех сигналов-масок io.bus.cmd.mask[3:0] — наличие лог «1» в соответствующем бите маске сигнализирует о том, что соответствующий байт (один из четырех байтов 32-х битного слова) требуется записать, а остальные оставить без изменения.

Таким образом, в реализации нашего контроллера SRAM вырисовывается автомат состояний, работающий по следующему алгоритму:

При записи в SRAM (io.bus.cmd.write === True):

Автомат начинает работу в состоянии #0, в котором он ожидает сигнала готовности io.bus.cmd.valid от шины.

Получив сигнал готовности, автомат устанавливает управляющие сигналы io.sram.oe = False и io.sram.we = False; параллельно с этим выставляет на шину адреса микросхемы io.sram.addr адрес младшего 16-ти битного слова, полученного с внешней шины io.bus.cmd.address; на шину данных микросхемы io.sram.dat - младшие 16 бит данных; на линии io.sram.ble и io.sram.bhe подает значения масок из io.bus.cmd.mask(0) и io.bus.cmd.mask(1) соответственно; и переводит автомат в состояние #1.

В состоянии #1 автомат выставляет на шину адреса io.sram.addr адрес старшего 16-ти битного слова; на шину данных io.sram.dat - старшие 16 бит данных; на линии io.sram.ble и io.sram.bhe подает значения масок io.bus.cmd.mask(2) и io.bus.cmd.mask(3) соответственно. В этом же состоянии автомат переводит своё состояние в #0 и сигнализирует о завершении выполнения операции установкой сигнала io.bus.cmd.ready в True.

Цикл записи требует всего два такта (два состояния).

При чтении из SRAM (io.bus.cmd.write === False) все становится немного сложнее:

Автомат так же начинает работу в состоянии #0 в котором он ожидает сигнала готовности io.bus.cmd.valid от шины.

Получив сигнал готовности, автомат устанавливает управляющие сигналы io.sram.oe = False, io.sram.we = True и выставляет на шину адреса io.sram.addr адрес младшего 16-ти битного слова, полученного с шины io.bus.cmd.address, а данные с шины io.sram.dat копирует во внутренний (временный) регистр rsp_data - в его младшие 16 бит, и переходит в состояние #1.

В состоянии #1 автомат продолжает удерживать на шине io.sram.addr адрес младшего 16-ти битного слова и продолжает копировать данные во внутренний регистр, т. е. выполняет пустой цикл и переходит в состояние #2.

В состоянии #2 автомат выставляет на шину адреса io.sram.addr адрес старшего 16-ти битного слова, полученного с шины io.bus.cmd.address, а данные с шины io.sram.dat копирует во внутренний регистр rsp_data, в его старшие 16 бит и переходит в состояние #3.

В состоянии #3 автомат продолжает удерживать на шине io.sram.addr адрес старшего 16-ти битного слова, продолжает копировать данные во внутренний регистр. При этом автомат в этом же цикле формируется сигнал завершения операции io.bus.cmd.ready в True, а также устанавливает сигнал готовности данных io.bus.rsp.valid.

Таким образом, цикл чтения требует четыре такта (четыре состояния автомата).

Здесь требуется сделать еще пару замечаний по работе алгоритма:

Выходной сигнал io.bus.rsp.valid должен буферизироваться через регистр (в нашем случае это будет регистр rsp_valid). Это требуется для того, чтобы разнести во времени сигналы io.bus.cmd.ready и io.bus.rsp.valid из-за особенностей реализации шины PipelinedMemoryBus. Если этого не сделать, то получив оба сигнала в одном такте шина остановится (перейдет в состояние STALL) и система прекратит работу.

Выходные данные при цикле чтении должны браться из временного регистра rsp_data и передаваться на шину io.bus.rsp.data.

При установке управляющих сигналов для микросхемы SRAM нужно учитывать, что все управляющие сигналы имеют инверсное значение (active low), т. е. эти сигналы требуется инвертировать.

Переведя описанный выше алгоритм на язык SpinalHDL, получим следующий код для контроллера SRAM, описываемого классом PipelinedMemoryBusSram:

Sram.scala

case class PipelinedMemoryBusSram(pipelinedMemoryBusConfig: PipelinedMemoryBusConfig, sramLayout : SramLayout) extends Component{ val io = new Bundle{ val bus = slave(PipelinedMemoryBus(pipelinedMemoryBusConfig)) val sram = master(SramInterface(sramLayout)) } val state = Reg(UInt(3 bits)) init(0) val rsp_data = Reg(Bits(pipelinedMemoryBusConfig.addressWidth bits)) init(0) val rsp_valid = Reg(Bool()) init(False) io.sram.cs := ~io.bus.cmd.valid io.sram.we := True io.sram.oe := True io.sram.bhe := True io.sram.ble := True io.bus.rsp.data := rsp_data; io.bus.rsp.valid := rsp_valid io.bus.cmd.ready := (state === 1 && io.bus.cmd.write) || (state === 3 && !io.bus.cmd.write) when (io.bus.cmd.valid) { when (io.bus.cmd.write) { // Write io.sram.we := False // active low when (state === 0) { // Write low 16 bits io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"0" io.sram.dat := io.bus.cmd.data(15 downto 0).asBits io.sram.ble := ~io.bus.cmd.mask(0) io.sram.bhe := ~io.bus.cmd.mask(1) state := 1 } otherwise { // Write high 16 bits io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"1" io.sram.dat := io.bus.cmd.data(31 downto 16).asBits io.sram.ble := ~io.bus.cmd.mask(2) io.sram.bhe := ~io.bus.cmd.mask(3) state := 0 } } otherwise { // Read io.sram.ble := False io.sram.bhe := False io.sram.oe := False when (state === 0) { io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"0" rsp_data(15 downto 0) := io.sram.dat // buffer low 16 bits - first time state := 1 rsp_valid := False } elsewhen (state === 1) { io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"0" rsp_data(15 downto 0) := io.sram.dat // buffer low 16 bits - second time state := 2 } elsewhen (state === 2) { io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"1" rsp_data(31 downto 16) := io.sram.dat // buffer high 16 bits - first time state := 3 } otherwise { io.sram.addr := io.bus.cmd.address(sramLayout.addressWidth downto 2).asBits ## B"1" rsp_data(31 downto 16) := io.sram.dat // buffer high 16 bits - second time rsp_valid := True // Signal data is READY state := 0 } } } otherwise { // not Valid state := 0 rsp_valid := False } }

Поместим этот код в файл Sram.scala и попробуем запустить сборку командой make clean && make. Если никаких синтаксических ошибок не возникло, то на стадии генерации кода Verilog (т. е. при исполнении байт-кода на JVM), мы должны получить длинный список из приведенных ниже сообщений:

rz@devbox:~/VexRiscv/scripts/Murax/Karnix$ make clean && make ... [info] [Progress] at 2.396 : Checks and transforms ... [error] Exception in thread "main" spinal.core.SpinalExit: [error] Error detected in phase PhaseCheck_noLatchNoOverride [error] ******************************************************************************** [error] ******************************************************************************** [error] NO DRIVER ON (toplevel/io_sram_cs : out Bool), defined at [error] mylib.SramInterface.<init>(Sram.scala:16) [error] vexriscv.demo.Murax$$anon$1.<init>(Murax.scala:176) [error] vexriscv.demo.Murax.<init>(Murax.scala:162) [error] vexriscv.demo.Murax_karnix$$anonfun$main$8.apply(Murax.scala:556) [error] vexriscv.demo.Murax_karnix$$anonfun$main$8.apply(Murax.scala:556) [error] spinal.sim.JvmThread.run(SimManager.scala:51) [error] ******************************************************************************** [error] ******************************************************************************** [error] NO DRIVER ON (toplevel/io_sram_we : out Bool), defined at [error] mylib.SramInterface.<init>(Sram.scala:17) [error] vexriscv.demo.Murax$$anon$1.<init>(Murax.scala:176) [error] vexriscv.demo.Murax.<init>(Murax.scala:162) [error] vexriscv.demo.Murax_karnix$$anonfun$main$8.apply(Murax.scala:556) [error] vexriscv.demo.Murax_karnix$$anonfun$main$8.apply(Murax.scala:556) [error] spinal.sim.JvmThread.run(SimManager.scala:51) [error] ******************************************************************************** ... [error] Nonzero exit code returned from runner: 1 [error] (Compile / runMain) Nonzero exit code returned from runner: 1 [error] Total time: 32 s, completed Feb 14, 2024, 11:47:45 PM

Сообщение об ошибке вида «NO DRIVER ON» говорит о том, что соответствующий сигнал объявлен и используется, но для него не назначен источник (нет «драйвера»), то есть нет схемы, формирующей этот сигнал. В нашем случае это легко объясняется тем, что мы описали интерфейсные сигналы для микросхемы SRAM, подключили сигнальные линии к самой микросхеме, но не подключили их к контроллеру PipelinedMemoryBusSram, да и сам контроллер не подключили к шине MainBus.

Ну что же, исправим это недоразумение — отредактируем файл Murax.scala, найдем в нём участок кода, в котором производится подключение «слэйв» устройств к шине MainBus путем добавления их в ассоциативный массив mainBusMapping:

//****** MainBus slaves ******** val mainBusMapping = ArrayBuffer[(PipelinedMemoryBus,SizeMapping)]() val ram = new MuraxPipelinedMemoryBusRam( onChipRamSize = onChipRamSize, onChipRamHexFile = onChipRamHexFile, pipelinedMemoryBusConfig = pipelinedMemoryBusConfig, bigEndian = bigEndianDBus ) mainBusMapping += ram.io.bus -> (0x80000000l, onChipRamSize) ...

И добавим сюда наш контроллер микросхемы SRAM:

val sramCtrl = new PipelinedMemoryBusSram( pipelinedMemoryBusConfig = pipelinedMemoryBusConfig, sramLayout = SramLayout(addressWidth = 18, dataWidth = 16) ) sramCtrl.io.sram <> io.sram mainBusMapping += sramCtrl.io.bus -> (0x90000000l, 512 kB)

При добавлении нового компонента декодеру шины сообщается, что контроллеру SRAM будет доступно адресном пространстве 512KB @ 0x90000000. Напомню, что адресное пространство «бортовой» RAM находится в диапазоне 96KB @ 0x80000000.

Запустим еще раз сборку и убедимся, что всё прошло гладко и без ошибок:

Статистика синтеза СнК Murax после добавления контроллера Sram

rz@devbox:~/VexRiscv/scripts/Murax/Karnix$ make (cd ../../..; sbt "runMain vexriscv.demo.Murax_karnix") [info] welcome to sbt 1.6.0 (Ubuntu Java 11.0.9.1) … [info] running (fork) vexriscv.demo.Murax_karnix [info] [Runtime] SpinalHDL v1.10.1 git head : 2527c7c6b0fb0f95e5e1a5722a0be732b364ce43 [info] [Runtime] JVM max memory : 8294.0MiB [info] [Runtime] Current date : 2024.02.15 00:24:16 [info] [Progress] at 0.000 : Elaborate components [info] [Warning] This VexRiscv configuration is set without software ebreak instruction support. Some software may rely on it (ex: Rust). (This isn't related to JTAG ebreak) [info] [Warning] This VexRiscv configuration is set without illegal instruction catch support. Some software may rely on it (ex: Rust) [info] [Progress] at 2.281 : Checks and transforms [info] [Progress] at 3.035 : Generate Verilog … Info: Logic utilisation before packing: Info: Total LUT4s: 2637/24288 10% Info: logic LUTs: 2149/24288 8% Info: carry LUTs: 272/24288 1% Info: RAM LUTs: 144/ 3036 4% Info: RAMW LUTs: 72/ 6072 1% Info: Total DFFs: 1428/24288 5% … Info: Packing constants.. Info: Packing carries... Info: Packing LUTs... Info: Packing LUT5-7s... Info: Packing FFs... Info: 675 FFs paired with LUTs. Info: Generating derived timing constraints... Info: Input frequency of PLL 'i_pll.pll_i' is constrained to 25.0 MHz Info: Derived frequency constraint of 75.0 MHz for net clk75 Info: Promoting globals... Info: promoting clock net clk75 to global network Info: promoting clock net io_core_jtag_tck$TRELLIS_IO_IN to global network Info: Checksum: 0x8aa53f27 Info: Device utilisation: Info: TRELLIS_IO: 54/ 197 27% Info: DCCA: 2/ 56 3% Info: DP16KD: 48/ 56 85% Info: MULT18X18D: 0/ 28 0% Info: ALU54B: 0/ 14 0% Info: EHXPLLL: 1/ 2 50% ... Info: TRELLIS_FF: 1428/24288 5% Info: TRELLIS_COMB: 2749/24288 11% Info: TRELLIS_RAMW: 36/ 3036 1% … Info: Max frequency for clock 'clk75': 80.34 MHz (PASS at 75.00 MHz) Info: Max frequency for clock 'io_core_jtag_tck$TRELLIS_IO_IN': 130.21 MHz (PASS at 12.00 MHz) … 2 warnings, 0 errors Info: Program finished normally. ecppack --compress --freq 38.8 --input murax_hello_world_out.config --bit murax_hello_world.bit

Главное, на что следует обращать во всей этой статистике то, что наш дизайн всё еще проходит по STA и максимально допустимая тактовая частота составляет 80,34 МГц, т. е. имеется некоторый запас «прочности».

17.2.2 Тестируем память и контроллер SRAM

Перед тем, как задействовать полученную область памяти в программе, нам потребуется некая функция, которая проведет тест всего пространства SRAM памяти объемом 512 КБ и выяснит, рабочая у нас SRAM или нет — вполне возможна такая ситуация, при которой микросхема SRAM перестанет справляться с задачей, т. е. попросту не будет успевать выполнять операции чтения/записи. Такая ситуация может возникнуть, если продолжить увеличивать тактовую частоту системного домена.

Строго говоря, организовать качественное тестирование памяти — это достаточно сложная задача, но мы не будем заниматься перфекционизмом, а воспользуемся простым алгоритмом — будем записывать псевдослучайную последовательность в ячейки памяти последовательно до конца области, после чего проделаем цикл чтения и сравнения читаемых данных с этой же псевдослучайной последовательностью. Ниже приведен вариант такой функции тестирования:

Фукнция тестирования области памяти использующая псевдостучайную последовательность.

#define SRAM_SIZE (512*1024) #define SRAM_ADDR_BEGIN 0x90000000 #define SRAM_ADDR_END (0x90000000 + SRAM_SIZE) // ... int sram_test_write_random_ints(void) { volatile unsigned int *mem; unsigned int fill; int fails = 0; fill = 0xdeadbeef; // random seed mem = (unsigned int*) SRAM_ADDR_BEGIN; print("Filling SRAM at: "); printhex((unsigned int)mem); while((unsigned int)mem < SRAM_ADDR_END) { *mem++ = fill; fill += 0xdeadbeef; // generate pseudo-random data } fill = 0xdeadbeef; // random seed mem = (unsigned int*) SRAM_ADDR_BEGIN; print("Checking SRAM at: "); printhex((unsigned int)mem); while((unsigned int)mem < SRAM_ADDR_END) { if(*mem != fill) { print("SRAM check failed at: "); printhex((unsigned int)mem); print("expected: "); printhex((unsigned int)fill); print("got: "); printhex((unsigned int)*mem); fails++; } mem++; fill += 0xdeadbeef; // generate pseudo-random data } if((unsigned int)mem == SRAM_ADDR_END) print("SRAM total fails: "); printhex((unsigned int)fails); return fails++; }

В приведенном выше коде на языке Си, мы для удобства объявляем набор констант для описания области памяти — её начальный адрес, конечный адрес и размер. В функции sram_test_write_random_ints(), мы сначала циклом заполняем тестируемую область 32-х битными числами, которые вычисляются по известной нам формуле — первоначальное число 0xDEADBEEF каждую итерацию цикла прибавляется к накопленной сумме в переменной fill, формируя псевдослучайное число. Затем производится чтение данных из этой же области и сравнение считанного числа с рассчитанным значением. Функция возвращает количество выявленных несовпадений, т. е. ошибок записи или чтения.

Добавим вызов функции sram_test_write_random_ints() в начало функции main() программы «hello_world», сразу после процедуры инициализации UART:

void main() { Uart_Config uart_config; uart_config.dataLength = UART_DATA_8; uart_config.parity = UART_PARITY_NONE; uart_config.stop = UART_STOP_ONE; uint32_t rxSamplePerBit = UART_PRE_SAMPLING_SIZE + UART_SAMPLING_SIZE + UART_POST_SAMPLING_SIZE; uart_config.clockDivider = SYSTEM_CLOCK_HZ / UART_BAUD_RATE / rxSamplePerBit - 1; uart_applyConfig(UART, &uart_config); sram_test_write_random_ints(); ...

Выполняем сборку всего проекта командой make clean && make. После устранения ошибок и получения битстрима, загружаем его в плату «Карно» командой make upload, запускаем эмулятор терминала minicom и наблюдаем за тем, как отрабатывает тест SRAM памяти. Если всё в порядке, то в порт будут выводиться следующие сообщения: