Данная статья открывает серию публикаций, посвященных многоядерным цифровым сигнальным процессорам TMS320C6678. В статье дается общее представление об архитектуре процессора. Статья отражает лекционно-практический материал, предлагаемый слушателям в рамках курсов повышения квалификации по программе «Многоядерные процессоры цифровой обработки сигналов C66x фирмы Texas Instruments», проводимых в Рязанском государственном радиотехническом университете.

Цифровые сигнальные процессоры TMS320C66xх строятся по архитектуре KeyStone и представляют собой высокопроизводительные многоядерные сигнальные процессоры, работающие как с фиксированной, так и с плавающей точкой. Архитектура KeyStone – это разработанный фирмой Texas Instruments принцип изготовления многоядерных систем на кристалле, позволяющий организовывать эффективную совместную работу большого числа ядер DSP- и RISC-типов, акселераторов и устройств периферии с обеспечением достаточной пропускной способности внутренних и внешних каналов пересылки данных, основой чего являются аппаратные компоненты: Multicore Navigator (контроллер обмена данными по внутренним интерфейсам), TeraNet (внутренняя шина пересылки данных), Multicore Shared Memory Controller (контроллер доступа к общей памяти) и HyperLink (интерфейс с внешними устройствами на внутрикристальной скорости).

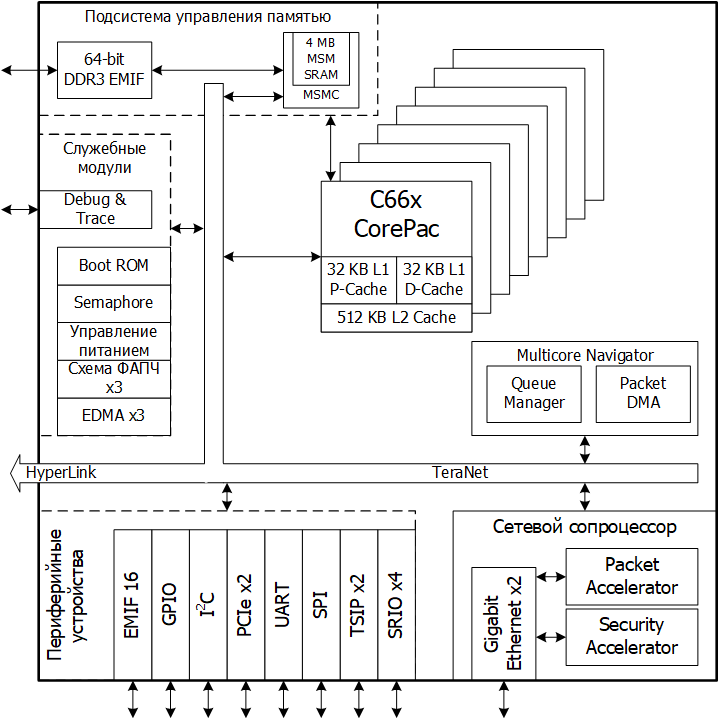

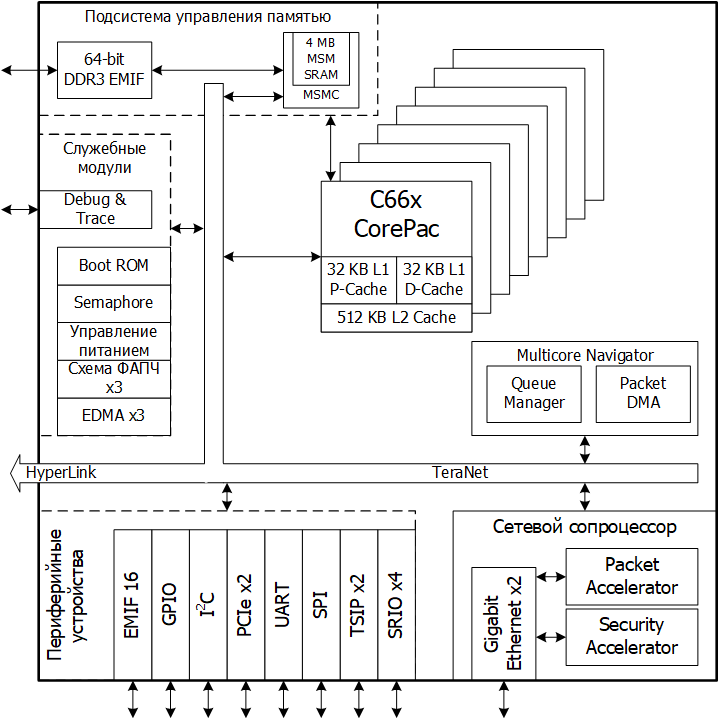

Архитектура процессора TMS320C6678 [2], наиболее высокопроизводительного процессора в семействе TMS320C66xх, изображена на Рисунке 1. Архитектура может быть разбита на следующие основные компоненты:

Рисунок 1. Общая архитектура процессора TMS320C6678

Процессор TMS320C6678 работает на тактовой частоте 1.25 ГГц. В основе функционирования процессора лежит набор операционных ядер С66х CorePack, количество и состав которых зависят от конкретной модели процессора. ЦСП TMS320C6678 включает в свой состав 8 ядер DSP-типа. Ядро является базовым вычислительным элементом и включает в свой состав вычислительные блоки, наборы регистров, программный автомат, память программ и данных. Память, входящая в состав ядра, называется локальной.

Кроме локальной памяти, есть память общая для всех ядер – общая память многоядерного процессора (Multicore Shared Memory – MSM). Доступ к общей памяти осуществляется через подсистему управления памятью (Memory Subsystem), которая также включает интерфейс внешней памяти EMIF для обмена данными между процессором и внешними микросхемами памяти.

Сетевой сопроцессор повышает эффективность работы процессора в составе различного рода телекоммуникационных устройств, реализуя аппаратно типовые для данной сферы задачи обработки данных. В основе работы сопроцессора лежат акселератор пакетной передачи данных (Packet Accelerator) и акселератор защиты информации (Security Accelerator). В спецификации на процессор перечислен набор протоколов и стандартов, поддерживаемых данными акселераторами.

Периферийные устройства включают:

Служебные аппаратные модули включают в себя:

Контроллер внутренних пересылок (Multicore Navigator) представляет собой мощный и эффективный аппаратный модуль, отвечающий за арбитраж передачи данных между различными компонентами процессора. Многоядерные системы на кристалле TMS320C66xx являются весьма сложными устройствами и, чтобы организовать обмен информацией между всеми компонентами такого устройства, необходим специальный аппаратный блок. Multicore Navigator позволяет ядрам, периферийным устройствам, хост-устройствам не брать на себя функции управления обменом данными. Когда какому-либо компоненту процессора необходимо переслать массив данных на другой компонент, он просто указывает контроллеру, что и куда нужно передать. Все функции по самой пересылке и синхронизации отправителя и получателя берет на себя Multicore Navigator.

Основой функционирования многоядерного процессора TMS320C66xх с позиции высокоскоростного обмена данными между всеми многочисленными компонентами процессора, а также внешними модулями, служит внутренняя шина TeraNet.

В следующей статье будет подробно рассмотрена архитектура операционного ядра C66x.

1. Multicore Programming Guide / SPRAB27B — August 2012;

2. TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor Data Manual / SPRS691C — February 2012.

Цифровые сигнальные процессоры TMS320C66xх строятся по архитектуре KeyStone и представляют собой высокопроизводительные многоядерные сигнальные процессоры, работающие как с фиксированной, так и с плавающей точкой. Архитектура KeyStone – это разработанный фирмой Texas Instruments принцип изготовления многоядерных систем на кристалле, позволяющий организовывать эффективную совместную работу большого числа ядер DSP- и RISC-типов, акселераторов и устройств периферии с обеспечением достаточной пропускной способности внутренних и внешних каналов пересылки данных, основой чего являются аппаратные компоненты: Multicore Navigator (контроллер обмена данными по внутренним интерфейсам), TeraNet (внутренняя шина пересылки данных), Multicore Shared Memory Controller (контроллер доступа к общей памяти) и HyperLink (интерфейс с внешними устройствами на внутрикристальной скорости).

Архитектура процессора TMS320C6678 [2], наиболее высокопроизводительного процессора в семействе TMS320C66xх, изображена на Рисунке 1. Архитектура может быть разбита на следующие основные компоненты:

- набор операционных ядер (CorePack);

- подсистема работы с общей внутренней и внешней памятью (Memory Subsystem);

- периферийные устройства;

- сетевой сопроцессор (Network Coprocessor);

- контроллер внутренних пересылок (Multicore Navigator);

- служебные аппаратные модули и внутренняя шина TeraNet.

Рисунок 1. Общая архитектура процессора TMS320C6678

Процессор TMS320C6678 работает на тактовой частоте 1.25 ГГц. В основе функционирования процессора лежит набор операционных ядер С66х CorePack, количество и состав которых зависят от конкретной модели процессора. ЦСП TMS320C6678 включает в свой состав 8 ядер DSP-типа. Ядро является базовым вычислительным элементом и включает в свой состав вычислительные блоки, наборы регистров, программный автомат, память программ и данных. Память, входящая в состав ядра, называется локальной.

Кроме локальной памяти, есть память общая для всех ядер – общая память многоядерного процессора (Multicore Shared Memory – MSM). Доступ к общей памяти осуществляется через подсистему управления памятью (Memory Subsystem), которая также включает интерфейс внешней памяти EMIF для обмена данными между процессором и внешними микросхемами памяти.

Сетевой сопроцессор повышает эффективность работы процессора в составе различного рода телекоммуникационных устройств, реализуя аппаратно типовые для данной сферы задачи обработки данных. В основе работы сопроцессора лежат акселератор пакетной передачи данных (Packet Accelerator) и акселератор защиты информации (Security Accelerator). В спецификации на процессор перечислен набор протоколов и стандартов, поддерживаемых данными акселераторами.

Периферийные устройства включают:

- Serial RapidIO (SRIO) версии 2.1 – обеспечивает скорость передачи данных до 5 GBaud на линию при числе линий (каналов) – до 4;

- PCI Express (PCIe) версии Gen2 – обеспечивает скорость передачи данных до 5 GBaud на линию при числе линий (каналов) – до 2;

- HyperLink – интерфейс внутренней шины, позволяющий коммутировать процессоры, построенные по архитектуре KeyStone, напрямую друг с другом и осуществлять обмен на внутрикристальной скорости; скорость передачи данных – до 50 Gbaud;

- Gigabit Ethernet (GbE) обеспечивает скорости передачи: 10/100/1000 Mbps и поддерживается аппаратным акселератором сетевых коммуникаций (сетевым сопроцессором);

- EMIF DDR3 – интерфейс внешней памяти типа DDR3; имеет разрядность шины 64 бита, обеспечивающую адресуемое пространство памяти до 8 Гбайт;

- EMIF – интерфейс внешней памяти общего назначения; имеет разрядность шины 16 бит и может использоваться для подключения 256MB NAND Flash или 16MB NOR Flash;

- TSIP (Telecom Serial Ports) – телекоммуникационный последовательный порт; обеспечивает скорости передачи до 8 Mбит/с на одну линию при числе линий – до 8;

- UART – универсальный асинхронный последовательный порт;

- I2C – шина внутренней связи;

- GPIO – ввод-вывод общего назначения – 16 выводов;

- SPI – универсальный последовательной интерфейс;

- Таймеры (Timers) – используются для генерации периодических событий.

Служебные аппаратные модули включают в себя:

- модуль отладки и трассировки (Debug and Trace) – позволяет получать отладочным инструментальным средствам доступ к внутренним ресурсам работающего процессора;

- загрузочное ПЗУ (boot ROM) – хранит программу начальной загрузки;

- аппаратный семафор (semaphore) – служит для аппаратной поддержки организации совместного доступа параллельных процессов к общим ресурсам процессора;

- модуль управления питанием – реализует динамическое управление режимами питания компонентов процессора с целью минимизации энергозатрат в моменты, когда процессор работает не в полную мощь;

- схема ФАПЧ – формирует внутренние тактовые частоты процессора из внешнего опорного тактирующего сигнала;

- контроллер прямого доступа в память (EDMA) – управляет процессом пересылки данных, разгружая операционные ядра ЦСП и являясь альтернативой Multicore Navigator.

Контроллер внутренних пересылок (Multicore Navigator) представляет собой мощный и эффективный аппаратный модуль, отвечающий за арбитраж передачи данных между различными компонентами процессора. Многоядерные системы на кристалле TMS320C66xx являются весьма сложными устройствами и, чтобы организовать обмен информацией между всеми компонентами такого устройства, необходим специальный аппаратный блок. Multicore Navigator позволяет ядрам, периферийным устройствам, хост-устройствам не брать на себя функции управления обменом данными. Когда какому-либо компоненту процессора необходимо переслать массив данных на другой компонент, он просто указывает контроллеру, что и куда нужно передать. Все функции по самой пересылке и синхронизации отправителя и получателя берет на себя Multicore Navigator.

Основой функционирования многоядерного процессора TMS320C66xх с позиции высокоскоростного обмена данными между всеми многочисленными компонентами процессора, а также внешними модулями, служит внутренняя шина TeraNet.

В следующей статье будет подробно рассмотрена архитектура операционного ядра C66x.

1. Multicore Programming Guide / SPRAB27B — August 2012;

2. TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor Data Manual / SPRS691C — February 2012.