Comments 25

"Не всё так однозначно". И в опросах маловато вариантов.

Я использовал Dot для составления блок-схемы алгоритма. Правда — post factum, для документирования.

Dot трудно назвать языком разметки, а dot диаграмма выше выглядит как электронная плата с проводными соединениями между компонентами:)

Может кто знает, есть ли «рисовальщик» дот’ов, который в зависимости от весовых коэффициентов (или других атрибутов), расположилы бы шейпы сверху вниз (или слева направо)? Очень напряжно «перерисовать цепь аккуратнее» для нескольких тысяч связей (пусть будет, например, связь сотрудников в AD).

Это возможно.

Веса есть и в самом dot. Но я недопонял, как ими пользоваться.

Говорю по своему опыту перерисовывания схемотехники под себя для олвиннеровского H3.

Опять же, у вас тут овал:

Любая принципиальная схема это, в сущности, граф.А тут уже сова:

Вот Dot код описывающий плату nRF5340-DK.Где промежуточный этап, Карл? Или вы хотите сказать, что пишете этот код вручную, глядя на pdf-ку? Тогда этому коду грош цена.

Или вы хотите сказать, что пишете этот код вручную, глядя на pdf-ку?

да.

Этот Dot код нужен для того, чтобы утилита dot.exe отрисовала граф и сама расставила ранги узлов. Так как иначе понять правильный путь электрического сигнала не очевидно.

да.рукалицо.jpg

А просто пристально, вдумчиво поизучать схему не вариант вообще? По-моему вы мартышкиным трудом с этим описанием занимаетесь. Сколько времени у вас ушло на составление приведенного описания? Полученная схема в виде графа абсолютно нечитаема. Сколько времени вы потратили на то, чтобы привести её в более компактный нечитаемый вид? По-моему это время можно было провести с чуть большей пользой, поблочно разрисовав всё сразу вручную в том же yEd, если вам настолько не хватает структурной схемы готовой борды.

По поводу важности составления блок схем печатных плат у меня есть отдельный пост

https://habr.com/ru/post/667030/

Сколько времени у вас ушло на составление приведенного описания?

пара часов, параллельно просматривая YouTube

А просто пристально, вдумчиво поизучать схему не вариант вообще?

Pdf(ки) со схемотехникой от Vendor(a) иногда настолько циклопические (45--100 страниц), что подвисают при обычном Ctrl+F.

Полученная схема в виде графа абсолютно нечитаема.

Если поставить свойство ортогональных сплайнов

splines=ortho;то читаемость заметно повышается

очень интересно, но ничего не понятно. замена на кракозябры удалила идею целиком

ладно кракозяблы, так ведь и стрелочки еще "невидимым серым"!

PS: вроде там можно настроить ему, чтобы он квадратнее группы\субгруппы делал, не?

В ванильном dot можно, плагинчик который всё это в призму заворачивает будет это игнорировать.

Здесь оно на самом деле стрёмно выглядит, по факту я сейчас в основном в графике смотрю только дела на сегодня. Дела на неделю и долгосрочные в основном ручные и write-only прямо в исходнике: это либо добавление новых, либо сортировка, либо вычерпывание задач из предыдущего пула на текущий, либо вырезание неактуального.

Процитирую себя же с другого ресурса о проблемах такого подхода:

Мне, блин ОЧЕНЬ нравится простота graphviz в вопросе проведения и изменения связей между сущностями (самое сложное – в кавычки брать всё, что содержит неалфавитные символы), но как её перенести на приложение с хоть какой-то логикой и формальной схемой хранения данных (не вычислять же их из gv каждый раз? Хотя, кэши сила), которая неумолимо займёт место точки правды, а потому заберёт у gv предназначение способа ввода и сделает его промежуточным форматом для выхлопа – хз.

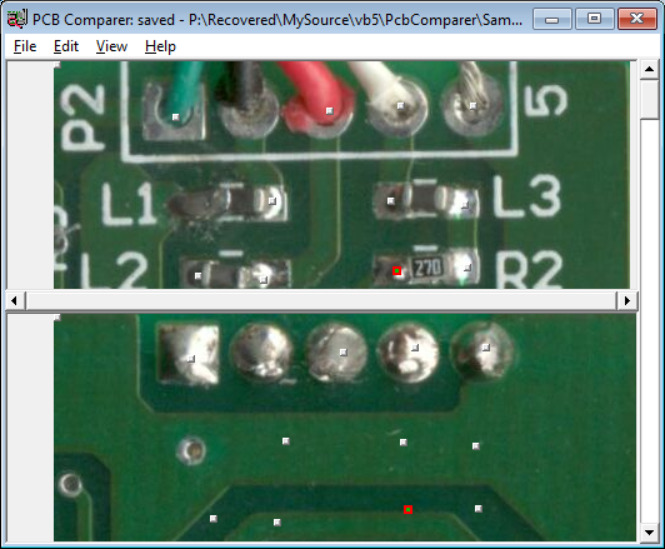

Я когда-то в стародревние времена писал реверс-инжиниринговую программку-вьюер печатной платы (pcbcomparer), просмотр одновременно с двух сторон (две фотки).

Создание пинов (контактных площадок), цепей меж ними и ... генерация netlist-а для CAD-ов.

Набор компонент на плате использовался очень ограниченный: резистор, конденсатор, дроссель, транзистор, контактный вывод и многополюсник-черный-ящик - с соответствующими библиотечными элементами

Кроме net-list-а программа создавала файл печатной платы в самом первом старинном текстовом формате Protel (сейчас уже общеизвестный Altium).

И, если мне не изменяет память, процесс реверс-инжиниринга выглядел так:

файл .pcb открывался в Protel'99

в него импортировался NetList

в интерфейсе Protel создавался новый файл принципиальной схемы .sch

и ... делалась синхронизация: т.е. перенос компонент и цепей в схему с платы, силами Protel-а.

Таким образом "генерировалась" схема, в которой мышой компоненты двигались, цепи "резиной" тянулись за компонентом. Компоненты расставлялись-раздвигались, и потом можно их было заменить на другие библиотечные элементы микросхем-контроллеров, если было охота.

Но странное дело - я уже даже и не помню, что пошло не так, и почему разработка программы не пошла далее. Вероятнее всего потому, что я продолжал создавать схемы с нуля, без использования реверс-инжиниринга :)

А удалось ее реанимировать :)

С nrf и их отладочными платами имел дело. В упор не понял при чем тут дот, графы и вообще нафига это все нужно. Разобраться с платой можно по описанию, и это не сложнее чем научится пользоватся посудомойкой или материнкой компа. Другое дело что у нордика достаточно специфичный подход к отладочным платам. Они там скорее не отладочные а демонстрационные , да еще и за дикие деньги. Для nrf9160 пришлось заказывать свой девкит т.к. их ни куда не годится, на плате налеплена куча ненужной ппреферии которая тупо мешает подключить свою. Половина ножек на ружу не выведена, в общем как отладочная плата это мало применимо.

Я попробовал описать на DOT циклограмму тех процесса установки, которой я занимался на работе. Предполагается, что после визуальной проверки исходный файл описания циклограммы будет вводиться в программу управления установкой на базе обработки данных в потоке на Elixir. Фактически, модель циклограммы описывает разворачивание и взаимодействие граф процессов.

К сожалению, не смог растянуть граф в направлении time-line сверху вниз. Подразумевалось представление в виде плавающих дорожек. А так визуально граф получается "скомканным".

Как специалиста, хочу Вас спросить: "Можно параметрически решить эту задачу?"

Язык Graphviz для Автогенерации Блок-Схем Сложных Электронных Цепей