Новостной дайджест событий из мира FPGA/ПЛИС — №0010 (2021_03) + конференция FPGA разработчиков

ПЛИСкульт привет, FPGA хаб!

Программируемые логические интегральные схемы

ПЛИСкульт привет, FPGA хаб!

Ниже предложен рецепт приготовления деликатеса, позволяющего Вам попробовать различные 8 и 16-битные приставки и компьютеры. Основное же блюдо для меня miniMIG — Amiga core с графикой OCS/AGA/RTG и CPU до 68020 в 20 раз быстрее стандартной A600.

В свои студенческие годы после ZX-Spectrum (Пентагон-128 с дисководом) я прикоснулся к волшебному миру Амига, сначала A600, затем A1200, аксели от 030-40MHz до PPC603+040. И вот, совсем недавно я узнал о Apollo Vampire (цена конечно кусачая) решил поискать что-нибудь подобное. Нашел несколько вариантов, но самый интересный, на мой взгляд, проект MIST доделанный Павлом Рябцовым. Проштудировал ветку Сборка, настройка платы MiST v 1.31 , заказал на сайте CHIPkin две печатные платы (как оказалось потом правильное решение, попеременно возникали проблемы то с одним, то с другоим экземпляром) и детали, которые были в наличии. Остальное было куплено на Али и "Чип и Дип", по мере прибытия деталей, начал сборку, о чем и хочу рассказать вам. Если Вы являетесь таким же OLD-фагом старых компьютеров, как и я, пожалуйста, приготовьтесь к прочтению.

ПЛИСкульт привет, FPGA хаб.

Мы продолжаем держать вас в курсе последних событий из мира программируемой логики и решили немного пересмотреть формат дайджеста. Мы добавили категории, чтобы было проще искать. Под катом вы найдете: статьи, новости, анонсы, вебинары, вакансии, а еще информацию по конференции FPGA разработчиков

Наверное многие, из тех, кто увлекается изучением того, как работает компьютер на самом низком уровне читали такие книги как: Таненбаум "Архитектура компьютера" или Харрис, Харрис "Цифровая схемотехника и архитектура компьютера", которые безусловного являются объемлющими трудами и хорошими книгами для обучения. Но если вы не являетесь инженером, но всё равно хотите погрузиться в мир цифровых вычислений и более глубоко понять то, а как же работает компьютер. В этом вам сможет помочь книга Чальза Петцольда "Код. Тайный язык информатики", которая начинает свой рассказ от причин, по которым людям понадобился обмен информацией и её обработка , с какими проблемами при этом столкнулись и заканчивает рассказам об устройстве реальных операционных систем и процессоров и их архитектуру. При этом автором был отлично подобран уровень абстракции, которого он придерживался при написании. В каких-то моментах подробно описывая работу элементарных частей процессора, а в других рассказывая простыми словами о сложных вещах.

ПЛИСкульт привет, FPGA хаб.

Мы продолжаем держать вас в курсе последних событий из мира программируемой логики и решили немного пересмотреть формат дайджеста. Мы добавили категории, чтобы было проще искать информацию. В этот выпуск мы добавили: вебинары, анонсы, статьи, стримы, вакансии и даже сделали pdf версию. Подробности по катом

Все делают это. Ну ладно, не все, но большинство. Пишут скрипты, чтобы симулировать свои проекты на Verilog, SystemVerilog и VHDL. Однако, написание и поддержка таких скриптов часто бывает довольно непроста для типично используемых Bash/Makefile/Tcl. Особенно, если необходимо не только открывать GUI для одного тестбенча и смотреть в диаграммы, но и запускать пачки параметризированных тестов для различных блоков, контролировать результат, параллелизировать их выполнение и т.д. Оказалось, что всё это можно закрыть довольно прозрачным и легко поддерживаемым кодом на Python, что мне даже обидно становится от того, как я страдал ранее и сколько странного bash-кода родил.

Идея сделать цифровые логические микросхемы с изменяемой структурой была всегда. Почему? Достаточно посмотреть на толстенный каталог чипов серии TTL 74xx (или советской К155), чтобы такая идея самозародилась. В СССР почти у каждого инженера и радиолюбителя был справочник В.Л. Шило «Популярные цифровые микросхемы», который вышел каким-то невероятным тиражом. Но всё равно, хотелось иметь некий «универсальный кристалл», из которого можно сделать все остальные микросхемы (ну хорошо, не все, но многие).

Идея сделать цифровые логические микросхемы с изменяемой структурой была всегда. Почему? Достаточно посмотреть на толстенный каталог чипов серии TTL 74xx (или советской К155), чтобы такая идея самозародилась. В СССР почти у каждого инженера и радиолюбителя был справочник В.Л. Шило «Популярные цифровые микросхемы», который вышел каким-то невероятным тиражом. Но всё равно, хотелось иметь некий «универсальный кристалл», из которого можно сделать все остальные микросхемы (ну хорошо, не все, но многие).Здравствуйте друзья.

Продолжаем публиковать новости из мира FPGA/ПЛИС.

В 2020 опубликовано 238 новостей, запущены FPGA стримы и проведена первая отечественная FPGA конференция. Подборка за декабрь и ссылки на все упоминания под катом.

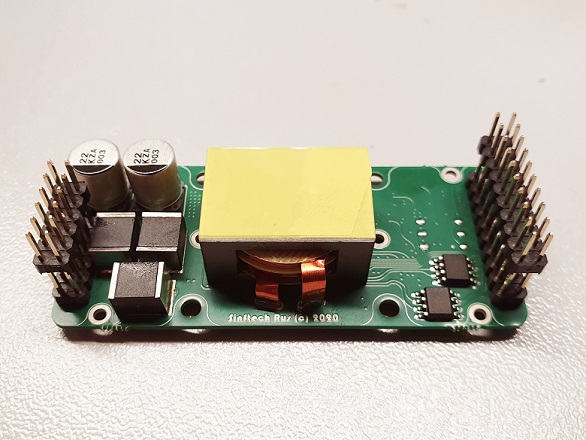

Всё началось с проекта моих новых колонок. Давно увлекаюсь, в качестве хобби, разными аудиопроектами, иногда, довольно долгими и сложными. В этот раз, моё хобби совпало с вероятным будущим направлением профессиональной деятельности.

Некоторое время назад в одном из новостных FPGA дайджестов было небольшое упоминание о FPGA конференции.

Так вот, конференция состоялась 28 ноября 2020 года, и этим постом я бы хотел поведать вам об этом «немаловажном» для отечественного FPGA сегмента событии. Постараюсь рассказать обо всём «от идеи до реализации».