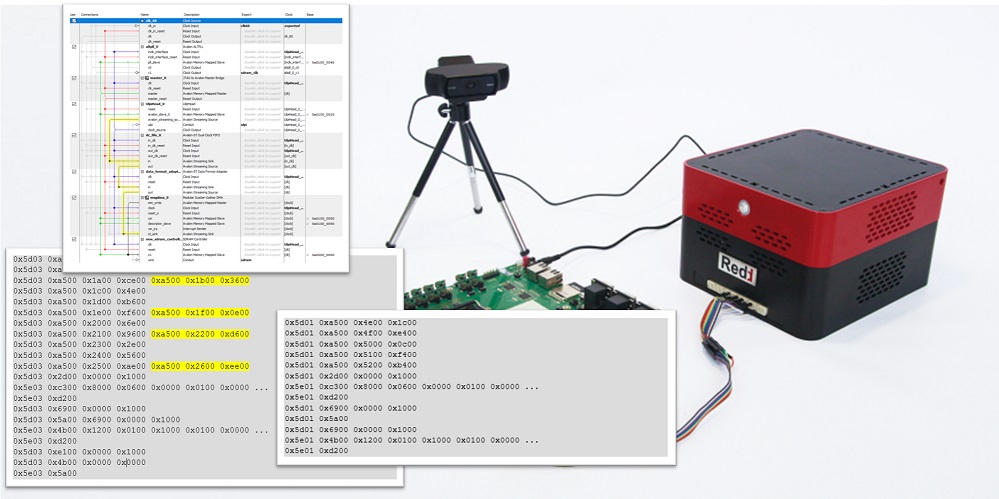

Скоростной АЦП с нуля. 16 бит за 10 лет

Программируемые логические интегральные схемы

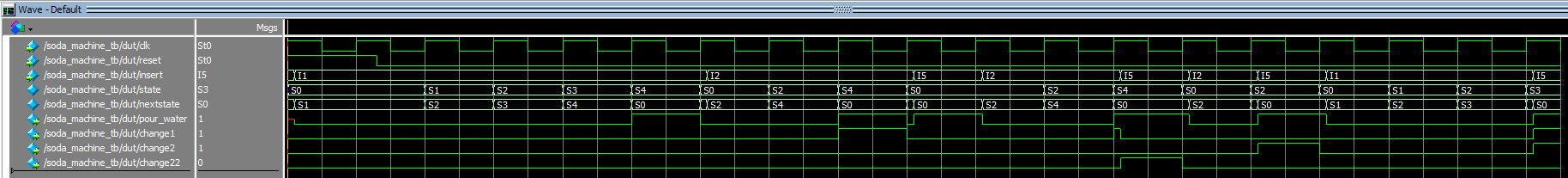

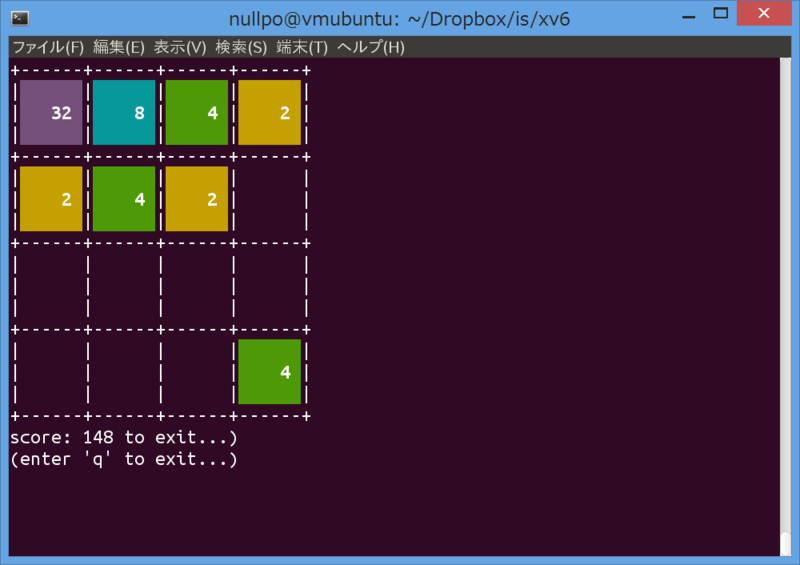

Знаешь что такое цифровой автомат(FSM)!? Интересуешься цифровой схемотехникой? Если да, то вам будет интересно посмотреть решение одной проблем, которую часто игнорируют. Если нет, то вам придётся потратить дополнительно 5 минут на введение)

Для тех кто хочет загрузить свой мозг новой интересной задачей. Результаты вас удивят.

Здравствуйте, друзья.

Продолжаем публикации последних событий из мира FPGA/ПЛИС. Ниже приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

А еще в РФ очень очень скоро будет FPGA конференция/митап :)

Здравствуйте, друзья.

Возвращаемся к публикации последних событий из мира FPGA/ПЛИС. Ниже приведены несколько ссылок на новости, анонсы, вебинары, воркшопы, туториалы, видео и тд. Подобные новостные дайджесты есть, например, на хабе про php, почему бы и не сделать что-то подобное и для ПЛИС?

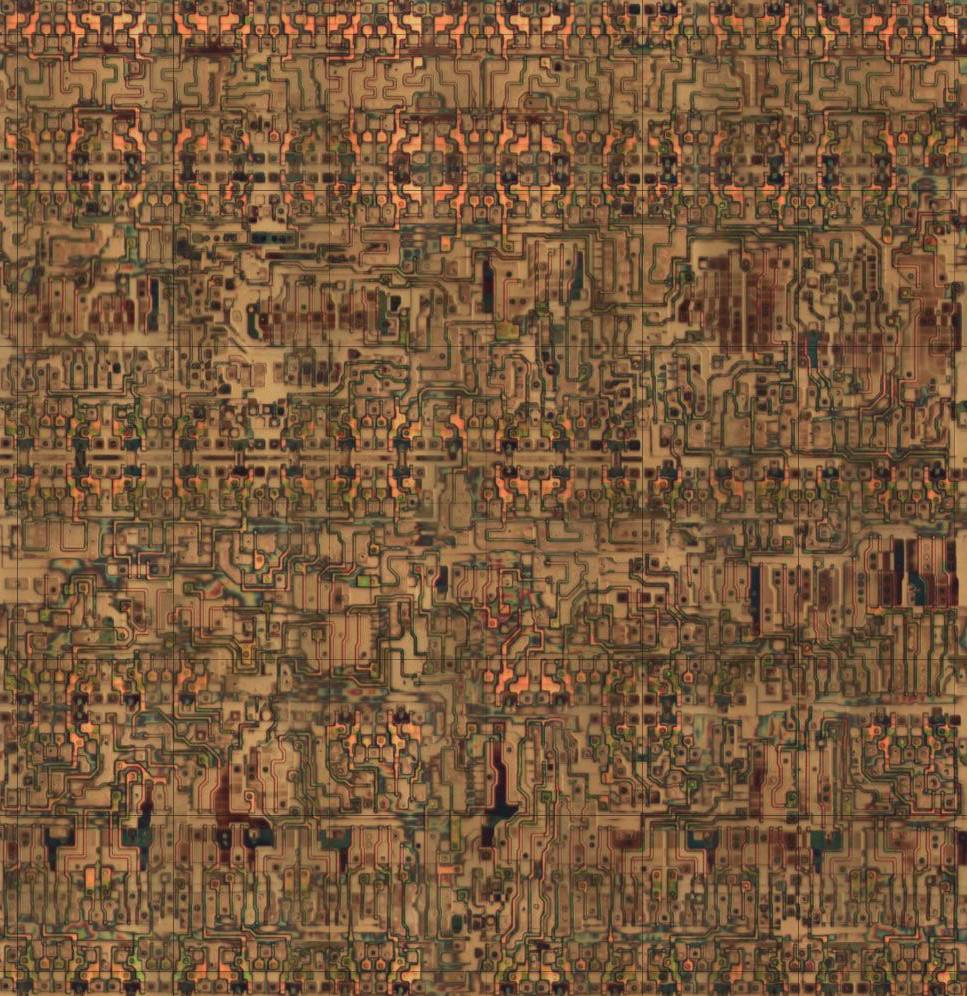

Эта статья является переводом поста Chris Hodapp Embedding Haskell: Compilers, and compiling compilers В своём посте автор рассматривает различные подходы к использованию Haskell для написания кода для встраиваемых систем. Предоставим слово автору.

В моем последнем посте упоминалось, что некоторые вещи требуют лучшего объяснения, потому что я всегда пытаюсь объяснить и уточнить.

Этот блог посвящен использованию Haskell со встраиваемыми системами. Что это хотя бы значит? Мы видим пару широких категорий (которые отражают слайды на последней странице, а также наша страница ссылок):