nanoFOX — простое RISC-V совместимое ядро

Небольшое вступление:

Идея написания собственного ядра появилась после прохождения школы-семинара по цифровой схемотехнике в городе Томске. На данном мероприятии проводилось знакомство с текущими языками описания аппаратуры (Verilog HDL и VHDL), а также с небольшим процессорным ядром schoolMIPS. Для понимания устройства ядер было принято решение изобрести собственный велосипед, следуя по пути развития schoolMIPS, но взяв за основу другую систему команд. Вследствие роста популярности RISC-V и открытости его системы команд (MIPS на момент начала написания ядра не имел открытую систему команд) для осуществления разработки будущего ядра был выбран набор инструкций RISC-V, а именно RV32I. RV32I имеет небольшой набор базовых инструкций (37 без учёта специальных) и при желании его можно расширить, например, добавив инструкции целочисленного умножения и деления (RV32M) или поддержку сокращённых инструкций (compressed instructions) (RV32C). Также данный проект задумывался как образовательный, поэтому было решено по максимуму увеличить наглядность работы ядра для эффективной демонстрации его работы.

По аналогии с schoolMIPS были реализованы следующие версии ядра:

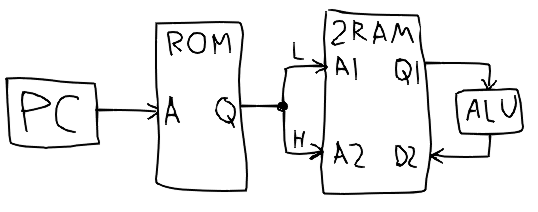

- Однотактная версия (00_simple_risc_v_cpu).

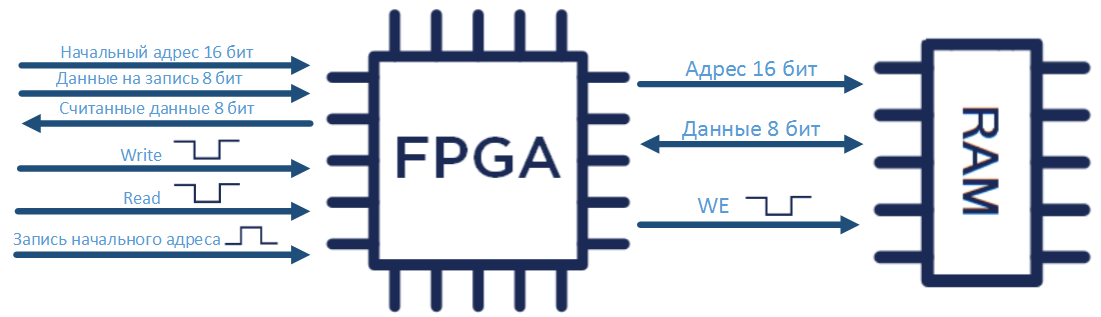

- Однотактная версия с поддержкой инструкций lw/sw (load word/store word) (01_simple_risc_v_cpu_lwsw).

- Конвейерная версия (5-ти стадийный конвейер) (02_pipe_risc_v_cpu).

На текущий момент описывается следующая версия ядра (03_pipe_risc_v_cpu_fc) с полным набором команд RV32I (без учёта некоторых специальных).

В статье описан очередной примитивный процессор и ассемблер для него.

В статье описан очередной примитивный процессор и ассемблер для него.