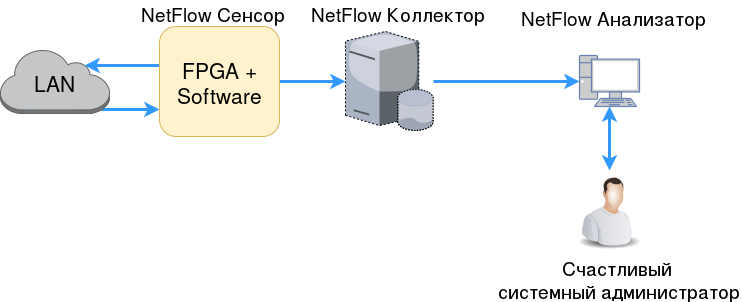

Реализация NetFlow сенсора на FPGA + CPU — гибко и быстро

Добрый день!

Как вы поняли из названия, вас ждет очередная статья про NetFlow, но на этот раз с необычной стороны — со стороны реализации NetFlow сенсора на FPGA.

Программируемые логические интегральные схемы

Добрый день!

Как вы поняли из названия, вас ждет очередная статья про NetFlow, но на этот раз с необычной стороны — со стороны реализации NetFlow сенсора на FPGA.

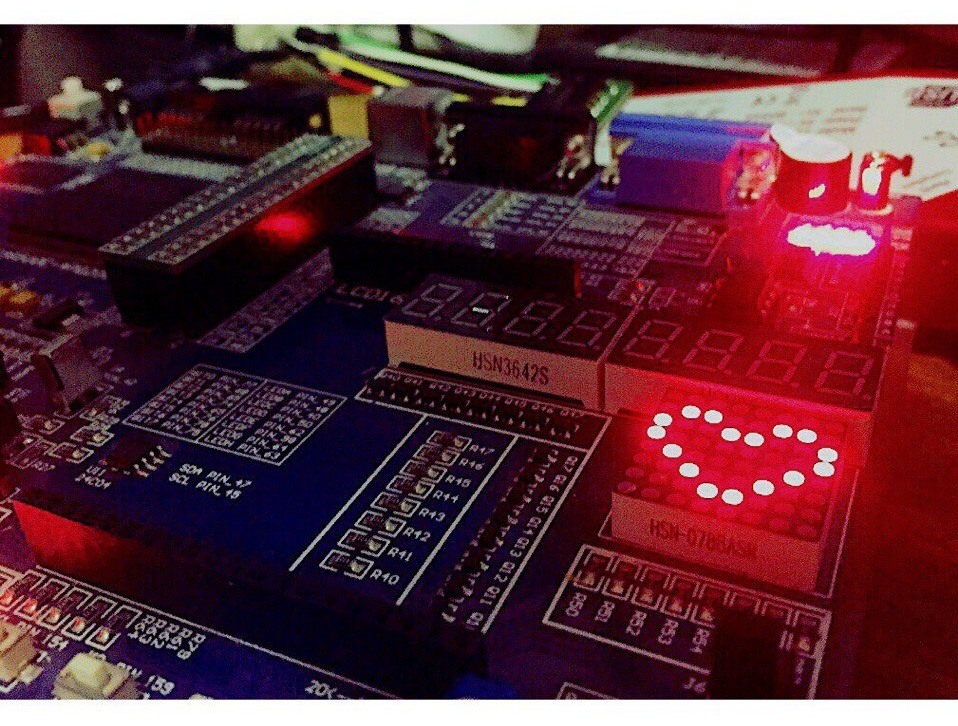

Недавно мы применили плату Ethond в качестве мини-роутера и запустили на нём OpenVPN.

Недавно мы применили плату Ethond в качестве мини-роутера и запустили на нём OpenVPN.

Но обнаружилось, что процессор часто нагружается на 100%, а скорость не поднимается выше 15-16 Мбит/с. На канале связи 100 мегабит это очень мало, поэтому мы решили ускорить процесс аппаратно.

Ребята из группы FPGA-разработчиков сделали прошивку на базе открытого IP-core для Altera CycloneV с реализацией шифра AES-128, которая умеет шифровать 8 Гбит/сек и дешифровать 700 Мбит/сек. Для сравнения, программа openssl на CPU (ARM Cortex A9) того же CycloneV может обрабатывать лишь около 160 Мбит/сек.

Эта статья посвящена нашему исследованию по применению аппаратного шифрования AES. Мы сжато представим описание криптографической инфраструктуры в Linux и опишем драйвер (исходный код открыт и доступен на github), который осуществляет обмен между FPGA и ядром. Реализация шифрования на FPGA не является темой статьи — мы описываем лишь интерфейс, с которым происходит взаимодействие c акселератором со стороны процессора.

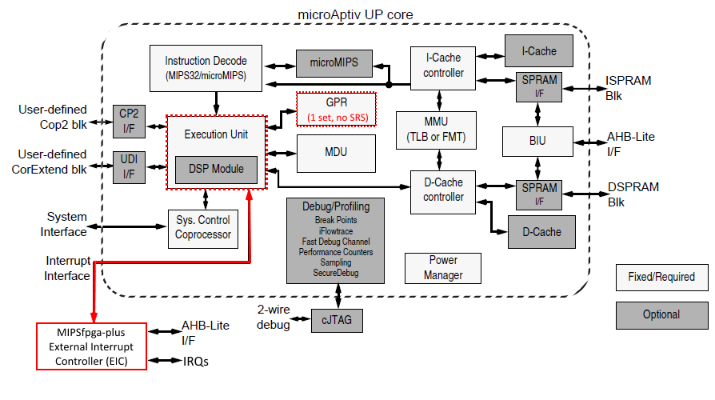

Прошло чуть больше месяца с тех пор, как я портировал open source модуль UART16550 на шину AHB-Lite. Писать об этом на тот момент было несколько не логично, так как еще не была опубликована статья про прерывания MIPSfpga.

Если вы опытный разработчик, то для вас только одна полезная новость: UART16550 добавлен в состав системы MIPSfpga-plus, дальше можете не читать. А тем, кого интересует разобранный пример использования этого модуля — добро пожаловать под кат.

В статье приводится несколько примеров настройки и использования прерываний MIPS32 Release 2, включая подробное описание задаваемой при этом конфигурации, описывается работа с контроллером внешних прерываний.

Весь описываемый код опубликован на github в составе проекта mipsfpga-plus [L3].

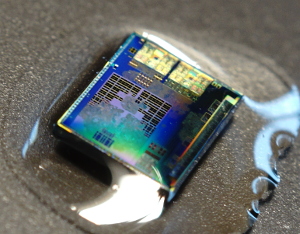

Думаю многие уже слышали про реализованный московскими разработчиками Байкал Электроникс процессор Байкал-Т1 — с двумя ядрами Imagination Technologies P5600 MIPS 32 r5 и набортным 10GbE. Байкал оказался первым, кто реализовал в кремнии это ядро.

Думаю многие уже слышали про реализованный московскими разработчиками Байкал Электроникс процессор Байкал-Т1 — с двумя ядрами Imagination Technologies P5600 MIPS 32 r5 и набортным 10GbE. Байкал оказался первым, кто реализовал в кремнии это ядро.

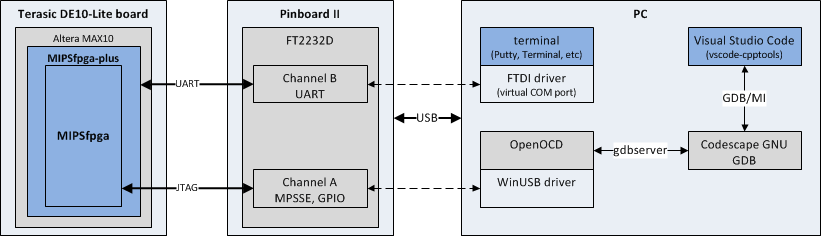

Поставляемые в составе пакета MIPSfpga документация, ПО и конфигурационные файлы предполагают применение Bus Bluster в качестве аппаратного отладчика. Статья содержит инструкции по использованию для этой цели практически любого USB-UART адаптера, построенного на микросхеме FTDI с поддержкой MPSSE (FT232H, FT2232H, FT4232H, FT2232D). Кратко описывается интеграция среды разработки Visual Studio Code и отладчика GNU GDB.

Все конфигурационные файлы, описываемые в статье, а также часть документации доступны на github.

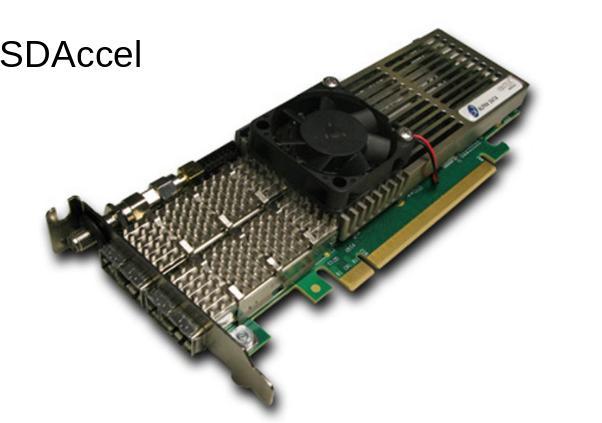

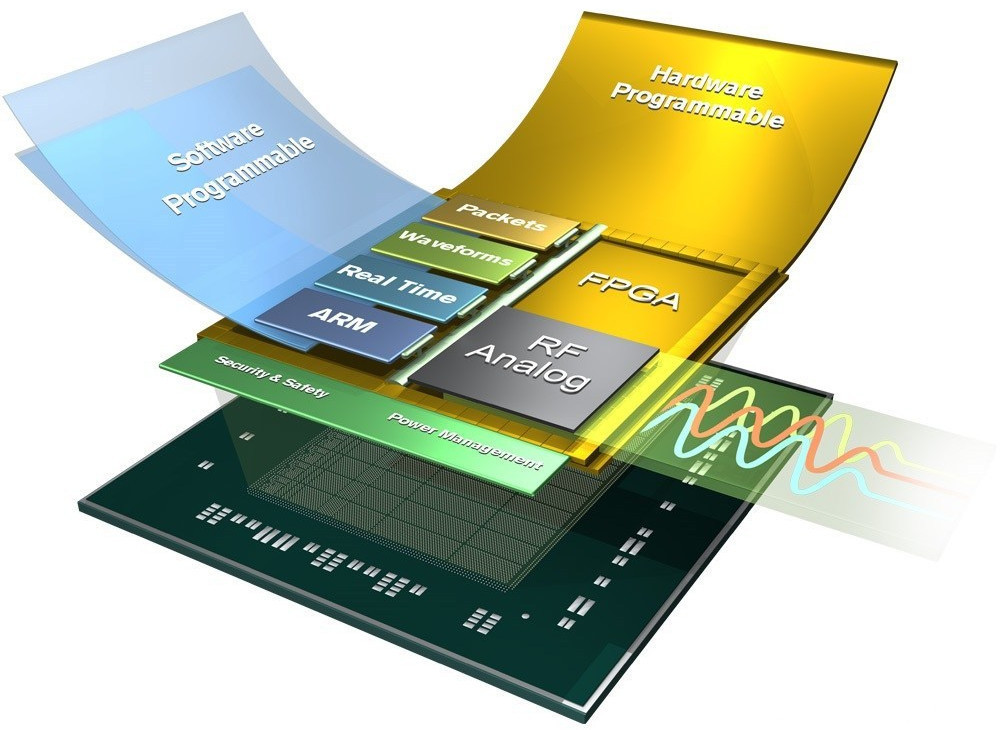

В разработке электронных устройств грань между разработчиком-схемотехником и разработчиком-программистом очень размыта. Что уж говорит о том, кто должен писать RTL под FPGA.

С одной стороны, RTL — это территория схем, с другой стороны, ресурсы FPGA дешевеют, синтезаторы умнеют. Цена ошибки RTL дизайнера для FPGA не превышает цены ошибки программиста, а созданные схемы можно также обновлять и наращивать по функциональности, как обычную прошивку процессора.

Производители микросхем тоже не отстают, стали паковать ПЛИС в один корпус с процессором, даже Intel выпустил процессор для PC с FPGA внутри, купив для этого известного производителя ПЛИС Altera.

Думаю всем истинным программистам Вселенная шлет сигналы, что им просто необходимо изучить RTL и начать писать “код” для FPGA не хуже, чем под их привычные процессоры.

Когда-то давно, я проходил этот путь и позволю себе дать несколько советов для ускорения.