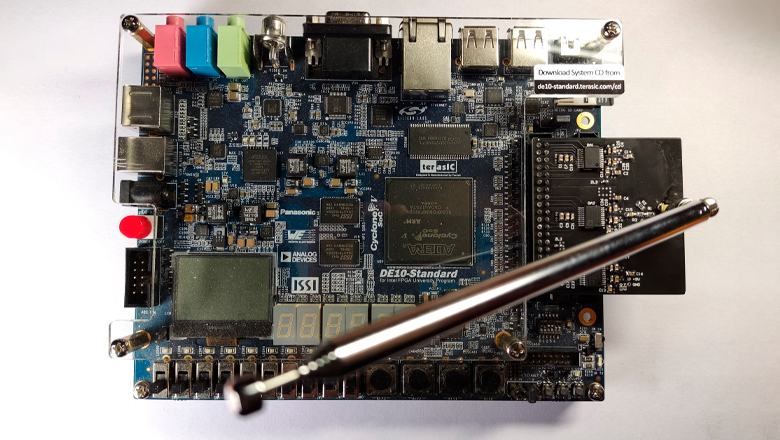

Наверное каждый "ПЛИСовод" использовал высокоскоростные приёмопередатчики хотя бы раз в своей практике. В семействе ПЛИС Intel/Altera серии IV IP ядро с этим функционалом называется ALTGX.

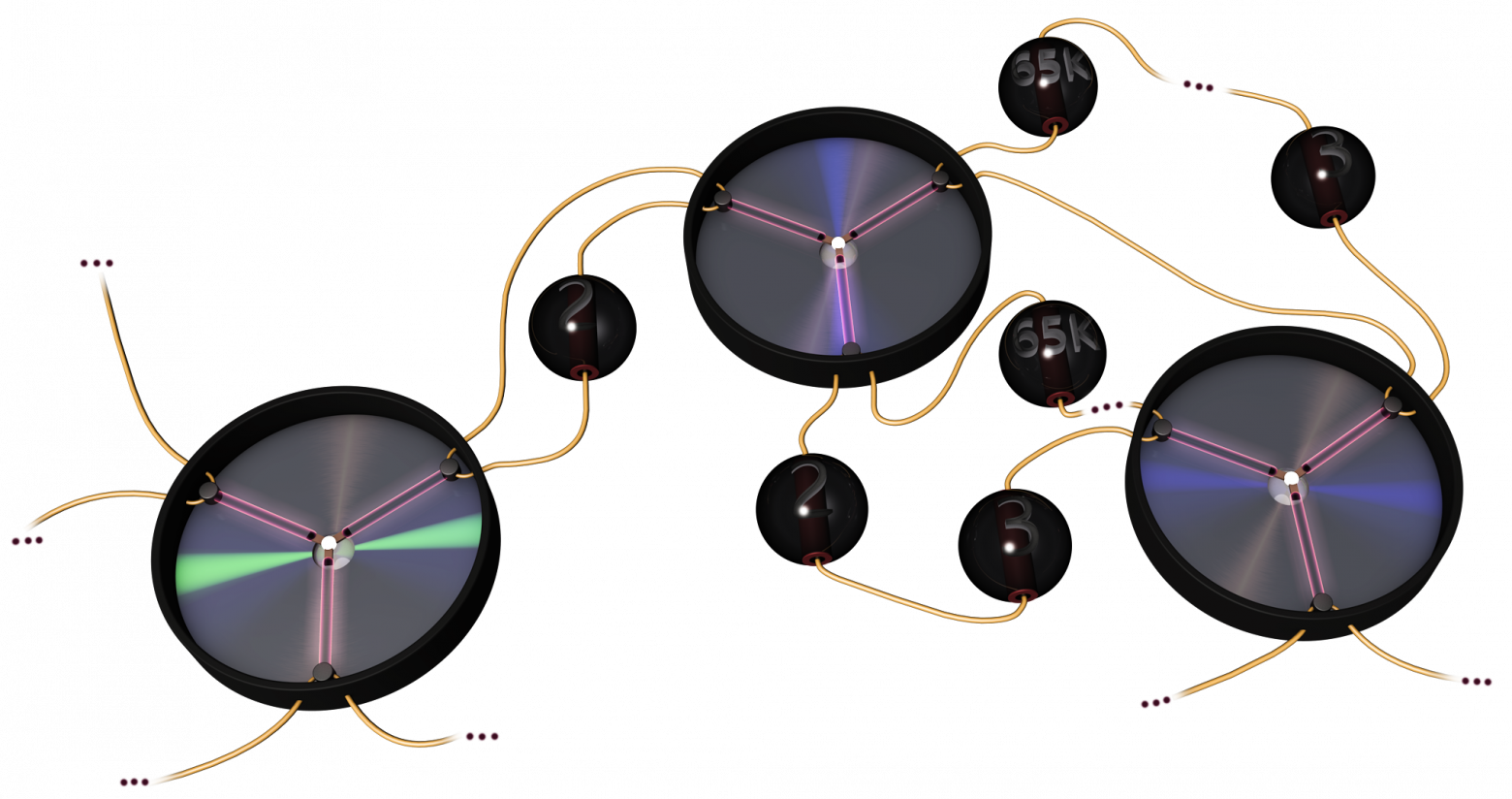

Основная задача этого IP ядра - преобразование параллельной шины на низкой частоте в последовательную шину на высокой.

Динамическая реконфигурация позволяет менять различные параметры приёмопередатчиков "на лету", то есть не меняя прошивку ПЛИС.

Основными из них являются:

скоростные характеристики, то есть на какой скорости будут принимать и передавать данные

включать/выключать встроенные кодеки (в ПЛИС серии IV - кодек 8b/10b)

менять аналоговые параметры, такие как TX VOD, TX Preemphasis, RX Offset Cancelation, RX Adaptive Equalizer

Ни для кого не секрет, что компиляция и тестирование проектов ПЛИС занимает достаточно большую часть времени всего процесса разработки. Поэтому часто разработчики используют различные среды симуляции для тестирования своих модулей. Но многие ли использовали среду симуляции для тестирования разработанных модулей в связке с используемыми IP ядрами от разработчика ПЛИС. В этой статье мы решили поделиться своим опытом, начиная с создания IP ядра ALTGX для ПЛИС Intel Cyclone IV до симуляции созданного проекта для тестирования модулей динамической реконфигурации с связке с ALTGX.