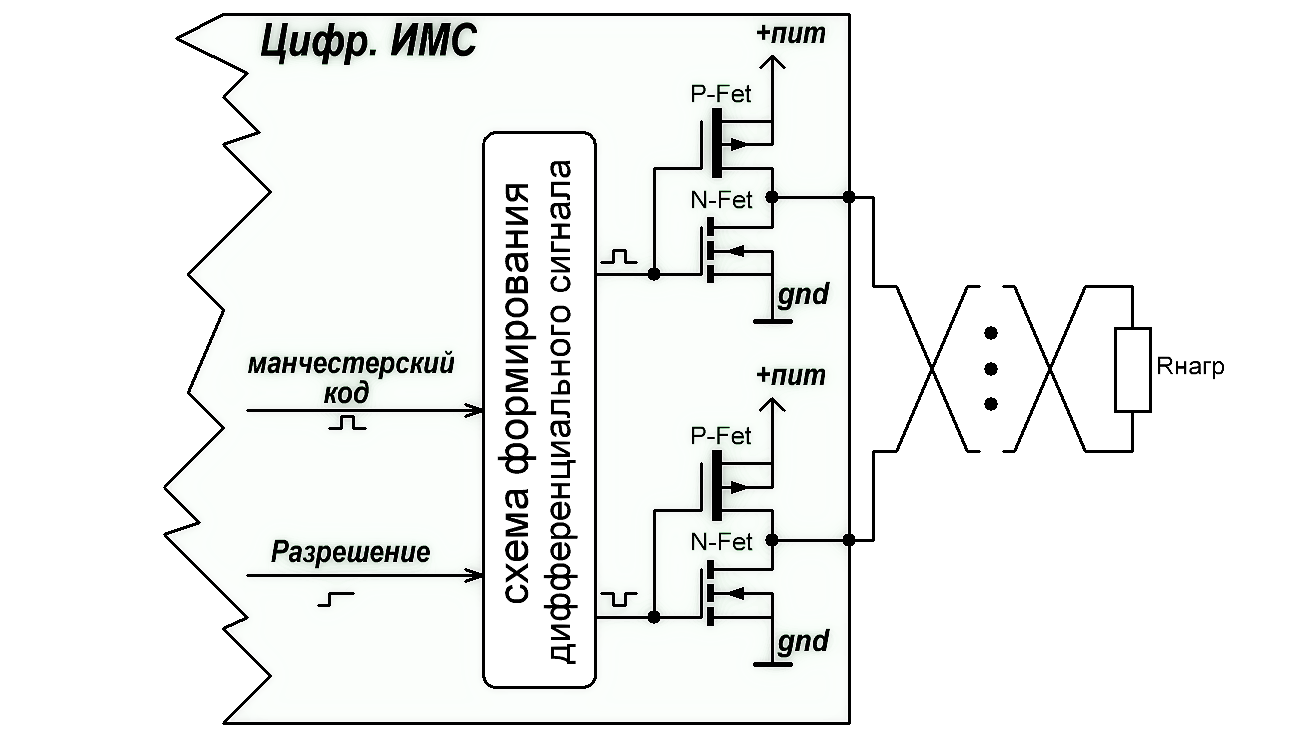

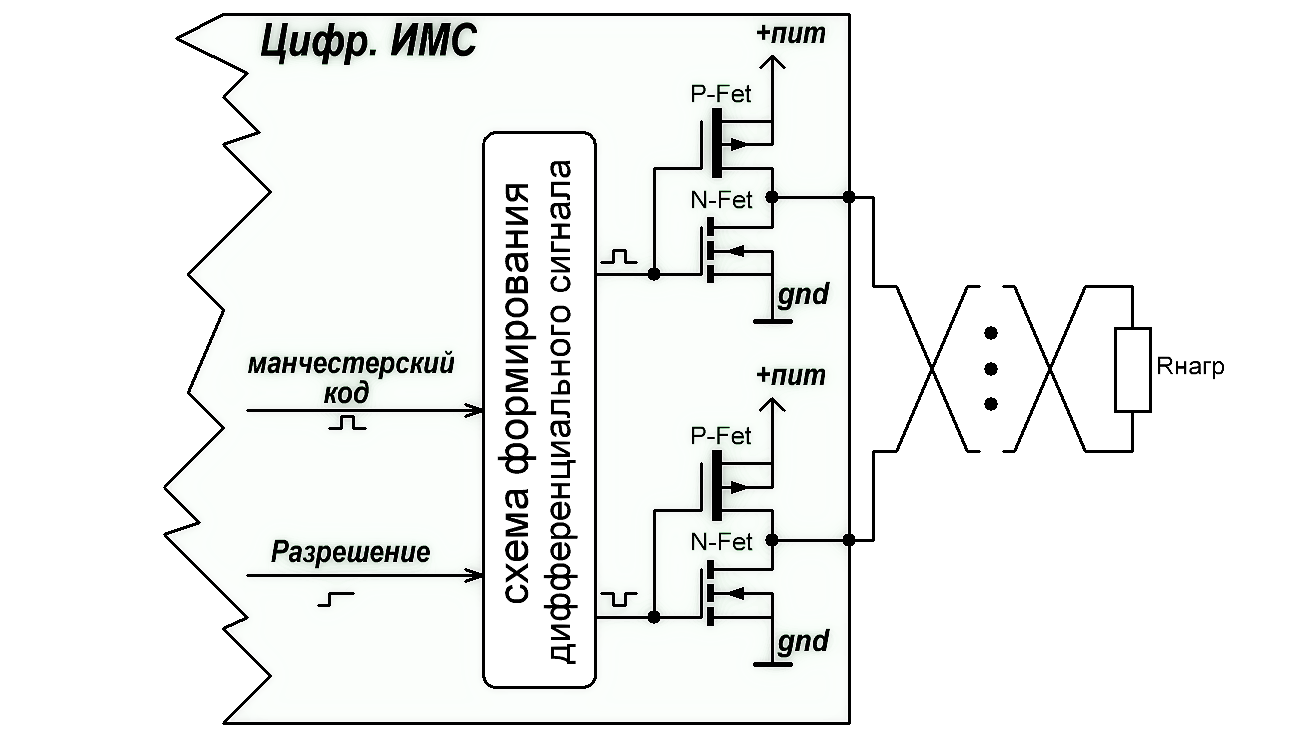

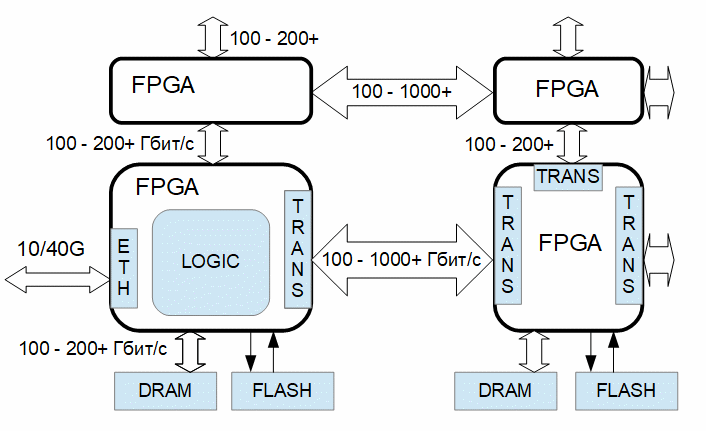

Интереса ради сделал максимально простенький комплект модулей: приемники, передатчики и те и другие с разным набором плюшек, реализующих простой самобытный протокол связи с манчестерским кодированием для связи 2х и более ПЛИС.

Программируемые логические интегральные схемы

Интереса ради сделал максимально простенький комплект модулей: приемники, передатчики и те и другие с разным набором плюшек, реализующих простой самобытный протокол связи с манчестерским кодированием для связи 2х и более ПЛИС.

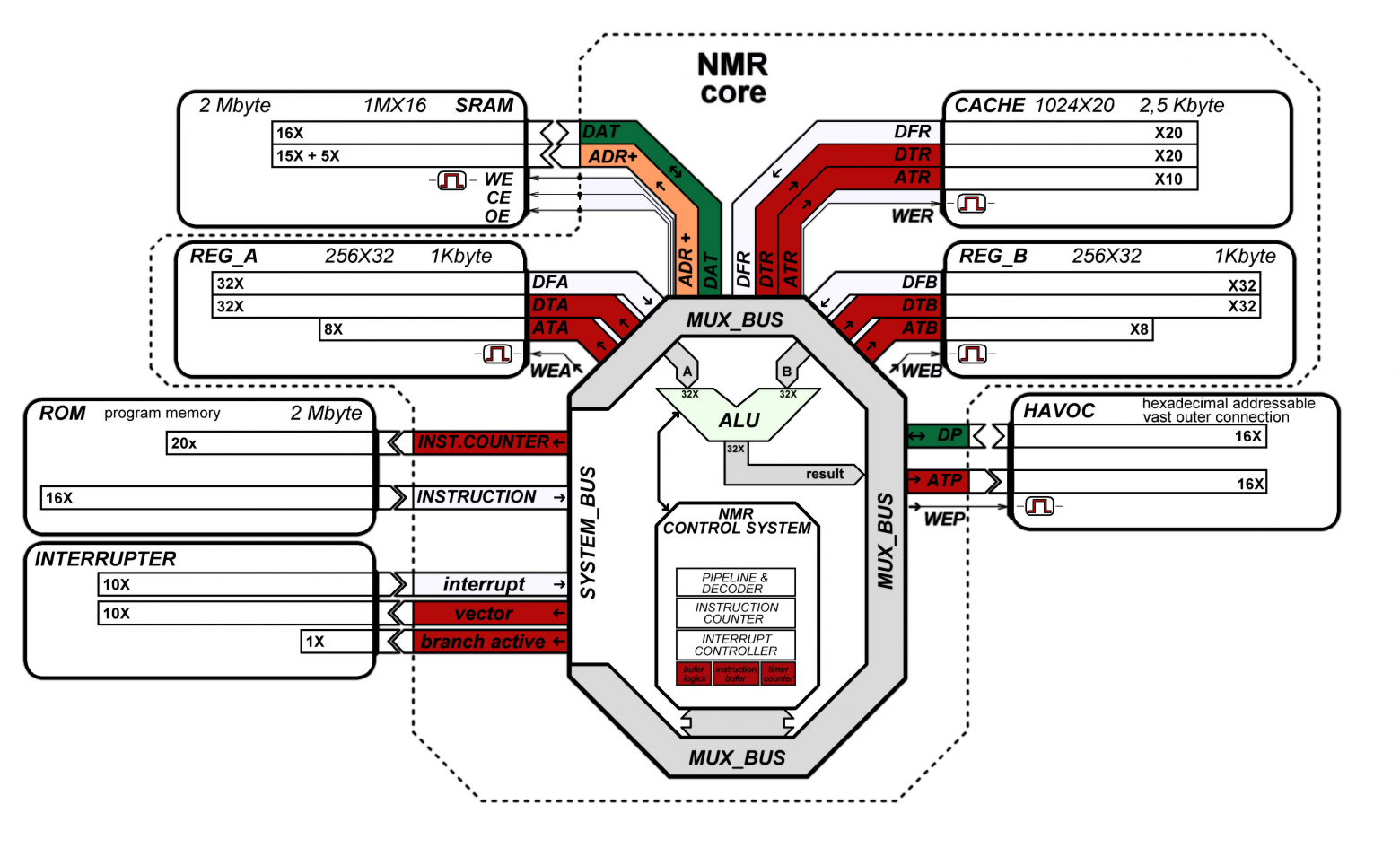

Простое, нестандартное процессорное ядро с открытым кодом, которое может быть использовано для создания микроконтроллера в базисе ПЛИС, в том числе ПЛИС - ОП.

Данная серия статей является туториалом по установке линукса на плату KC705 с софт-процессорным ядром Микроблэйз.

В первой части я описываю процесс создания схемы платформы, на которую мы поставим систему, с описанием некоторых нюансов.

Во второй части я опишу процесс сборки образа линукса и тестирование его работоспособности на отладочной плате путём прошивания через usb.

В третей — расскажу о том, как прошить SPI флэшку на плате, чтобы система стартовала сразу при включении платы.

Буду рад любым советам, замечаниям и фидбэку в комментариях. Статью считаю полезной, т.к. в процессе столкнулся с достаточно большим количеством неочевидных вещей, настроек и решений, информацию о которых в интернете нашёл с трудом. Да и вообще, актуальных туториалов и статей, конкретно по этой отладочной плате в интернете ничтожно мало. Поехали!

ПЛИС-Культ привет FPGA хабрунити!

Очередной движ по программируемой логике состоится с конца ноября по вторую неделю декабря в Мск, СПб и Томске/Омске

Приглашаем всех разработчиков и мимопроходилов принять участие в очередной конференции FPGA-Systems 2023.2 и в создании контента для первого номера журнала полностью посвященного проектированию на ПЛИС.

В данном цикле статей будет представлен процесс разработки и тестирования RTLмодулей на языке Verilog. В качестве примера будет рассмотрен целочисленный

сумматор с AXI-Stream интерфейсами. Мы разберем некоторые приемы и паттерны,

часто используемые при проектировании цифровых устройств. Также мы покажем

типовую структуру тестового окружения для проверки RTL-модулей.

Описанное нами окружение будет состоять из отдельных компонентов, у каждого из

которых будет своя конкретная задача. При правильном подходе к разработке этих

компонентов их можно будет повторно использовать в других тестовых окружениях.

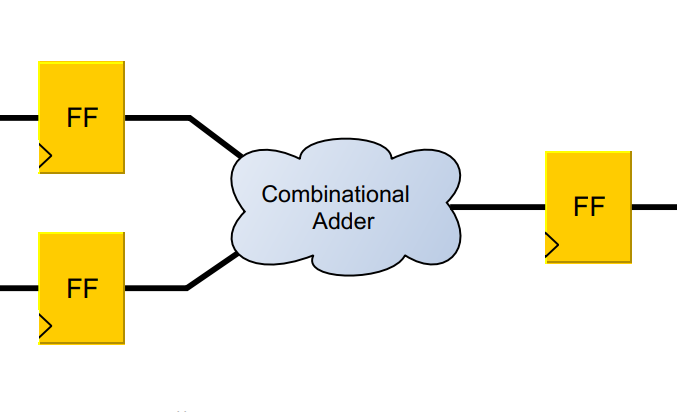

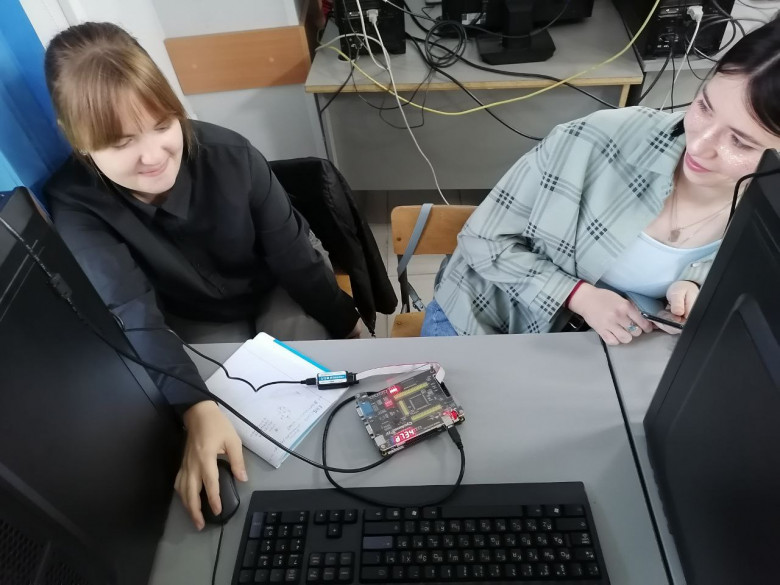

Прошли первые три занятия Школы Синтеза Цифровых Схем в 18 вузах России и Беларуси. На втором занятии пошла речь о D-триггерах и их описании в современном SystemVerilog, а не в стареющем Verilog-2001 и не в допотопном Verilog-95.

D-триггер - это минимальный элемент состояния, он хранит 1 бит информации в течении 1 такта. Именно он делает электронику "умной", позволяет повторять вычисления, ждать события, организовывать конвейеры вычислений внутри микропроцессора, графического процессора, сетевого роутера.

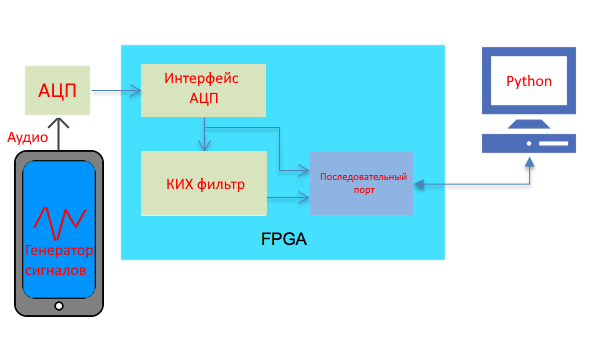

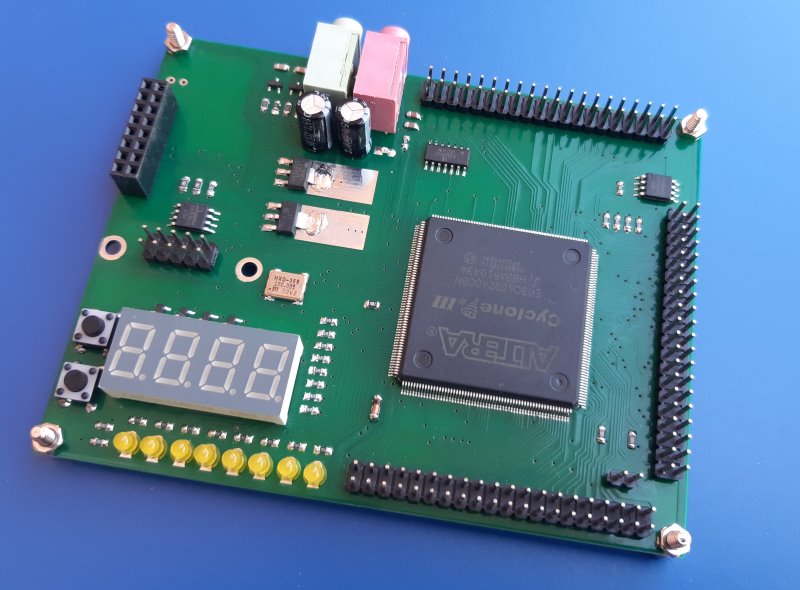

В своей предыдущей статье я написал, как произвести оцифровку звукового сигнала FPGA платой MCY316. В том проекте данные полученные из АЦП просто передавались в компьютер через последовательный порт. Уже на компьютере данные принимались из последовательного порта программой на питоне и отрисовывались в окне.

А сейчас я хочу модифицировать этот проект и добавить в FPGA еще цифровой фильтр, чтобы разобраться, как он работает.

Рисунок выше показывает схему моего эксперимента.

В эти выходные в Silicon Valley прошла парти на 400 человек под названием GPT-Party, из которых все 400 человек говорили по-русски (когда ведущий спросил кто не говорит, никто не поднял руку).

На парти выступали основатели ИИ компаний, русские венчурные капиталисты (Давыдов, Шойфот, Орешкин), украинские венчурные капиталисты (Сорока) , а также креаторы контента (Алекс Кролл). Креаторы говорили, что из-за ChatGPT всех инженеров выгонят с работы и останутся только бармены и креаторы контента.

Под конец самый богатый человек на парти, основатель ABBYY Давид Ян - посягнул на проблему сознания. В качестве показателя прогресса ИИ в этой области Давид приводил решение компьютером задачек, в которых нужно ставить себя на место других людей. Типа (это не задачка Яна, а мой аналог приведенных им задачек):

В 2023 году появилось много всего интересного, связанного с FPGA. Компании ставят рекорды, выпускают новые чипы и разрабатывают технологии, которых не было раньше. Сегодня обо всём этом и поговорим. Что же, самое интересное — под катом.

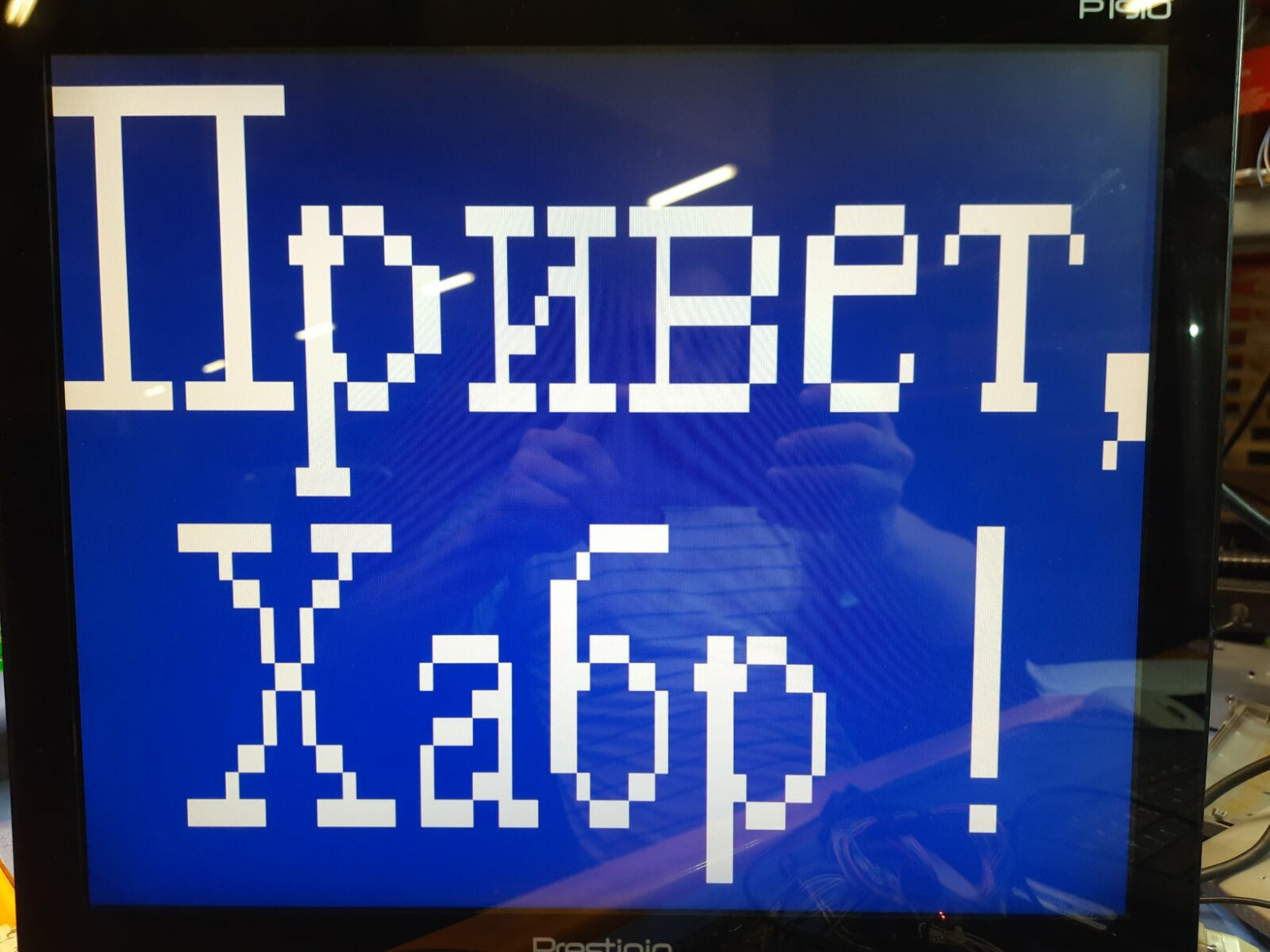

В субботу прошло первое занятие Школы Синтеза Цифровых Схем. Записалось 650 человек в 15 городах России и Беларуси, пришли 400 (250 офлайн и 150 онлайн). Российский флаг на мониторе нарисован комбинационной логикой FPGA (первое что пришло в голову рисовать студентам сразу в двух кластерах). Вообще обычно на первом занятии мигают светодиодами, но мы решили пойти дальше и показали им как рисовать картинки. Для этого два счетчика формируют X и Y, а задача студента - реализовать функцию RGB (X, Y).

Из-за наличия зоопарка плат, версий Windows и Linux, а также EDA софтвера, глючных программаторов, и при этом свежих и недотестированных bash-скриптов, возникла ситуация полного ада, особенно у онлайн-пользователей (преподаватели на местах героически справлялись). Возникла ошибка, которая меня реально удивила. И не только меня:

Гугл переводит английское слово embarrassment как "смущение", но для британцев это не просто смущение. Для них это сродне ощущение во сне, в котором вы приходите на экзамен совсем не готовым и при этом голым. Когда британцы проводят семинар с какими-нибуть платами в далекой стране, они панически боятся, что плата не заработает и будет embarrassment. Поэтому они стараются использовать один тип плат в фиксированной конфигурации, если всего этого нельзя избежать вообще и просто показывать плату издалека.

В глубине души британцы завидуют русским, которые "able to cope with difficulties". И вот вам свежий пример: когда выяснилось, что на более чем 300 заявок (UPD: сейчас уже больше 600) на Школу Синтеза Цифровых схем в 15 российских кластерах (UPD: уже 19, из них один белорусский) не хватает FPGA плат, группа волонтеров реализовала возможность легкого портирования учебных примеров на зоопарк из более чем 20 типов плат от Intel FPGA, GoWin и Xilinx, с идеей расшириться до 50 типов, с креативным добавлением недорогих внешних устройств.

На данный момент гегемония видеокарт в сфере машинного обучения кажется незыблемой - вычисления на них просты и эффективны. Но так ли они оптимальны? Это отнюдь не очевидно. Ограничения архитектуры для многих незримо, но принципиально влияют на развитие всей области знания. Однако и разумной альтернативы пока никто не предложил.

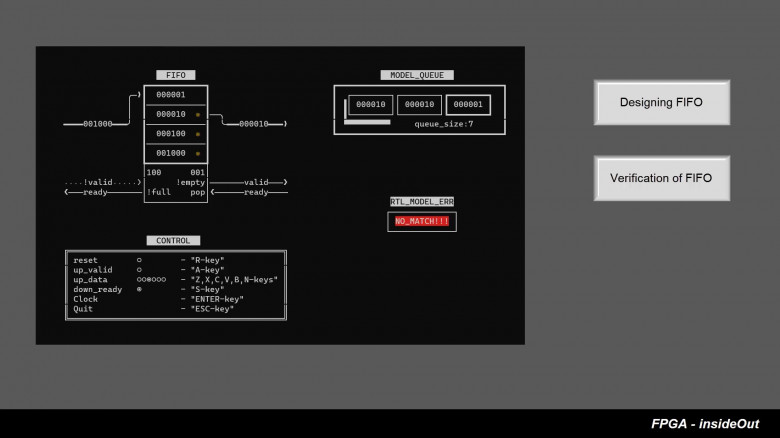

FIFO – ключевая концепция в хардварном дизайне. Понимание работы FIFO необходимо, в частности, для понимания протокола valid/ready, который в свою очередь необходим для организации flow-control как внутри цифровых блоков так и на межблочном уровне.

К сожалению по данной тематике очень мало литературы. Да и что говорить, микроархитектурные концепции достаточно сложно освоить по книгам. Понимание данных концепций это по сути выработка хардварной интуиции приходящая с практикой.

Микроархитектурный тренажер дает возможность «прощупать» хардварные сценарии в пошаговом (интерактивном) режиме, предоставляя детальную визуализацию цифровой логики.

Поскольку тренажер является "фронтендом" для HDL симулятора то на самом симуляторе исполняется реальный, синтезируемый SystemVerilog который можно посмотреть и даже поменять его функциональность.

Введение

В этой статье я хочу рассказать, как построить матрицу перехода для генератора псевдослучайной последовательности (PRBS - pseudorandom binary sequence). Данная задача особенно актуальная для реализации генератора на ПЛИС, где требуется за минимальное время (один такт) рассчитать как можно больше значений. Также данный метод позволит сократить время перехода на нужное состояние генератора в случае, если расчет производится на процессоре (микроконтроллере).

Несмотря на то, что предпосылки к отставанию закона Мура от экспоненты обсуждаются ещё с 90‑х, сам закон, с рядом оговорок, справедлив и в наши дни. Это приводит к тому, что если человек поступил в университет в 2010 году, то первые микроконтроллеры STM32F1, выпущенные в середине 2007 года, имели заметные шансы не попасть в его учебные курсы. Как, впрочем, и памяти DDR3 (стандарт также вышел в середине 2007‑го). В момент же получения человеком диплома в 2015‑ом, стандарту DDR4 исполнилось бы три года, STMicroelectronics только что выпустила бы серию STM32F7 со встроенным графическим модулем, а сами STM32 уже два года как имели возможность программироваться при помощи MATLAB и Simulink, минуя код на Си (если верить рекламе).

Подобное положение вынуждает динамично актуализировать знания.

Академические курсы не всегда успевают за прогрессом. А их первоисточник — техническая документация — бывает крайне обширна. Например, базовая документация на микроконтроллеры STM32F103xB насчитывает 1252 страницы. Помимо неё имеются ещё 54 документа типа application note и десятка полтора документов других типов. Поэтому достаточно востребованным источником знаний оказываются профильные сообщества.

Для эффективного получения знаний в подобных сообществах проблема должна быть сформулирована максимально качественно. Ещё в 2001 году появилось (и было переведено на множество языков) фундаментальное руководство «Как правильно задавать вопросы на технических форумах». Представляется, что тезисы данного руководства во многом универсальны и актуальны как для сообществ программистов, так и для сообществ электронщиков, туристов, кулинаров или художников. Однако столь же универсален феномен, когда ответ на сформулированный в соответствии с духом этого руководства вопрос, оказывается не ответом по существу, а чем‑то «идентичным натуральному ответу по существу». Об этом феномене и пойдёт речь в настоящей статье.

Сегодня в некоторой русско-американской группе по QA (я не даю ссылку потому что она закрытая, хотя и многочисленная) некий молодой человек задал вопроc как войти в Quality Assurance Automation. Я сказал, что могу показать путь в Design Verification, который является фактически специализированным QA в области проверки функциональности цифровых аппаратных блоков, спроектированных с помощью синтеза из кода на языке описания аппаратуры SystemVerilog (я их собственно и проектирую). Так как получить ответ захотело еще человек десять, я понял, что нужно писать пост. К счастью, я об этом писал более 10 лет, так что можно делать выжимки из предыдущих постов.

Карьера Design Verification Engineer с писанием сред тестирования на SystemVerilog может понравится опытным программистам, которые хотят сменить карьеру с например писания программ на Джаве. В SystemVerilog есть элементы объектно-ориентированного и симулированно-многопоточного программирования. Суть деятельности заключается в создание фреймворков, которые тестируют хардверные дизайны на прочность, бомбардируя их превдослучайными транзакциями и учитывая покрытие интересных сценариев (functional coverage).

В России не любят Линукс. Студенты и корпорации всячески отлынивают его использовать, даже если Линукс насаждают преподаватели или госзаказчики. Но есть область, в которой Линукс придется полюбить. Это разработка микросхем. Даже внутри Apple и Microsoft инженеры используют Synopsys Design Compiler / IC Compiler и Cadence Genus / Innovus, у которых вообще нет версий для Windows и MacOS, только для Linux. Да, я знаю, что Synopsys и Cadence ушли из России. Но даже открытые тулы для синтеза ASIC - Open Lane - есть только под Linux.

Я уже несколько лет использую для семинаров по FPGA загружаемые через USB SSD диски, на который ставится весь необходимый софтвер. Такое решение позволяет избежать агонии первого дня семинара, когда приходит куча народу со своими ноутбуками, три часа ставят Quartus, а потом мучаются с драйверами USB Blaster для китайского контрафактного клона, который без танцев с бубном не хотят поддерживать не Win10, ни Linux, ни особенно Win11, который хочет подписанные драйверы.

А как же виртуальные машины? - спросите вы. С моей точки зрения они вносят дополнительный уровень танцев с бубном. И это не мое дремучее мнение - так же считает мой приятель, который работал над виртуализацией в Микрософте. То оно USB порт не пробивает, то еще какие-нибудь глюки. Плюс учить дополнительные опции, качать и копировать файлы в десятки гигабайт. А тут вставил в USB порт, и если загрузится, то заработает.

Конечно, загружаемые SSD тоже не без проблем: тут и Legacy BIOS boot против UEFI boot, и Secure Boot с Bit Locker, и зловещий "хвост GPT", и отрубание всего из-за скачка напряжения в USB хабе - но с этими проблемами мы методично разобрались. Решение я и описываю в этой заметке, предназначенной в первую очередь для учеников и руководителей кластеров в Школе Синтеза Цифровых Схем, которая начинается с сентября в 14 российских городах (объявления и точных дат еще нет, но уже записалось 200 учеников).

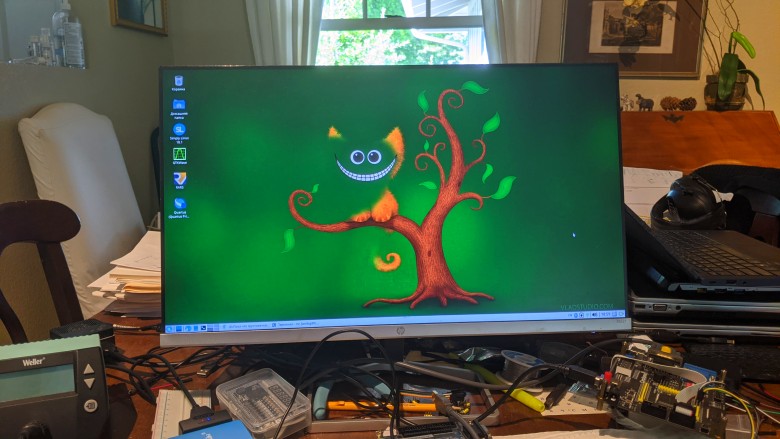

Прежде всего: как выглядит загружаемый SSD? А вот так: