Comments 91

До cs11047.vk.me/u88317703/-14/z_76fa2485.jpg, после cs10760.vk.me/u88317703/-14/z_d5e30b8d.jpg

FPGA это круто, но для специфичных задач.

Поковырять ПЛИС было всегда интересно, но задачи так и не придумал.

С другой стороны. сымитировать простейший эрзац-процессор — это реально круто для обучения, но уже такой advanced уровень.

Построить простейший процессор — это на самом деле не advanced уровень, для этого есть пошаговая инструкция в книжке, которая через месяц должна появиться на русском языке — Digital Design and Computer Architecture, Second Edition, 2012 by David Harris & Sarah Harris.

Странный подход, давайте еще художники сразу Adobe Photoshop будут изучать.

Что Arduino, что это, не могут чему-то обучить, помочь, да могут, но обучить нет. Только кнопки жать и работать по шаблону, а самому системно думать, сомневаюсь. Соглашусь с eta4ever. Да и дорого.

Вы в Xilinx работаете?

Я согласен с eta4ever, что изучать азы стоит начинать с серии 155, чтобы человек почувствовал, что такое логический элемент, триггер и сигнал тактовой частоты. А потом перелезть на ПЛИС.

Простейший студенческий процессор чисто на серии 155 строить муторно, а вот на ПЛИС-е совершенно реально даже на непродвинутом уровне.

Я работаю в компании Imagination Technologies, инженером в группе разработки процессора MIPS I6400.

а самому системно думать, сомневаюсьСистемно думать учат в университетах на теоретических курсах. А то что автор описал — практическое к тому приложение.

И мне кажется, что при грамотном подходе, школьник в конце концов должен что на ПЛИС, что на микроконтроллере, что на DSP одинаково хорошо работать. А ещё и разбираться когда какой из указанных типов смех применить лучше.

Не уверен, что это лучше, чем честное программирование зарубежных Xilinx.

ПЛИС нужны части студентов технических специальностей, не более того.

А что касается отечественной элементной базы, то вот именно ПЛИС — это один из самых сложных продуктов, который, как мне кажется, в России разрабатывать и производить просто бессмысленно. Делать надо что-то такое, на чем реально заработать денег. ПЛИС к таким продуктам явно не относится.

С нуля влезть в этот рынок сейчас невозможно, хуже только x86-совместимый процессор делать.

В России просто ни у кого нет достаточных программистских ресурсов, чтобы софт для ПЛИС написать.

И кто говорит, что надо во все школы? Достаточно в каждый технический ВУЗ. А если сидеть и ждать, и не осваивать современную элементную базу, а то а) нашей вообще никогда не возниктет и б) мы безнадежно отстанем в отрасли в общем.

Да, если эти 265 млн вложить в разработку отечественной элементной базы, то ситуация улучшиться. Если не вкладывать, то точно не улучшится.

САПР свой делать не обязательно, если open source нормальный есть.

habrahabr.ru/post/156843/

habrahabr.ru/post/218171/

habrahabr.ru/post/217427/

и поймете, почему эти 265 млн р. НИЧЕГО не сделают для российской микроэлетроники. И лучше эти деньги вложить в воспитание кадров в этой области.

Для российских реалий тех процесс 90 нм — это потолок. При том, что современные ПЛИС делают уже по технологии 14-22 нм на фабриках (TSMC, Intel) стоимостью в миллиарды долларов. Причем доступ российских дизайнеров микросхем к этим технологиям на этих фабриках закрыт.

И нормального open source для FPGA нет.

Работаете в сегодняшних реалиях и достигайте успеха. Может быть этот успех в конечном итоге и приведет к возрождению отечественной микроэлетроники, кто знает… Но не надо искусственно вкачивать в нее деньги, как в Автоваз…

Вот цитата из BarsMonster (http://habrahabr.ru/post/218171/)

Кроме того, Intel уже более 40 лет доходы от продажи процессоров реинвестирует в усложнение технологии, владеют кучей патентов — и чтобы сейчас достичь их уровня в равных условиях (налоги, бюрократия, доступность капитала) понадобилось бы по моей грубой оценке порядка 352 млрд$ и 30 лет работы — на что конечно никто пойти не может. Всем нужен свой Intel за 0.1, а лучше 0.01млрд$ :-)

Однако по тем же причинам и для США затруднительно создать свою технологию разделения урана центрифугами и строить ядерные энергетические реакторы на быстрых нейтронах. Так что где-то они побеждают, где-то мы, где-то Китай — нужно развивать то, где есть преимущество и не перенапрягаться там, где для достижения паритета пришлось бы потратить все ресурсы страны на 1 компанию.

надо перестать жить с имперскими амбициями по принципу осажденной крепости

С чего вы взяли? Я вот совершенно не против, если Россия станет планетарной державой (ну не будет других стран на планете). А про осажденную крепость — почему-то все дома свои забором огораживают / дверь в квартиру запирают, вот и государство стенку иметь должно, а то мало ли кто «в гости» заскочит. При этом дружить с соседями очень даже полезно.

у любого мирового продукта обязан быть отечественный аналог

Это конечно не реально, только вот когда врезапно например кредитные карточки прекращают обслуживаться, так сразу об отечественном аналоге думают. Может стоит наконец подумать до появления проблем. Думать-то не запрещено, вдруг решение какое-то придумается.

Автоваз

Который год езжу — приличная машинка. Проходимость — суперская (пусть и не полный привод), в обслуживании дешевая, и бензина много не кушает. Да, есть недостатки — сыпется по мелочам, зато вы на цену (в том числе и ремонта) посмотрите. То что автоваз государство поддерживает — ничего страшного, кого государство считает нужным, того и поддерживает. Во многих странах кого-нибудь, да поддерживают.

нужно развивать то, где есть преимущество и не перенапрягаться там, где для достижения паритета пришлось бы потратить все ресурсы страны на 1 компанию

Гармонично надо развиваться, а не развивая дальше только то, что получилось. Когда развиты несколько областей, это даёт развитие смежным. В результате вся экономика развивается.

Эти деньги не изменят вообще ничего.

*** А вообще обучать школьников целой страны программированию на иностранной элементной базе как-то обидно (прямо-таки для иностранных держав будем специалистов готовить). ***

Но ведь потом школьники будут делать российские разработки на Verilog, так что игра стоит свеч.

*** И мне кажется, что при грамотном подходе, школьник в конце концов должен что на ПЛИС, что на микроконтроллере, что на DSP одинаково хорошо работать. А ещё и разбираться когда какой из указанных типов смех применить лучше. ***

Да, вот это именно то, что нужно.

Но ведь они куда-то должны прошивки заливать? Будут опять импортное закупать.

А вот мир ASIC чрезвычайно замкнут. Открытого софта нет и потренироваться реальной возможности нету. Покупать софт при его стоимости занятие неоправданное, пока нет заказа на разработку. С ломаным софтом тоже проблемы. А кто ж возьмется за заказ не имея навыков работы. В общем замкнутый круг…

Проблем со стоимостью софта, например, нет у университетских дизайн-центров. У них, правда, софт есть, а вот с заказами проблемы.

А также открытый софт, пригодный для того, чтобы потренироваться, вполне себе существует.

vl2mv и VIS — компилятор Verilog, симулятор и синтезатор (http://vlsi.colorado.edu/~vis/)

SIS — оптимизирующий синтезатор с отображением в технологическую библиотеку (http://embedded.eecs.berkeley.edu/Alumni/pchong/sis/)

TimberWolf — размещение (http://opencircuitdesign.com/magic/archive/timberwolf-6.3.1.tgz)

qrouter — трассировщик (http://opencircuitdesign.com/qrouter)

Magic — просмотр топологии (http://opencircuitdesign.com/magic/)

IRSIM — симулятор для верификации конечной топологии (http://opencircuitdesign.com/irsim/)

Самая большая проблема — это верификация топологии, особенно если речь идет о суб-100 нм проектных нормах.

Плюс есть еще Tanner EDA, которые делают софт полного цикла за деньги, на порядки меньшие, чем у «большой тройки».

www.tannereda.com/

Там, конечно, больше упор на Mixed-signal (потому что с большими массивами цифровой логики их софт пока не справляется), но тем не менее.

Ну и, если есть какой-то конкретный интерес к заказным микросхемам — в личку черкните, может чего полезного расскажу.

Несколько лет преподавал относительно новый для нашей кафедры курс «Основы цифровой обработки сигналов на ПЛИС». К сожалению, ЦОС там и не пахло, все лабораторные были исключительно на помигать светодиодами, переключать кнопочки, сделать ту или иную логическую функцию. Самая сложная работа (она же и зачетная) — сделать простое FIFO или КИХ-фильтр определенного порядка по ТЗ.

Мы со студентами делали проекты на отладочной плате «Spartan3E starter kit».

Вот результаты опыта:

1. За отведенное время на это курс студенты не успевают разобраться ни в языке программирования, ни в приложениях от Xilinx. Плюс предмет читается на 5 курсе, когда все уже работают.

2. В связи с этим интерес у большинства падает уже на первых занятиях, поскольку нужно проделать много самостоятельной работы.

3. Работы делались по принципу — «самый умный сделал, у него скопировали проект и отчитались». Сдал — забыл.

4. Реально заинтересованных в ПЛИС было 1-2 человека на 4 группы. К счастью, они смогли сделать зачетные задания (FIFO, синтез КИХ в матлабе и реализация в CoreGenerator).

5. Творческие задачки на ПЛИС студентам нравились больше, по крайней мере интереса к реализации фильтра почему-то интерес проявили больше, чем к помигать светодиодами.

Вот и в этом семестре придет очередная порция студентов, и даже не знаю, сколько человек проявят интерес.

Итог: новичкам, (особенно студентам) очень тяжело быстро и сразу въехать в тему с ПЛИСами. Тут скорее нужно много энтузиазма, чем усилий, чтобы интерес не упал на самых первых порах. Но лично мое мнение — если хочется влезть в ПЛИС, то желательно изучать именно в студенческое время, а курс растянуть на семестра два-три (для профильных специальностей в магистратуре).

Но одного семестра для изучения такого курса реально мало, а показать за один семестр все не удается (а очень хочется!). Надеюсь, что в будущем этот курс у нас расширят.

Из опыта тоже могу сказать, что в первом семестре нельзя допускать никакой самодеятельности — все должны делать одно и тоже с серьезным контролем (т.е. время очень мало, материла много, и если туда-сюда смотреть и тыкаться, то ничего не успеют).

И главное — живо вести предмет, с реальными примерами, для чего нужны ПЛИС. Тогда процент заинтересовавшихся и оставшихся в теме на следующих курсах студентов будет больше.

А по поводу Vivado HLS — отдельный респект. У меня на основной работе еще очень скептически относятся к высокоуровневому программированию под ПЛИС, хотя я периодически проталкиваю идею начать те же FIR-фильтры или DDC делать на Си. А в институте вообще мало кто это поймет.

Вам выделили девкиты на Zynq или 7 серии?

По поводу Vivado HLS — тут надо взвешивать все за и против. Если вы нацелены на использование ПЛИС для схем управления приборами или в качестве каких-то интерфейсных схем, то может его и не надо использовать.

Этот транслятор хорош, когда надо на одном кристалле решать разные задачи, например в области HPC, где ПЛИС — это ускорители вычислений, или в DSP области. Тогда появляется реальный выигрыш от того, что существенно уменьшается время на разработку.

Наш курс все-таки нацелен на использование ПЛИС в качестве ускорителей вычислений, поэтому Vivado HLS и изучаем.

Мы периодически решаем задачи ЦОС с реализацией перестраиваемых DDC/DUC, фильтров сжатия, быстрой свертки и т.д. на ПЛИС. Поэтому время разработки критично. Если его минимизировать использованием HLS без потери в производительности и при тех же затратах ресурса кристалла — будет просто здорово!

Честно говоря, у меня большие сомнения в эффективности результата для более-менее сложных алгоритмов, но сам не щупал.

Можете что-то посоветовать?

Знаю, что у Altera такой же транслятор на подходе. Другие трансляторы имеют существенный недостатки.

Коммерческие Catapult C, Impulse C — дороги

Открытые LegUp, ROCCC, C-to-Verilog — синтезируют откровенно плохие схемы.

Периодически смотрю вебинары по SV, но дальше проекта обычного ШИМ руки не дошли.

VHDL тоже имеет ряд плюсов, но разводить холивар на эту тему не хочется. Язык программирования(будь то VHDL, verilogv SV, или C++) — это инструмент. И самое главное, это уметь им грамотно пользоваться. :)

cs621317.vk.me/v621317996/8033/HRWEv3jF7Us.jpg

Я часы на 155/561 серии собирал еще в 8-9 классе, они до сих пор идут на даче. Со светодиодным индикатором. Кварц, счетчики, всё как положено. И в то время компьютеров не было, идешь в библиотеку, берешь справочник.

Логические вентили это даже проще чем программирование. Есть же визуальные редакторы схем для плис. Нарисовал, нажал «прошить» и оно работает.

Напишите еще цикл статей по использованию всех приложений от Xilinx. Буду их показывать в качестве дополнительного обучающего материала :)

Например,

— создание примитивных IP-ядер в Coregerator, их интеграция в проект.

— задание временных ограничений, правильное описание UCF (XDC) для ног ПЛИС, для компонентов внутри кристалла при включенной иерархии, (тут можно всю мощь PlanAhead и FPGA Editor подключить), и т.д и т.п.

Сам вот думаю написать про интеграцию блоков из System Generator и Matlab на примере динамических систем.

Если на уровне блок-схем, то у меня как-то руки не поднимаются писать [про те проекты, в которых я участвую], кажется что, материала на хорошую статью не особо хватит. Если разбирать код, то руководство может сделать атата, если буду сливать исходники в интернетах)

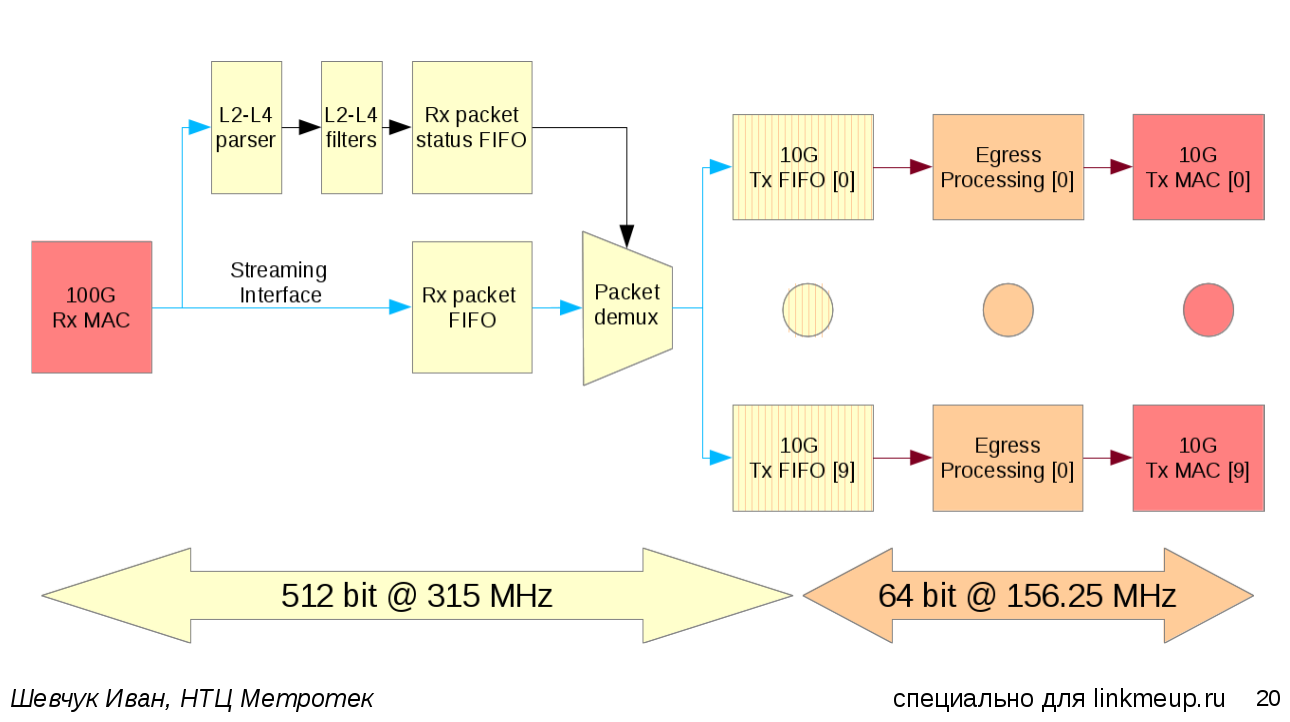

Не так давно вместе с коллегой были в гостях у Марата eucariot ( habrahabr.ru/post/246753/ ), где я рассказывал о применении FPGA в конкретном проекте: 100G Ethernet балансировщик ( с функцией фильтрации ). Позволю себе привести слайд из презентации «блок-схемы»:

Если будет интересен рассказ о проектах в формате похожих блок-схем (ну или чуть подробных ), то почему нет? :)

По поводу Cx — я знаком с двумя десятками подобных тулов, так как сам был автором подобного тула еще в середине 1990-х годов — см. мой патент на эту тему — www.patents.com/us-6226776.html

С точки зрения обучения ценность данного класса тулов имхо сомнительная. Дело в том, что с моей точки зрения студента нужна научить двум ключевым концепциям — конечным автоматам и конвейерности, а тулы типа Cx скрывают конечный автомат (они извлекают его их софтверноподобной последовательности действий), а также делают конвейер не-наглядным (если конвейерность вообще поддерживается в Cx).

Что касается pyhdl, я посмотрел его и он показался мне очень многословным — слишком много текста, больше, чем в Verilog. Кроме этого, я подозреваю, что у него могут быть пролемы с временем симулирования на нетривиальных дизайнах. Вообще я видел несколько попыток сделать HDL средствами других языков (включая даже Lisp), но ни один из них не получил распостранение кроме SystemC, который тоже RTL-дизайнерам не нравится, но был навязан индустрии массированным маркетингом от Synopsys в течение многих лет.

Какой путь трансформаций проходят исходники (*.v файлики) с момента написания до момента попадания в Flash память FPGA?

подобно программированию на С(ях), где цепь такая

*.с->*.obj->*.elf->*.bin->OnChipNorFlash

Какая "пищевая цепочка" файлов в ToolСhain(е) для FPGA?

Можно ли представить схему на языке Dot?

Начинают с VHDL/Verilog, а потом там происходит многоэтажная проприетарная магия, которая иногда заканчивается файлом битстрима (непрозрачный набор байтов для заливки на чип), а иногда даже и там security through obscurity, и только программатор знает, что ему предыдущая проприетарщина нагенерировала.

Для двух с половиной чипов формат битстрима отреверсили и сделали опенсорсный набор утилит для компиляции высокоуровневых языков в него. Там вроде бы как промежуточные этапы это логические примитивы (RTL), которые потом компилируются в битстрим конкретного чипа. Подробнее, кажется, тут.

Как начать разрабатывать железо, используя ПЛИС — пошаговая инструкция