Author

Vladislav Grigorev

Introduction

A stopwatch is a timepiece designed to measure the amount of time that elapses between its activation and deactivation. It's often used in sports, cooking, or other timed events. Clock is a non-portable timepiece used to keep track of time. The key difference lies in their functionality: a clock continuously measures the time, while a stopwatch can be started and stopped to measure the duration of specific events.

A stopwatch is a widely used device for measuring time intervals. It's often used in sports, cooking, or other timed events. Clock is a non-portable timepiece used to keep track of time. The key difference lies in their functionality: a clock continuously measures the time, while a stopwatch can be started and stopped to measure the duration of specific events.

There are mainly two types of stopwatches implementations available, which are mechanical and digital. Mechanical stopwatches are powered by a mainspring, which must be wound up by turning the knurled knob. Digital stopwatches, due to their crystal oscillator timing element, are much more accurate than mechanical timepieces. Each type has its own unique features, making them suitable for different applications.

The key advantage of FPGAs is their high response speed and reliability, thus resulting in a more precise stopwatch system. We are not the first ones addressing such an FPGA-based stopwatch implementation ([1], [2]). However, the key advantage of our approach is that our stopwatch is able to count up to one hour without any delays, providing an accurate timekeeping experience. The use of a peripheral LED scheme enhances the visibility of the counting process, making it easy for users to monitor time progression. Furthermore, the ability to pause, continue, and stop the stopwatch offers flexibility and control to the user. This makes our implementation suitable for a wide range of applications where precise time measurement and control are required.

During the implementation process, we faced a problem known as button bounce. This phenomenon caused random interference when attempting to record saved loops.

Hardware and software used

This project is implemented by using the following devices and technologies (see Appendix Figure 2).

Altera MAX 10 FPGA device

Buttons and switches (input devices)

LEDs and 7-Segment display (output device)

5V Power USB-Blaster (power supply for FPGA and upload firmware)

Peripheral devices

RGB LED (state indicator)

Set of LEDs (time flow representation)

Transistors (burnout protection)

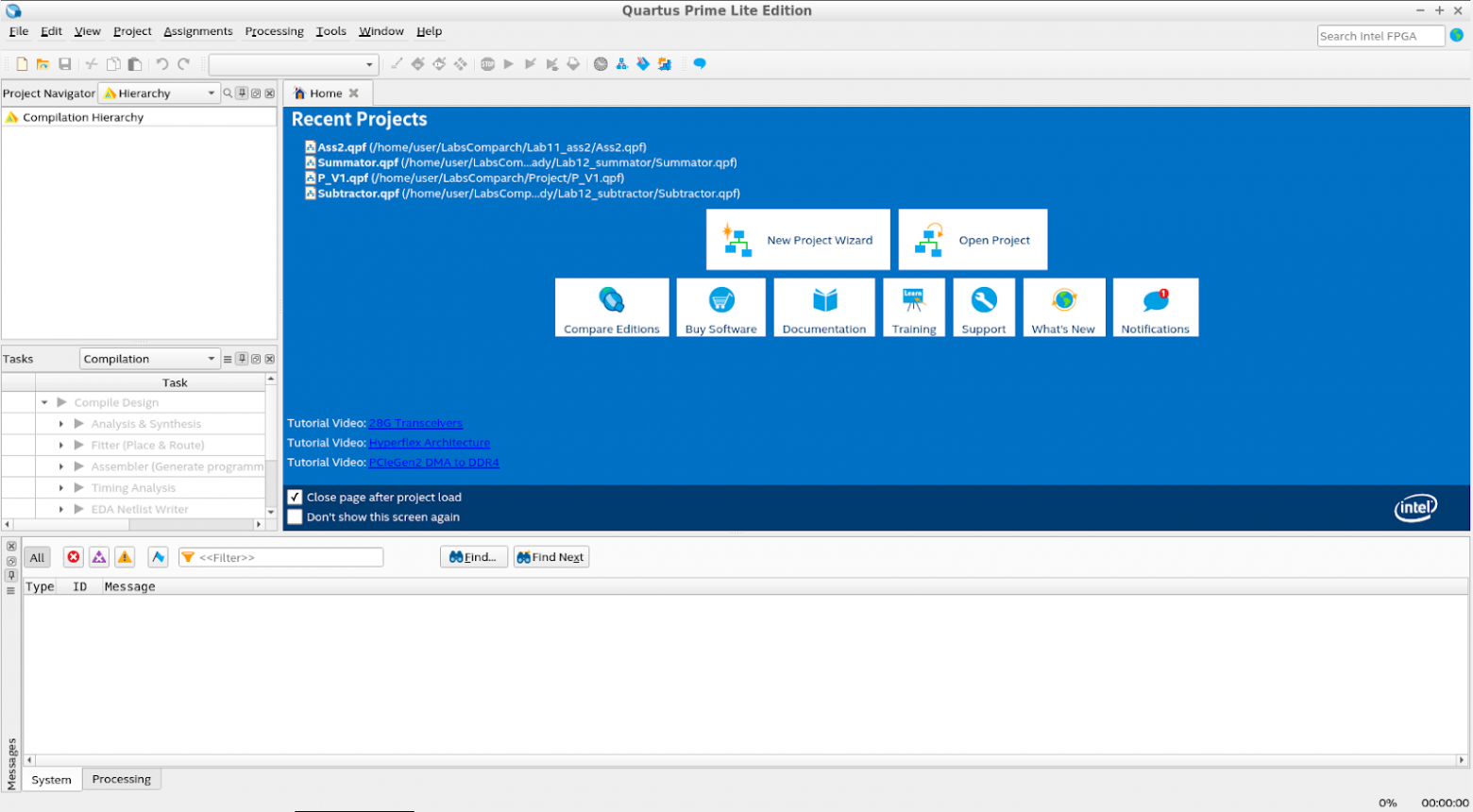

Quartus Prime Light Edition 21.1.1

Verilog HDL (hardware description language)

Technical implementation

3.1 Finite state machine representation (FSM) of the program execution.

The diagram (Figure 1) shows the flow of the program. The circles are states, arrows are transition conditions.

Figure 1: Program flow states.

3.2 Displaying the state of the program

LED indicates whether the stopwatch is active or paused. MAX 10 has a row of the named LEDs. In our case “LEDR0” is responsible for the indication of active state of countdown, flashing every second (see Appendix Figure 3).

In addition the RGB LED (see Appendix Figure 4) was connected via Arduino connector to indicate all the states of the stopwatch (Default/Pause - red, Active - green, Loops check - blue).

For the better interpretation of the time flow, we decided to add a circuit with a row of additional LEDs of different colors (see Appendix Figure 5), which sequentially change their flashing state. To prevent the burnout of the LEDs, the circuit was supported by resistors.

3.3 Time display

The main time counting is tracked via a 7-segment digit display. Each segment is represented as a unique output pin (see Appendix Figure 6). To simplify the process of the numbers output, we decided to create an array of 10 elements, which contained a binary representation of each digit from 0 to 9. The problem was that the values of each segment were inverted. Proper values have been handpicked by ourselves manually.

3.4 Clock

The frequency of the clock update is 50 MHz, which means it makes 50 * 106

cycles per second. Taking this into consideration we update our display each 1 centisecond i.e. each 500.000 ticks.

3.5 Schmitt trigger

To move between stages we use buttons. Generally every button has a bounce effect (see Appendix Figure 7), some electrical noise generated as the button rapidly oscillates between states immediately after a button is pressed but before it settles. To overcome this problem we use a special schmitt trigger integrated into the FPGA board.

Demonstration

Step-by-step instruction

Install Quartus Prime 21.1.1

Open Quartus Prime 21.1.1

Quartus Prime 21.1.1

New project wizard

Press "Next" (This section may not be displayed if you disabled it earlier).

Choose the directory for your project, set some name for the project, set "top" as

top-level entity. Press "Next" (Directory, Name, Top-Level Entity).

Select "Empty project". Press "Next" (Project type).

Press "Next" (Add Files).

First, choose your device family in the "Family" list. Second, select your device in the "Available devices" list (Usually the device name is written on an FPGA, in other words, on a big black square). Finally, press "Next" (Family, Device & Board Settings).

Press "Next" (EDA Tool Settings).

Press "Finish" (Summary).

Create all files and copy paste corresponding code from GitHub using following approach: File >> New >> Verilog HDL >> OK >> copy paste the code >> File >> Save as... >> set corresponding to code name >> Save

Project Navigator >> Files >> Choose your file >> Set as Top-Level Entity.

Project Navigator.

Processing >> Start Compilation.

Assignments >> Pin planner.

Close Pin planner.

Tools >> Programmer >> Hardware setup >> Select your device.

Close Hardware setup.

Press Start.

Done, stopwatch installed on your device.

Conclusion

The project has reached completion and fully meets the declared functionality. Future development could focus on addressing the button bounce issue. In conclusion, we have detailed the basic implementation of a stopwatch using an FPGA board, Quartus Prime software, and Verilog HDL. This project was undertaken as part of the “Computer Architecture” course at Innopolis University. The primary goal of this project was to create a functional stopwatch, and to foster teamwork and enhance our skills in FPGA programming.

Acknowledgments

Also I would like to express gratitude to our professors Artem Burmyakov and Alexander Tormasov for giving deep knowledge and possibility to use it in practice.

References

[1] Design and implementation of digital clock with stopwatch on FPGA

[2] Implementation of DIgital Clock Stopwatch on FPGA

[3] Max-10 manual

Appendix

Figure 2: The schematic representation of an FPGA board.

Figure 3: LEDs arrangement.

Figure 4: RGB LED during state 5.

Figure 5: Additional circuit of LEDs.

Figure 6: 7-segment display.

Figure 7: Button “Bounce”