Ссылка на русскую версию / link to Russian version

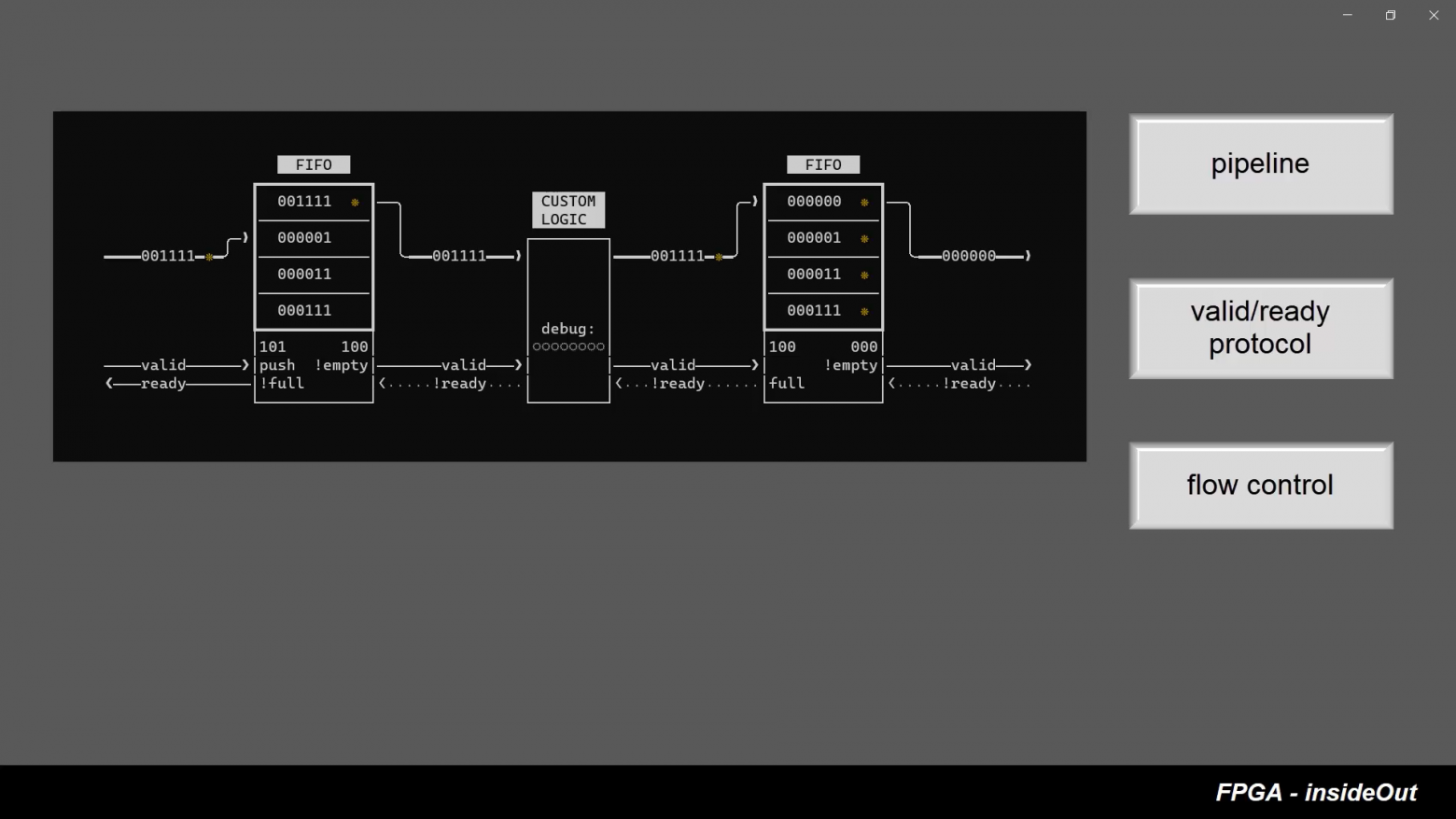

Understanding valid/ready protocol is extremely important for every microarchitect.

Valid/ready is one of the main protocols used to organise flow-control inside a logic block as well as on inter-block (SoC) level.

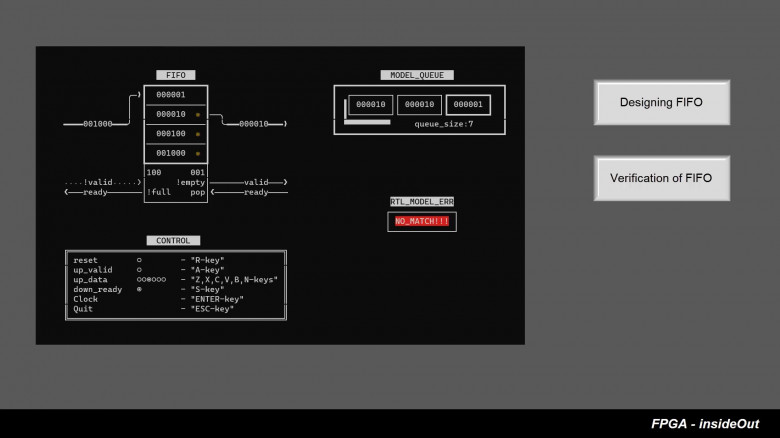

In the last lesson, we explored FIFO buffer using hdlgadgets - human-in-the-loop HDL training tool.

This time we will take two FIFO buffers (which form a pipeline with valid/ready handshakes) and will experiment with it by changing flow-control logic of the pipeline.

We will show that valid/ready is not only a mechanism for transferring data from one FIFO queue to another, but also a method for organizing various kinds of logical functionality between queues.

If you have not worked with valid/ready protocol before, you will be surprised how easy it is to achieve desired functionality of the design by simply writing couple of lines of Verilog code in the handshaking logic block between two FIFOs.