Это седьмая статья из цикла и заключительная в блоке, посвящённом трассировке сигнальных линий. Дальше есть идея развивать проект и выходить на руководство по проектированию печатных плат в виде удобной книги, поэтому по публикациям, возможно. будет пауза. В статье рассматривается важная тема — дифференциальная схема передачи данных, получающая всё большее распространение в современных системах, и предлагаются рекомендации по трассировке дифференциальных пар, позволяющей обеспечить преимущества этой схемы.

Bogdan @pbo

ECAD Application Engineer

SamsPcbGuide, часть 1: Оценка индуктивности элементов топологии печатных плат

8 мин

27KПредисловие

В поисках ответов на вопросы, возникающие при проектировании печатных плат, мною был изучен значительный объём литературы – как больших монографий, так и отдельных технических статей. За исключением, наверное, нескольких статей, это была англоязычная литература. Я подумал, а почему бы не оформить накопившийся опыт в виде практического руководства, которое может оказаться полезным как начинающим, так и, надеюсь, более опытным отечественным разработчикам. Начиная, я думал о распространении ценной информации, а краем мысли и о вкладе в отрасль в целом. Настоящая публикация открывает целую серию статей, в которых с практической точки зрения будут рассмотрены основные задачи, возникающие при разработке печатных плат, и в систематизированном виде изложены ключевые рекомендации с обязательным указанием их физических основ и условий применимости.

+27

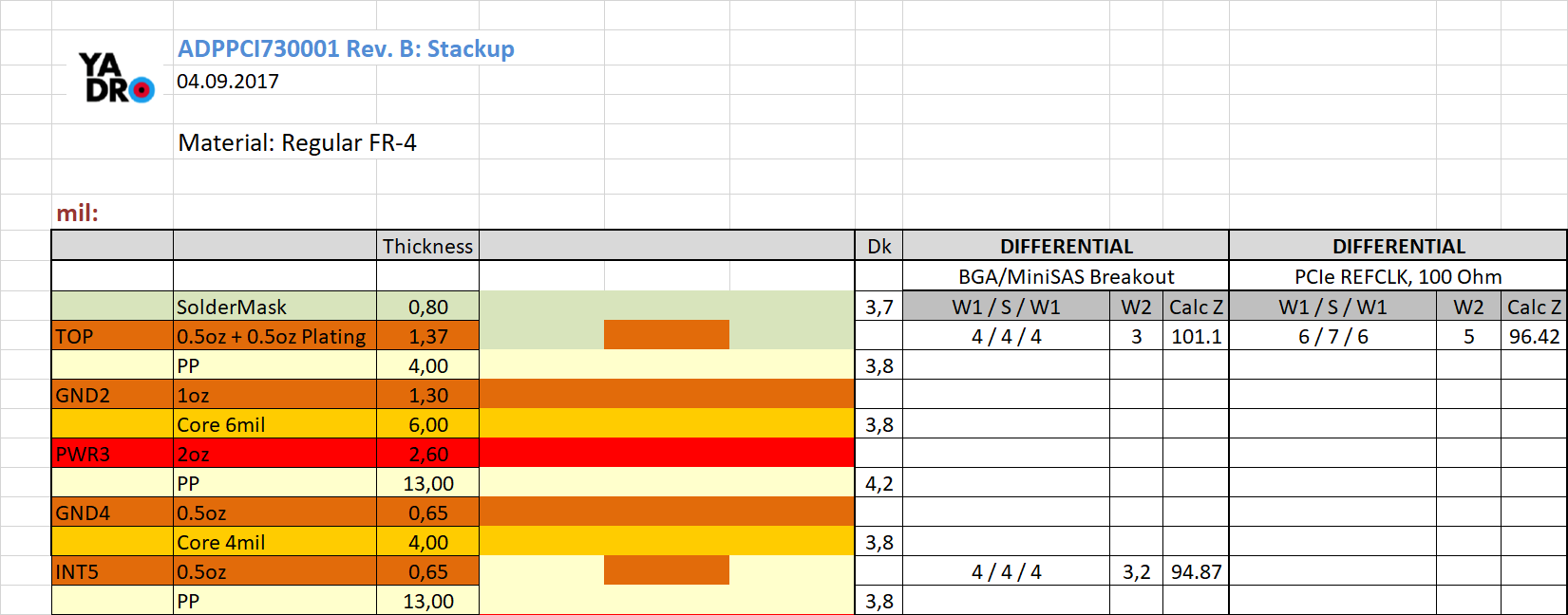

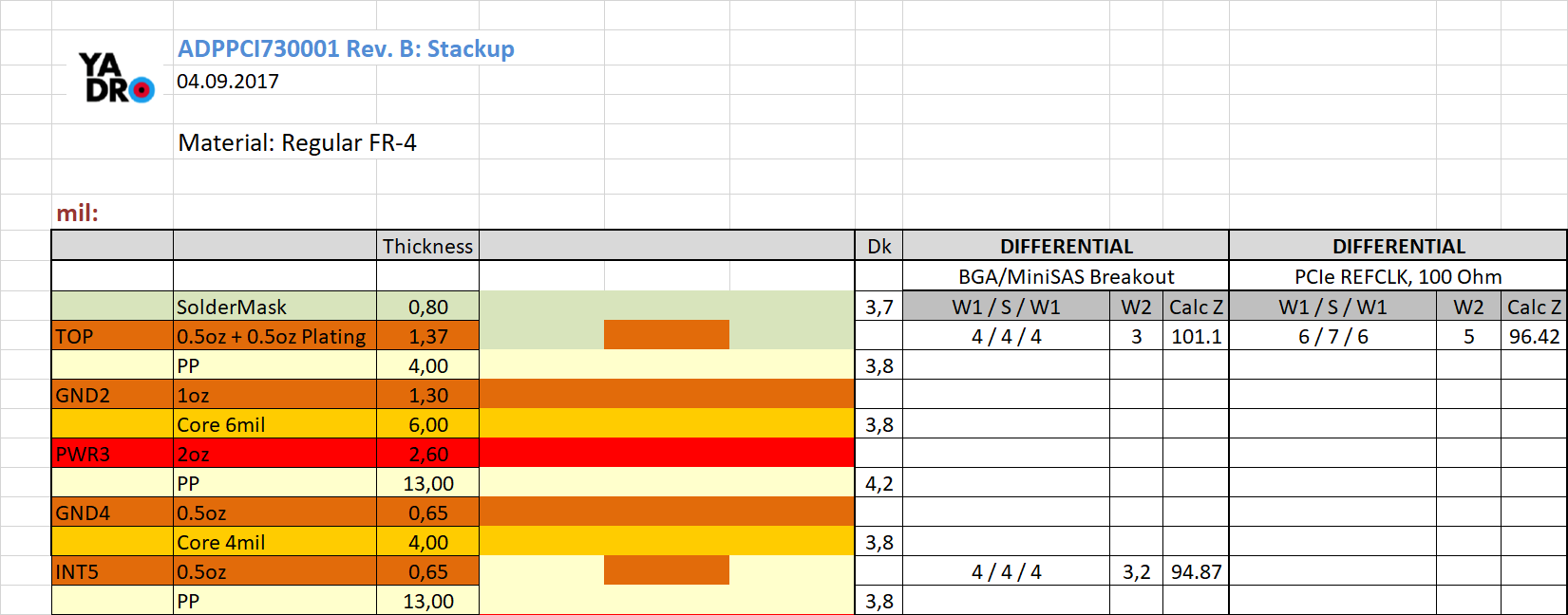

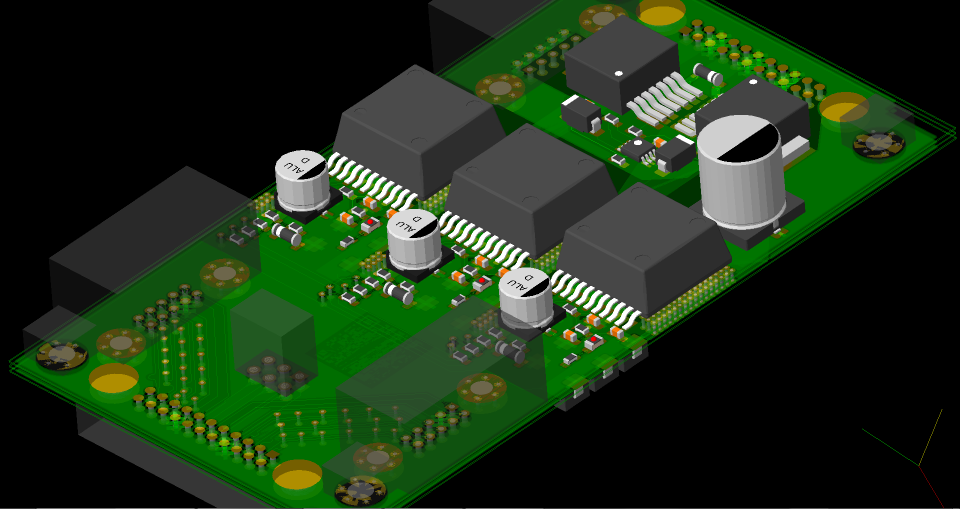

Наша методика расчета стека печатных плат

7 мин

27KПока мы заканчиваем последние приготовления к серийному выпуску сервера VESNIN, хочу провести образовательный эксперимент — опишу наши внутренние методики и рекомендации для расчёта стека печатных плат. С одной стороны, приятно, если наш опыт будет кому-то полезен. С другой, мы сами рады получить дельные комментарии, чтобы улучшить нашу практику. Если интересно прочитать и обсудить — добро пожаловать под кат.

+31

Термобарьеры, надгробные камни и прочие прелести печатных плат

6 мин

154K

Пока крутые конструкторы проектируют правильные платы и заказывают производство на суперсовременных американо-европейских заводах, обратимся к опыту разработки печатных плат под возможности срочного производства одного из подмосковных (на самом деле Зеленоград – район Москвы) заводов с ручным подвальным монтажом (на самом деле ручные монтажники у них сидят аж на втором этаже, а в подвале стоит линия на 60,000 компонентов в час).

Дальнейший текст – личное мнение автора. Это не истина в последней инстанции, а лишь один из возможных срезов того огромного пласта информации, который доступен в настоящее время обычному конструктору.

+96

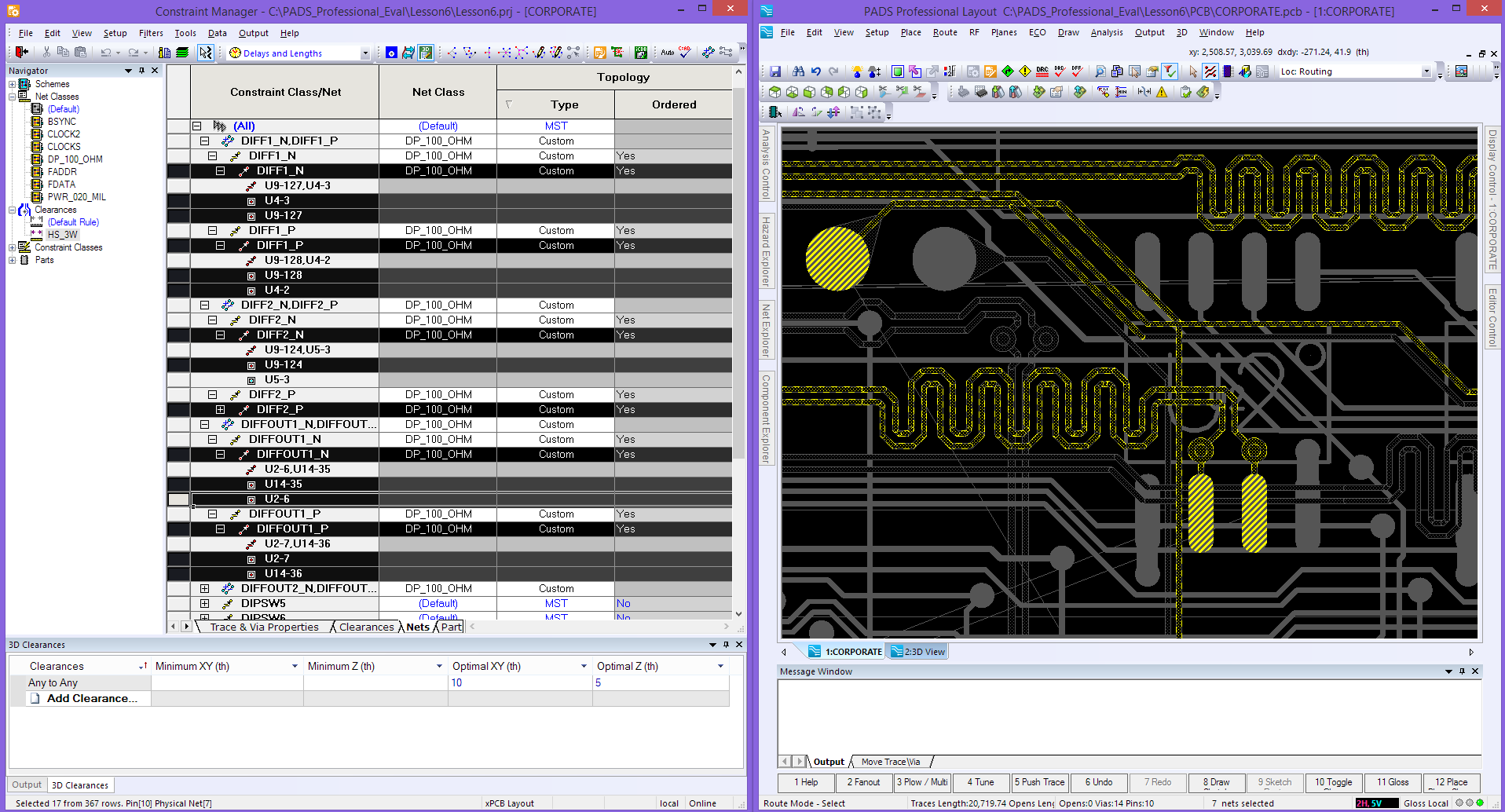

Настройка системы электрических ограничений для проектов, с использованием высокоскоростных интерфейсов

2 мин

6.6KТуториал

+11

Завтра мы начнём вас убивать, или Зачем нужны инженеры

12 мин

135KПривет, Хабр. Под этим пафосным заголовком я бы хотел поговорить о том, что такое «инженерная наука», в чём состоит главная обязанность инженера и что бывает, если он с ней не справляется — мне кажется, в последнее время эта тема становится всё более актуальной, при этом её публичного обсуждения я не вижу.

Сподвигла меня на это разразившаяся (при моём активном участии) в минувшие выходные история с «нейроинтерфейсами» компании Bitronics Lab — детскими учебными наборами для снятия ЭЭГ и мышечной активности, которые при ближайшем рассмотрении оказались попросту небезопасны в использовании из-за несоблюдения их производителем базовых требований к электробезопасности медицинского оборудования.

История это очень показательна в том, что она демонстрирует, как по мере роста сложности система, составленная из кажущихся её авторам безопасными компонентов, становится опасной — причём на примере системы простой, бытовой и интуитивно понятной, а не атомного реактора или реактивного лайнера, которые любят брать в качестве примеров авторы книг вроде моей любимой "Inviting Disaster".

Кроме того, с одной стороны, история эта с настолько счастливым концом, насколько возможно (производитель быстро признал проблему и сейчас работает над её решением), а с другой — вскрыла такие глубины, о которых многие и не подозревали, став из истории о технике историей о людях.

Итак, уважаемая российская компания, имеющая целую пачку не менее уважаемых партнёров, делает недешёвые, но пользующиеся спросом современные учебные наборы, используя для этого проверенные временем и считающиеся совершенно безопасными компоненты — Arduino, датчики, персональный компьютер.

Казалось бы, что может пойти не так?

Сподвигла меня на это разразившаяся (при моём активном участии) в минувшие выходные история с «нейроинтерфейсами» компании Bitronics Lab — детскими учебными наборами для снятия ЭЭГ и мышечной активности, которые при ближайшем рассмотрении оказались попросту небезопасны в использовании из-за несоблюдения их производителем базовых требований к электробезопасности медицинского оборудования.

История это очень показательна в том, что она демонстрирует, как по мере роста сложности система, составленная из кажущихся её авторам безопасными компонентов, становится опасной — причём на примере системы простой, бытовой и интуитивно понятной, а не атомного реактора или реактивного лайнера, которые любят брать в качестве примеров авторы книг вроде моей любимой "Inviting Disaster".

Кроме того, с одной стороны, история эта с настолько счастливым концом, насколько возможно (производитель быстро признал проблему и сейчас работает над её решением), а с другой — вскрыла такие глубины, о которых многие и не подозревали, став из истории о технике историей о людях.

Итак, уважаемая российская компания, имеющая целую пачку не менее уважаемых партнёров, делает недешёвые, но пользующиеся спросом современные учебные наборы, используя для этого проверенные временем и считающиеся совершенно безопасными компоненты — Arduino, датчики, персональный компьютер.

Казалось бы, что может пойти не так?

+224

Проектные нормы в микроэлектронике: где на самом деле 7 нанометров в технологии 7 нм?

12 мин

126KСовременные микроэлектронные технологии — как «Десять негритят». Стоимость разработки и оборудования так велика, что с каждым новым шагом вперёд кто-то отваливается. После новости об отказе GlobalFoundries от разработки 7 нм их осталось трое: TSMC, Intel и Samsung. А что такое, собственно “проектные нормы” и где там тот самый заветный размер 7 нм? И есть ли он там вообще?

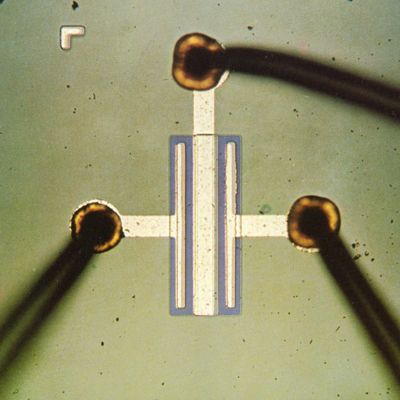

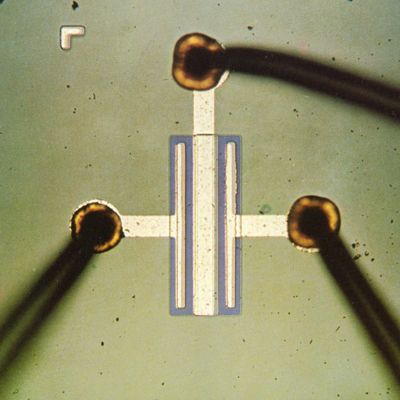

Рисунок 1. Транзистор Fairchild FI-100, 1964 год.

Самые первые серийные МОП-транзисторы вышли на рынок в 1964 году и, как могут увидеть из рисунка искушенные читатели, они почти ничем не отличались от более-менее современных — кроме размера (посмотрите на проволоку для масштаба).

Рисунок 1. Транзистор Fairchild FI-100, 1964 год.

Самые первые серийные МОП-транзисторы вышли на рынок в 1964 году и, как могут увидеть из рисунка искушенные читатели, они почти ничем не отличались от более-менее современных — кроме размера (посмотрите на проволоку для масштаба).

+157

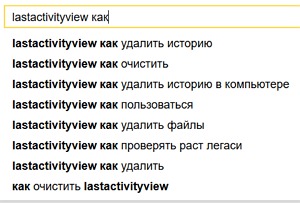

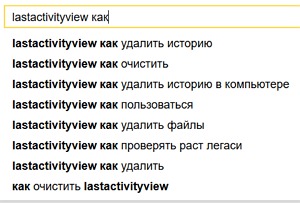

Forensic resistance 1 или Last-икActivityView. Данные об активности пользователя в Windows 10 и как их удалить

22 мин

40KДоброго времени прочтения, уважаемые читатели Хабра.

Побуждением к изысканиям, опубликованным в данной статье, стало набирающее все большую и большую популярность слово «форензика» и желание разобраться в вопросе — какие данные о цифровой жизнедеятельности рядового пользователя собирает ОС Windows 10, где их хранит и как сделать кнопку — «Удалить все» (Я бы взял частями, но мне нужно сразу (с) Остап Бендер).

А возникновению данного побуждения способствовало то, что, как оказалось, интерес к вопросу «как удалить историю», выдаваемую эпичной LastActivityView, до сих пор будоражит умы

при этом, зачастую, на форумах вопрос остается без ответа. Масла в огонь подливает то, что ванильный CCleaner в случае с LastActivityView не помогает.

Те, кому в основном интересна практическая сторона вопроса, насчет кнопки «Удалить все», могут сразу перейти к концу статьи — там предлагаю варианты решения.

А в статье — хочу поделиться результатами этих изысканий с теми, кого это заинтересует. Речь пойдет о тех данных, которые хранятся ОС Windows 10 локально и к которым можно просто и быстро получить доступ с использованием «бесплатных и общедоступных средств форензики», в том числе и утилит NirSoft. Хотя речь пойдет не о них (почему — смотреть ниже).

Побуждением к изысканиям, опубликованным в данной статье, стало набирающее все большую и большую популярность слово «форензика» и желание разобраться в вопросе — какие данные о цифровой жизнедеятельности рядового пользователя собирает ОС Windows 10, где их хранит и как сделать кнопку — «Удалить все» (Я бы взял частями, но мне нужно сразу (с) Остап Бендер).

А возникновению данного побуждения способствовало то, что, как оказалось, интерес к вопросу «как удалить историю», выдаваемую эпичной LastActivityView, до сих пор будоражит умы

при этом, зачастую, на форумах вопрос остается без ответа. Масла в огонь подливает то, что ванильный CCleaner в случае с LastActivityView не помогает.

Те, кому в основном интересна практическая сторона вопроса, насчет кнопки «Удалить все», могут сразу перейти к концу статьи — там предлагаю варианты решения.

А в статье — хочу поделиться результатами этих изысканий с теми, кого это заинтересует. Речь пойдет о тех данных, которые хранятся ОС Windows 10 локально и к которым можно просто и быстро получить доступ с использованием «бесплатных и общедоступных средств форензики», в том числе и утилит NirSoft. Хотя речь пойдет не о них (почему — смотреть ниже).

+22

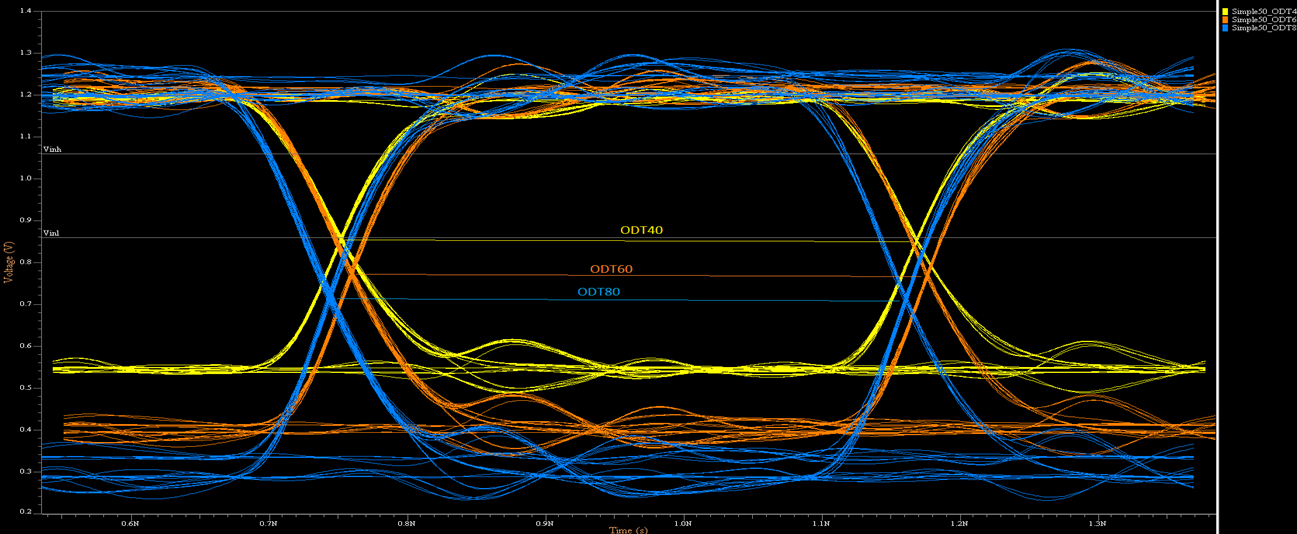

Полезные советы по использованию HyperLynx DDR Wizard для анализа QDR4

6 мин

5.8K

Quad Data Rate (QDR-IV) является стандартом высокопроизводительной памяти для сетевых применений и идеально подходит для нового поколения сетевых устройств, коммуникационного оборудования и вычислительных систем.

QDR-IV SRAM-память имеет встроенный блок обнаружения и коррекции ошибок (ECC), обеспечивающий целостность данных. Этот блок способен обработать все одноразрядные ошибки памяти, в том числе, вызванные космическими лучами и альфа-частицами. В результате модули памяти будут иметь коэффициент ошибок программ (SER) не более 0.01 сбоев/МБ. QDR-IV снабжена функцией программируемой чётности адреса, которая обеспечивает целостность данных на адресной шине.

Отличительные особенности QDR SRAM памяти:

- Встроенный модуль коррекции ошибок обеспечивает целостность данных и исключает программные ошибки

- Модули доступны в двух версиях: QDR-IV HP (скорость передачи данных 1334 Мтранз/с) и QDR-IV XP (скорость передачи данных 2132 Мтранз/с)

- Два независимых двунаправленных порта данных памяти DDR1

- Функция инверсии шины для снижения шумов при одновременном подключении линий ввода и вывода

- Встроенная схема согласования (ODT) снижает сложность плат

- Тренинг на перекос для улучшения временных характеристик захвата сигнала

- Уровень сигналов ввода-вывода: от 1.2В до 1.25В (высокоскоростная приёмопередающая логика (HSTL)/терминированная логика (SSTL)), от 1.1В до 1.2В (POD2)

- 361-выводной корпус FCBGA3

- Разрядность шины: x18, x36 бит

+15

Информация

- В рейтинге

- Не участвует

- Откуда

- Португалия

- Дата рождения

- Зарегистрирован

- Активность

Специализация

Technical Support Director, Technical Support Engineer

Lead

От 300 000 ₽

English

Electronics Development

Problem solving

Technical support

Development of integration solutions

CAD

Modeling

Public performance

Training

Business consulting