«Развернись на 180 градусов, проедь вперёд и включи фары»,

«Подъедь ближе к свету»,

«Если рядом ничего нет — проедь вперёд, потом поверни направо».

Хочется, чтобы даже игрушечные роботы понимали такие команды с полуслова. Без заученных фраз, без кнопок, без пульта. Нас к этому приучают голосовые ассистенты — Siri, Alexa, Алиса, но в DIY-проектах или любительской робототехнике такие интерфейсы встречаются редко, особенно когда речь идёт о чём-то более сложном, чем «вперёд» и «назад».

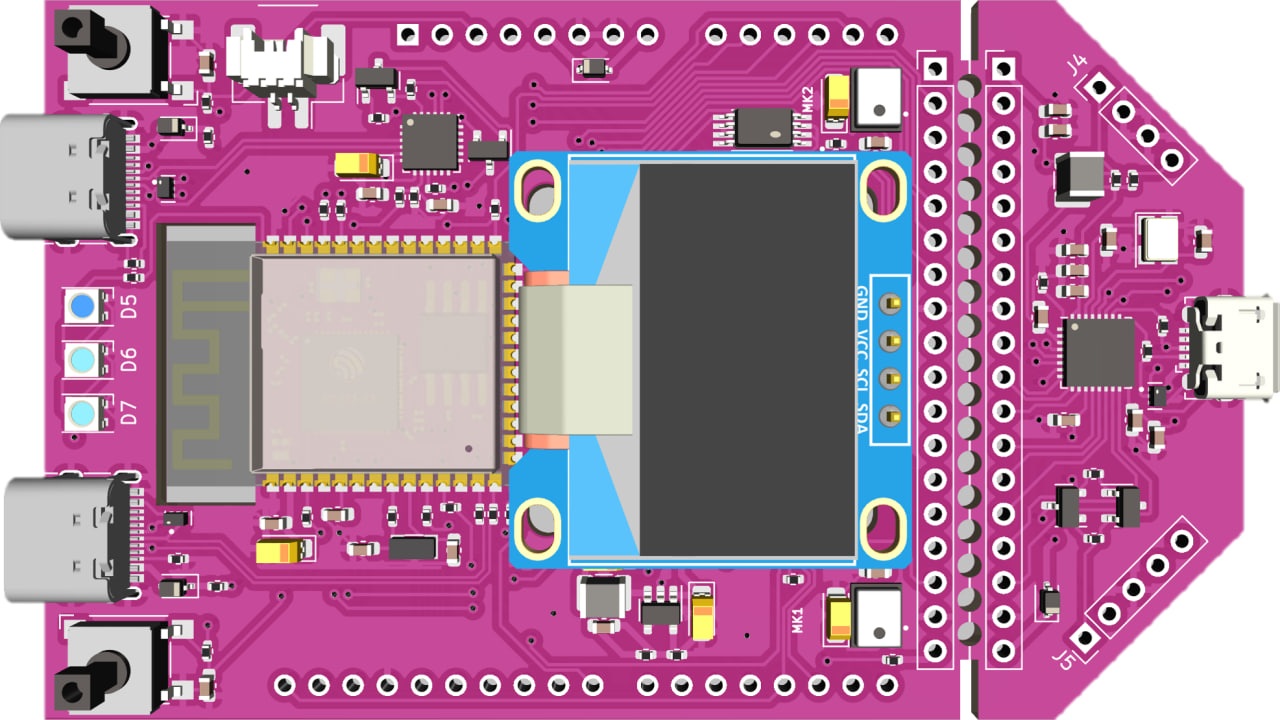

Готовых решений с распознаванием речи для различных устройств в продаже не нашёл, поэтому решил собрать всё самостоятельно. Получился контроллер для робота, который не просто «слушает», а действительно понимает команды.