Традиционно, говоря о косимулиции, имеют в виду моделирование систем, разные части которых представлены на разном уровне абстракции или написаны на разных языках. Например, SystemC-модели + RTL код, TLM-модели + RTL. При этом моделирование RTL-части может быть исполнено на симуляторе или в реальном времени на FPGA-прототипе. В последнем случае подразумевается существование некоторого интерфейса для транзакций между FPGA-платформой и хост-машиной, моделирующей остальную часть.

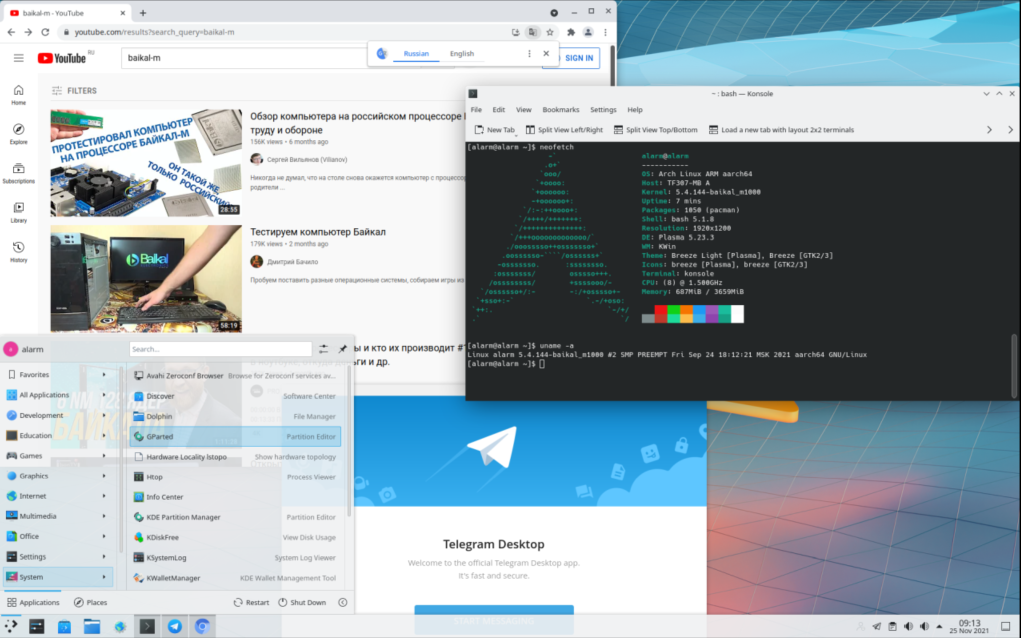

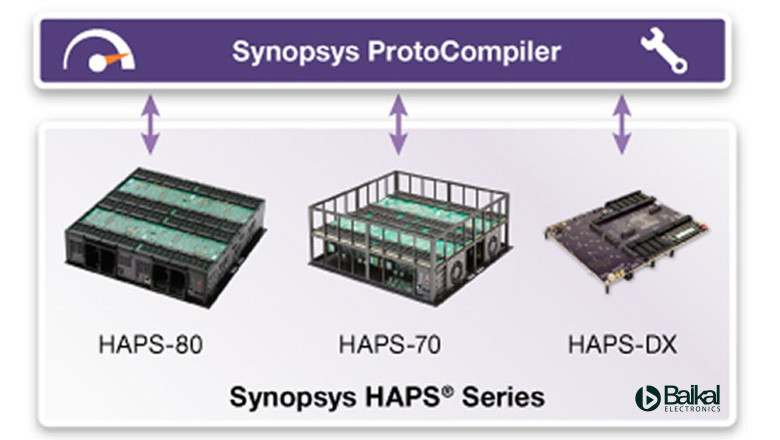

В «Байкал Электроникс» для FPGA-прототипирования используют платформы Synopsys HAPS®-80, позволяющие в процессе разработки микросхемы реализовать такие сложные сценарии, как загрузка ОС, что было бы невозможно выполнить RTL-моделированием в приемлемые сроки.

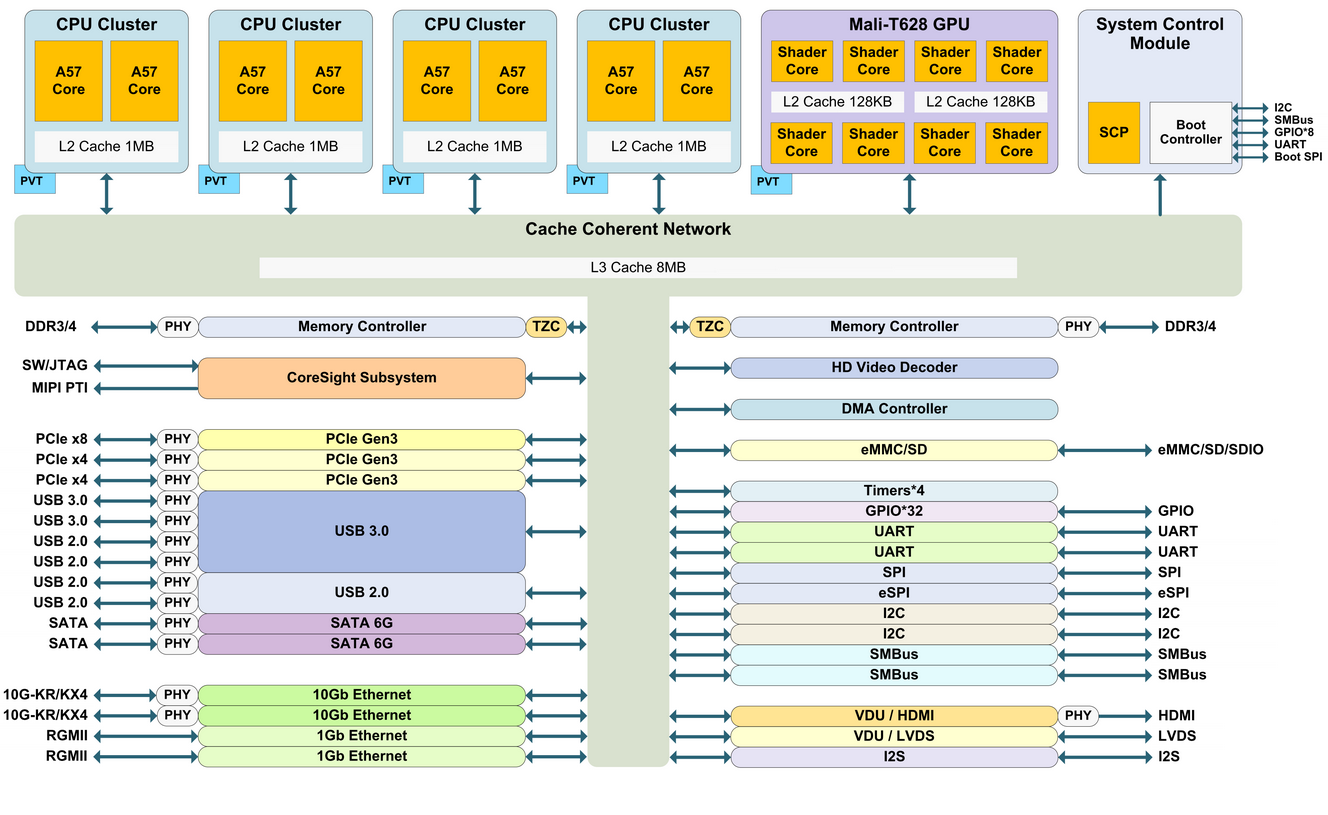

Но FPGA-прототипирование не может заменить RTL-моделирование в процессе полноценной верификации отдельных подсистем, так как на FPGA невозможно во всех нюансах воспроизвести поведение таких элементов будущей микросхемы, как, например, PHY-контроллеров интерфейсов. Также проблематично реализовать на FPGA работу количества частотных доменов, характерного для современных систем на кристалле.

Итак, в ряде случаев полноценное RTL-моделирование незаменимо, но как быть с огромными рантаймами? Например, моделирование программного кода трейнинга DDR4 может занимать 2 недели. Перед инженерами «Байкала» встал вопрос: а нельзя ли в этом верификационном окружении выделить ту часть, которая может быть полноценно синтезирована на FPGA-платформе, и осуществить косимуляцию несинтезабельной части на симуляторе с исполнением в real-time на FPGA синтезабельной части? Ведь очевидно, что львиная доля времени симуляции уходит на воспроизведение switching activity высокопараллельных структур, отлично портируемых на FPGA.