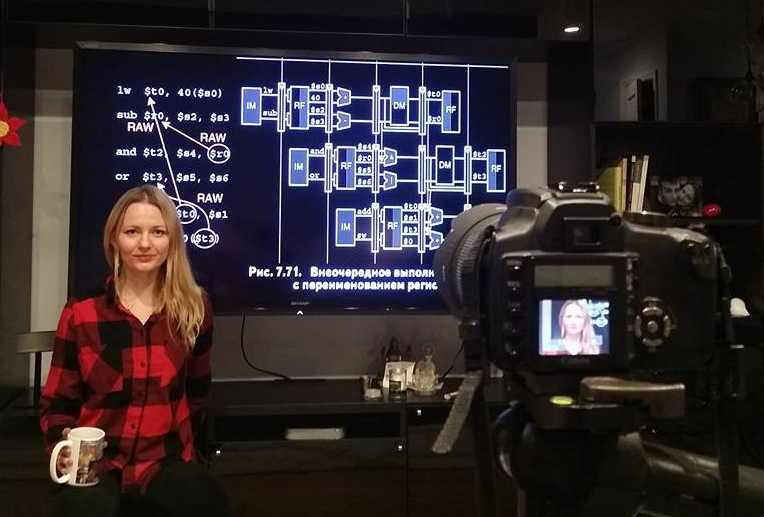

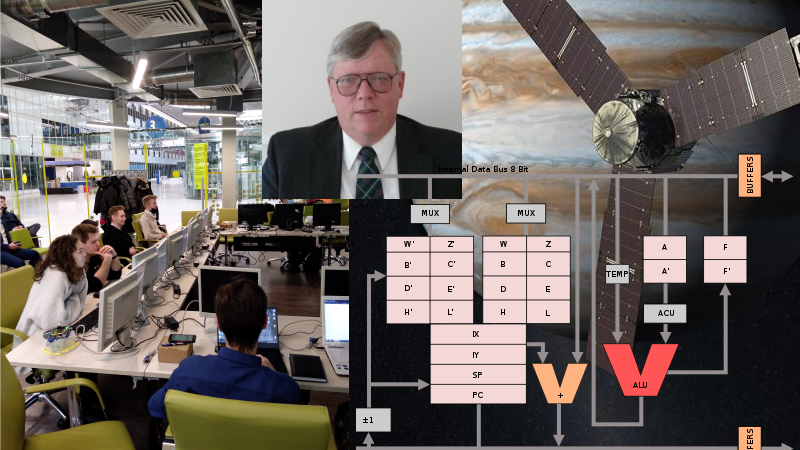

Что видит на своем экране проектировщик айфона в Купертино, Калифорния

Каждый год мы видим очереди фанатов, которым не терпится первыми прикоснуться к только что выпущенному новому айфону. А хотите узнать, как выглядит смартфон за два года до начала его продаж в магазине? Он в это время уже существует, как набор файлов в компьютерах проектировщиков его системы на кристалле.

Что же видит проектировщик Apple на своем экране? Завесу над этой тайной поможет над приоткрыть знаменитый в узких кругах блоггер Джон Кули (John Cooley), который начал свой вебсайт deepchip.com еще в 1990-е годы. Джон собирает всякие слухи, сливы и мнения тысяч инженеров больших электронных компаний, стартапов и контракторов, которые потом все это с большим интересом читают.

Когда-то в 2015 году, Джон опубликовал заметку "За закрытыми дверями", на основе анонимных емейлов от 36 инженеров. Аккурат в это время Apple переходил на собственные версии CPU и GPU (до этого Apple использовал готовые ядра от ARM и Imagination Technologies). Заметка выглядела так: