Являются ли программисты айтишниками? И является ли проектирование на уровне регистровых передач программированием?

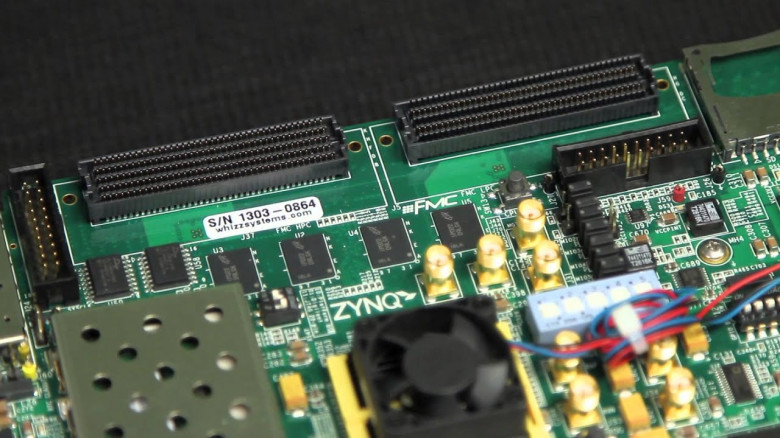

Перед нами девушка Лиля, с FPGA платой и учебником Харрис & Харрис в руках, на фоне самого высокого на Земле дерева Sequoia sempervirens, недалеко от Стенфорда в Silicon Valley.

Представьте, что вы приехали сюда в командировку в типичную электронную компанию. Усаживаетесь в офисе, входите со своего ноубука (в Америке их чаще называют лаптопами) в корпоративную сеть и пытаетесь что-то напечатать. А принтер не подсоединяется. Вы обращаетесь к ко-воркеру "Что делать?", а он вам говорит: "Обратитесь в IT". Вы в замешательстве "В Ай-Ти? А я что - не айтишник?"

Спокойствие. Если вы программист, вы не IT, вы software engineer и работаете в отделе Software Engineering Department. Если вы электронщик, вы тоже не IT, вы работаете в Hardware Engineering Department. IT Department - это другое, это отдельный от разработки отдел, это группа сисадминов, которые поддерживает внутри-корпоративную сетку и ведут учет выданых сотрудникам лаптопов.

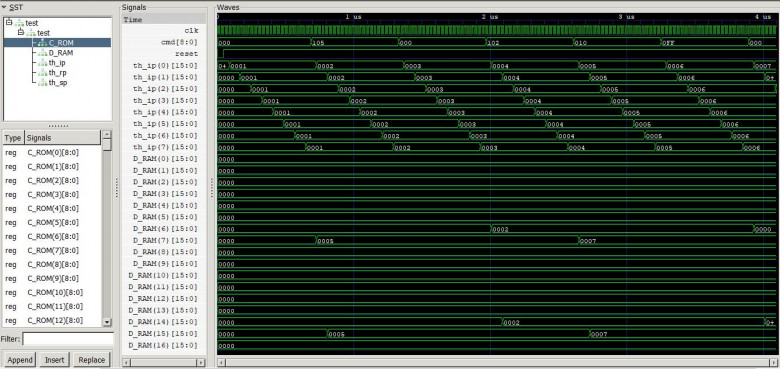

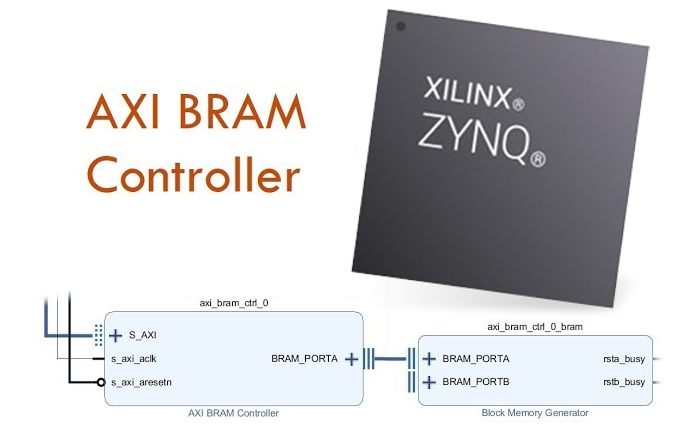

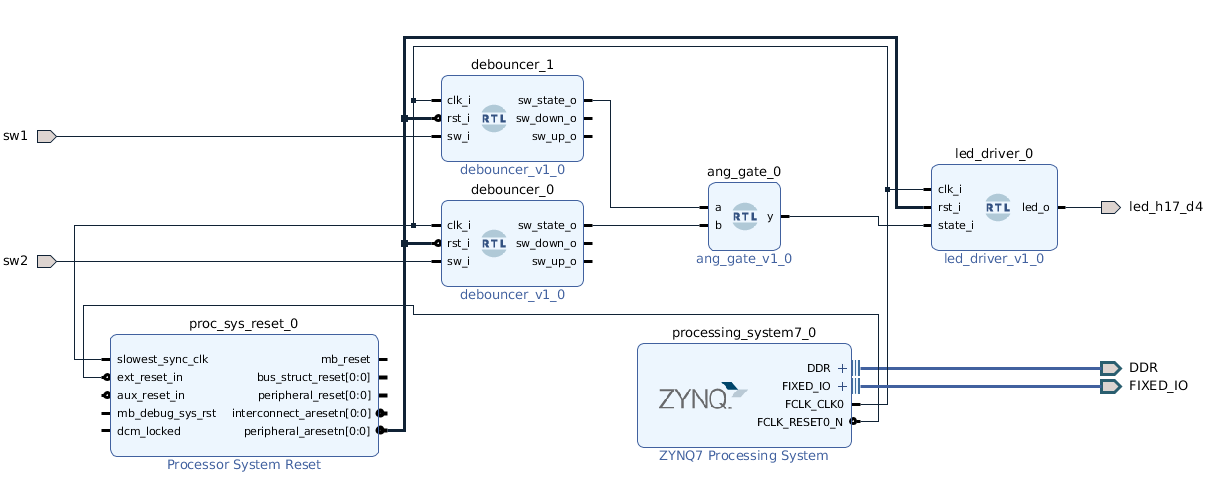

Но это слишком тривиально, обсудим более интересный вопрос: вот все эти люди, которые пишут код на языке описания аппаратуры Verilog, который потом превращается в дорожки и транзисторы из silicon на фабрике - они программисты? Аппарентли, нет.