Написание простого процессора и окружения для него

Здравствуйте! В этой статье я расскажу какие шаги нужно пройти для создания простого процессора и окружения для него.

Программируемые логические интегральные схемы

Здравствуйте! В этой статье я расскажу какие шаги нужно пройти для создания простого процессора и окружения для него.

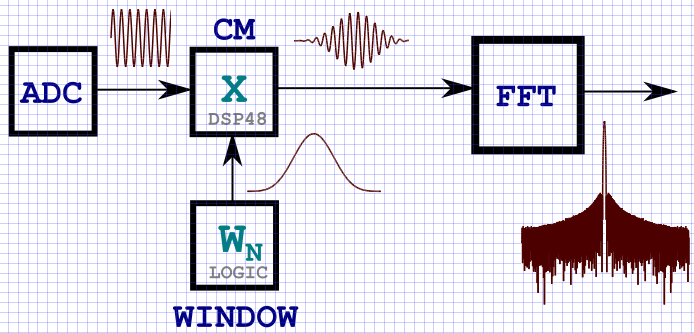

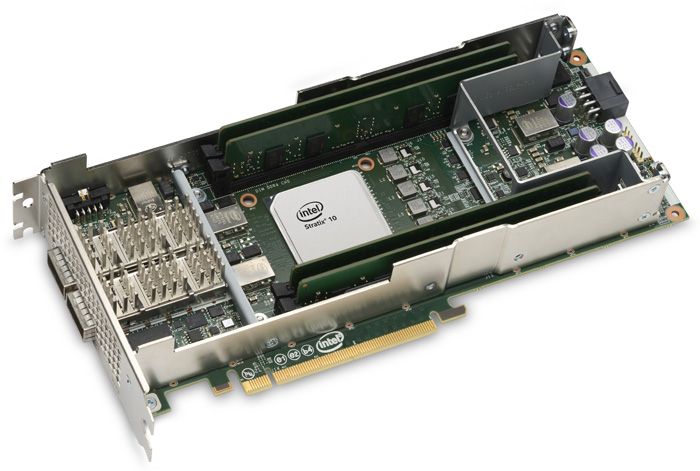

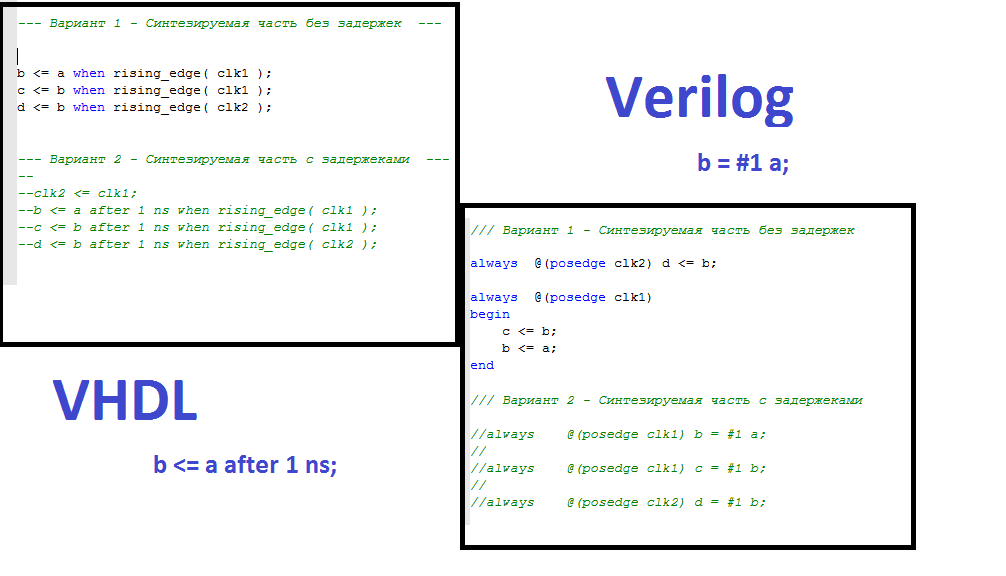

Возникал ли у вас когда-нибудь вопрос "как работает процессор?". Да-да, именно тот, который находится в вашем в ПК/ноутбуке/смартфоне. В этой статье я хочу привести пример самостоятельно придуманного процессора с дизайном на языке Verilog. Verilog — это не совсем тот язык программирования, на который он похож. Это — Hardware Description Language. Написанный код не выполняется чем-либо (если вы не запускаете его в симуляторе, конечно), а превращается в дизайн физической схемы, либо в вид, воспринимаемый FPGA (Field Programmable Gate Array).

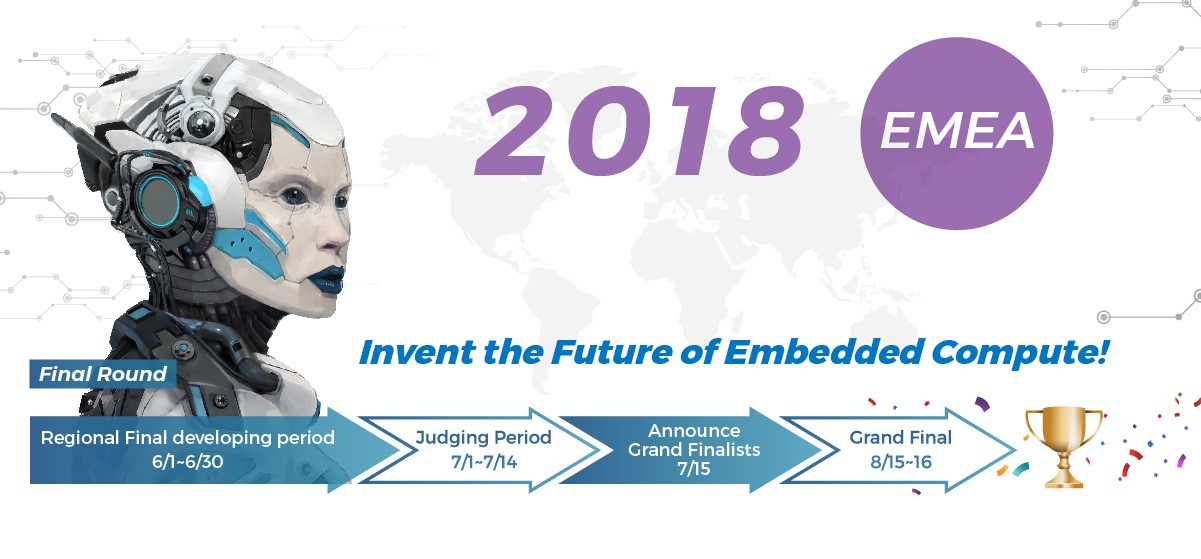

Со 2 по 5 октября в Новосибирске прошла школа по основам цифровой схемотехники, архитектуры и использования Verilog. Формальное название мероприятия: школа для магистрантов и аспирантов, проходившая в Новосибирском государственном техническом университет в рамках XIV Международной научно-технической конференции «Актуальные проблемы электронного приборостроения» АПЭП-2018, проводимой под эгидой IEEE.

Данное мероприятие было в первую очередь ориентировано на тех, кто:

Анонс: аналогичная школа запланирована с 6 по 9 ноября на базе Института космических и информационных технологий Сибирского федерального университета (ИКИТ СФУ). Вести школу будут Алина Лесковская — аспирант, инженер-конструктор АО ИСС им.М.Ф.Решетнева, а также ее коллеги: Дмитрий Власов и Борис Дудкин. Контакт для регистрации: leskovskayaav@yandex.ru

Если ваша должность звучит как минимум «Junior FPGA Developer», то с высокой вероятностью вы не узнаете в этом посте ничего для себя нового. Для всех остальных – добро пожаловать под кат.

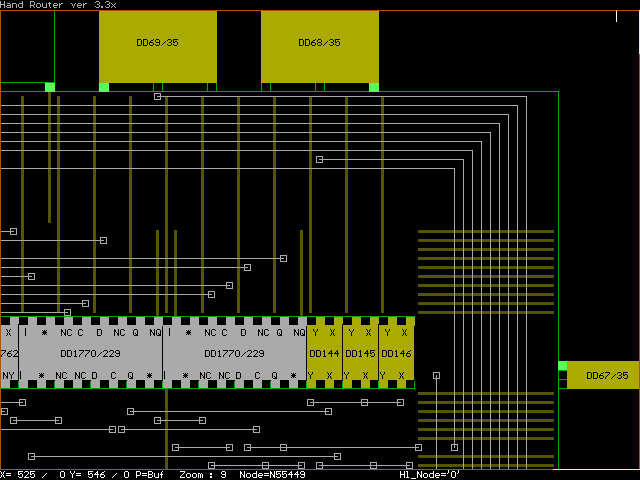

Принято решение для подключения к ПК использовать FTDI в ее двухканальной ипостаси — FT2232H. Один канал будет использован для конфигурации ПЛИС, другой может быть использован для высокоскоростного обмена в режиме FIFO.

С развитием микроэлектроники, rtl дизайны становились все больше и больше. Реюзабилити кода на verilog доставляет массу неудобств, даже с использованием generate, макросов и фишек system verilog. Chisel же, дает возможность применить всю мощь объектного и функционального программирования к разработке rtl, что является достаточно долгожданным шагом, который может наполнить свежим воздухом легкие разработчиков ASIC и FPGA.

В этой статье будет дан краткий обзор основного функционала и рассмотрены некоторые юзкейсы использования, также поговорим о недостатках этого языка. В дальнейшем, если тема будет интересна, продолжим статью в более детальных туториалах.

Всем нам известна проблема курицы и яйца: работодатели не хотят брать на работу выпускников без опыта работы, но где же в таком случае выпускникам получить опыт работы? В микроэлектронике эта проблема стоит особо остро ввиду требуемого огромного количества специфического опыта. Наши ВУЗы с советских времен знамениты широчайшей теоретической подготовкой, которая должна помочь выпускнику в любой сложной ситуации в жизни. Однако, современная индустрия требует практического опыта. Добавим сюда еще отсутствие мотивации, приводящее к тому, что по специальности работает процентов 15% выпускников, и получим жесточайший кадровый голод в отрасли, которая очень требовательна к качеству кадров. А ведь если бы каждый студент мог "поморгать лампочкой" со своего собственного кристалла ситуация могла бы развиваться совсем иначе.

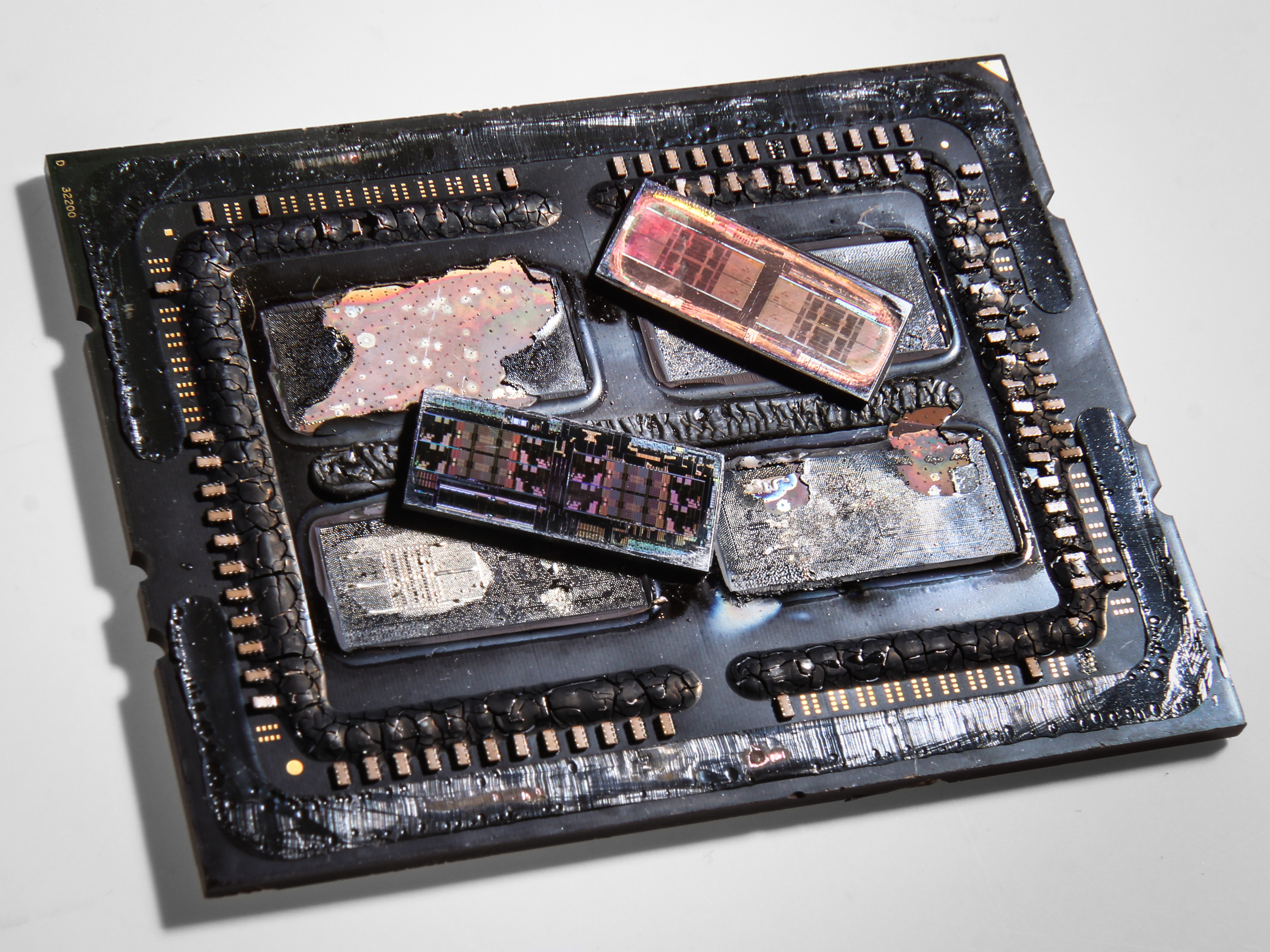

Рисунок 1. КДПВ

Что же мешает таким грандам подготовки кадров отечественной микроэлектроники, как, например, МИФИ и МИЭТ, поступать аналогично своим зарубежным коллегам (например, MIT или UZH), а именно — давать возможность студентами-дипломникам выпускать свои собственные кристаллы? Можно, конечно, предположить, что выпуск собственного кристалла занятие крайне долгое, сложное и дорогое, а потому для института — дорого, а для студента — непосильно. Однако, это не так. Давайте же взглянем на одну из доступных технологий на отечественном рынке микроэлектроники, знакомство с которой позволит студенту стать значительно более привлекательным в плане будущего трудоустройства, а предложение которой для студента — позволит университету значительно поднять свой рейтинг в глазах абитуриентов и работодателей.