Отладочная плата ПЛИС — Франкенштейн. Звуки и музыка

Сегодня у нас самая предновогодняя серия про ПЛИС и отладочную плату Френки. Предыдущие серии 1, 2.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

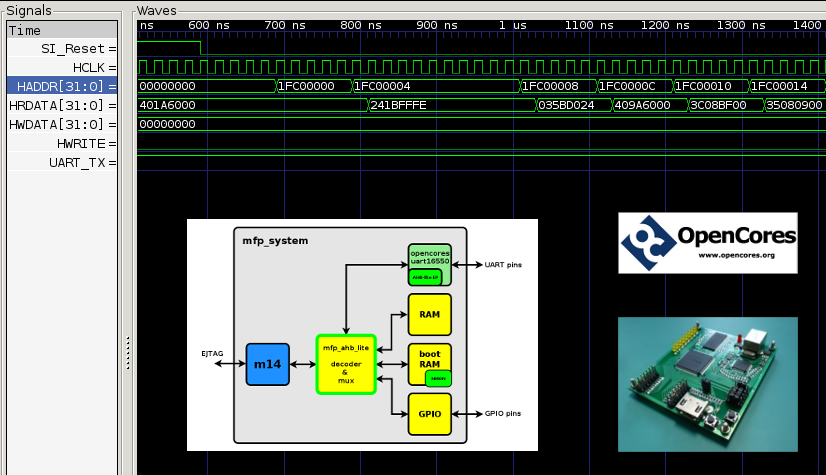

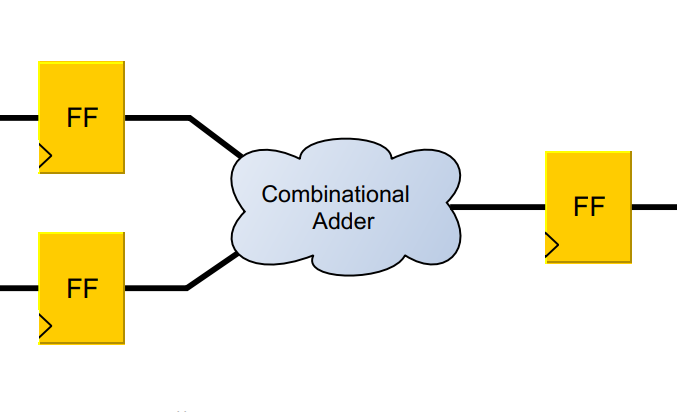

Для этого подключим к ПЛИС обычный динамик. К Френки подключен генератор на 25.175 МГц. Если поделить эту частоту до диапазона слышимых частот и подать на вывод ПЛИС, то мы можем услышать звук. Меня частоту мы можем получить разные звуки.

Тестировать качество звучания будет самый лучший слухач в доме — Маша. Диапазон частот в 60 КГц — это вам не шутки! )))

Настала пора сравнить две ПЛИС из одной весовой категории:

Настала пора сравнить две ПЛИС из одной весовой категории: