Верификация FPGA. Что это?

Если не все, то многие здесь слышали про ПЛИС. Возможно некоторые даже плотно с ними работали, но, думаю, с верификацией проектов на ПЛИС сталкивалось намного меньше людей. Сегодня я расскажу о процессе верификации.

Программируемые логические интегральные схемы

Рассказываем о проекте с корпорацией «Комета» — полный цикл от графической модели до работающего «железа» на FPGA

Привет с вами снова Александр и FPGA-тян. На самом деле хочется признаться, что эта статья задумывалась как первая, поэтому и имеет в названии слово " Знакомство". Но она никак не могла пройти модерацию (по неизвестной мне причине), однако я всё же решил выложить и этот пробный материал. Поэтому давайте мысленно представим, что она всё же вышла первой и будем отталкиваться от этого при прочтении.

Речь пойдёт всё так‑же о асинхронной логике. Похоже, что тут никто и никого не ждал... к такому выводу можно прийти, если посмотреть на сравнения, в сети и материалах, по части синхронной и асинхронной логики, и на фактические цифры, ну и на традиционную забагованность (в частности Gowin EDA) в таких нужных местах как массивы, впрочем эта забагованность вполне победима посредством небольшого «шаманства», об этом будет тоже. Приходится делать «двухшаговые » публикации, потому что если свалить всё в прошлую — то это вряд ли станет всё читабельным, а одного шага явно мало для полноценной публикации, особенно на фоне борьбы с чужими багами. Если не лень читать новые «приключения» в асинхронном, и не только, мире — то пожалуйста.

Для стабильной работы последовательным схемам нужен надежный тактовый сигнал для обеспечения стабильной синхронизации по времени. Для обеспечения стабильного источника частоты схемы генератора тактовых сигналов используют кварцевый резонатор. Драйверные схемы усиливают сигнал от кристалла (или генератора) в цифровой сигнал, который распространяется на остальные, например, запоминающие устройства в цифровой системе.

Большинству цифровых схем требуется несколько (или даже десятки) различных тактовых сигналов для управления различными подсистемами. Например, система на основе ППВМ может использовать тактовую частоту 48 кГц для создания аудиопотока, тактовую частоту 1 кГц для запуска таймера, тактовую частоту 10 МГц для запуска небольшого процессора и тактовую частоту 12 кГц для запуска контроллера двигателя. Было бы слишком дорого использовать отдельные внешние схемы осциллятора для создания такого количества различных тактовых сигналов, поэтому системы обычно производят необходимые им тактовые сигналы всего из одного или двух основных тактовых входов.

Когда возникла необходимость защитить устройство от нежелательного использования, оказалось, что на эту тему мало информации. В конце концов, процесс перехода по множеству ссылок, которые выдал поисковик, вывел на XAPP1239, UG470 и XAPP1084. Перед прочтением этой статьи лучше с ними ознакомится, так будет понятнее о чём идёт речь. Ниже будут пошагово описаны процессы создания зашифрованного bitstream и конфигурации ПЛИС на отладочной плате ARTY A7 и XC7K325T KINTEX-7 на кастомной плате для программирования этим зашифрованным bitstream.

Наверное каждый "ПЛИСовод" использовал высокоскоростные приёмопередатчики хотя бы раз в своей практике. В семействе ПЛИС Intel/Altera серии IV IP ядро с этим функционалом называется ALTGX.

Основная задача этого IP ядра - преобразование параллельной шины на низкой частоте в последовательную шину на высокой.

Динамическая реконфигурация позволяет менять различные параметры приёмопередатчиков "на лету", то есть не меняя прошивку ПЛИС.

Основными из них являются:

скоростные характеристики, то есть на какой скорости будут принимать и передавать данные

включать/выключать встроенные кодеки (в ПЛИС серии IV - кодек 8b/10b)

менять аналоговые параметры, такие как TX VOD, TX Preemphasis, RX Offset Cancelation, RX Adaptive Equalizer

Ни для кого не секрет, что компиляция и тестирование проектов ПЛИС занимает достаточно большую часть времени всего процесса разработки. Поэтому часто разработчики используют различные среды симуляции для тестирования своих модулей. Но многие ли использовали среду симуляции для тестирования разработанных модулей в связке с используемыми IP ядрами от разработчика ПЛИС. В этой статье мы решили поделиться своим опытом, начиная с создания IP ядра ALTGX для ПЛИС Intel Cyclone IV до симуляции созданного проекта для тестирования модулей динамической реконфигурации с связке с ALTGX.

Чем хорош FPGA-хаб на Хабре это еще и тем что тема протокола valid/ready время от времени тут всплывает. И это действительно важно так как valid/ready является одним из основных протоколов организации управления потоком (flow-control). Понимание valid/ready для микроархитектора так же необходимо как необходимо понимание закона Ома электрику.

На прошлом занятии мы отработали концепцию очереди FIFO на микроархитектурном тренажере - hdlgadgets. В этот раз мы возьмем два FIFO буфера (которые образуют конвейер с valid/ready рукопожатиями) и будем менять flow-control логику конвейера.

Мы покажем что valid/ready это не только механизм передачи данных от одной очереди к другой, но еще и метод для организации разного рода логического функционала между очередями.

Если до этого момента вы не сталкивались с протоколом valid/ready, то будете приятно удивлены как легким движением руки (а если точнее, написанием пары строк на верилоге) мы можем реализовывать разного рода функционал взяв за основу конвейер из двух FIFO.

В эти выходные в Silicon Valley прошла парти на 400 человек под названием GPT-Party, из которых все 400 человек говорили по-русски (когда ведущий спросил кто не говорит, никто не поднял руку).

На парти выступали основатели ИИ компаний, русские венчурные капиталисты (Давыдов, Шойфот, Орешкин), украинские венчурные капиталисты (Сорока) , а также креаторы контента (Алекс Кролл). Креаторы говорили, что из-за ChatGPT всех инженеров выгонят с работы и останутся только бармены и креаторы контента.

Под конец самый богатый человек на парти, основатель ABBYY Давид Ян - посягнул на проблему сознания. В качестве показателя прогресса ИИ в этой области Давид приводил решение компьютером задачек, в которых нужно ставить себя на место других людей. Типа (это не задачка Яна, а мой аналог приведенных им задачек):

Схема на картинке содержит в себе повторяющиеся части. Если их количество постоянно меняется в ходе разработки, то было бы неплохо, если бы всё это собиралось автоматически, правда? Как это реализовать, читайте в данной статье.

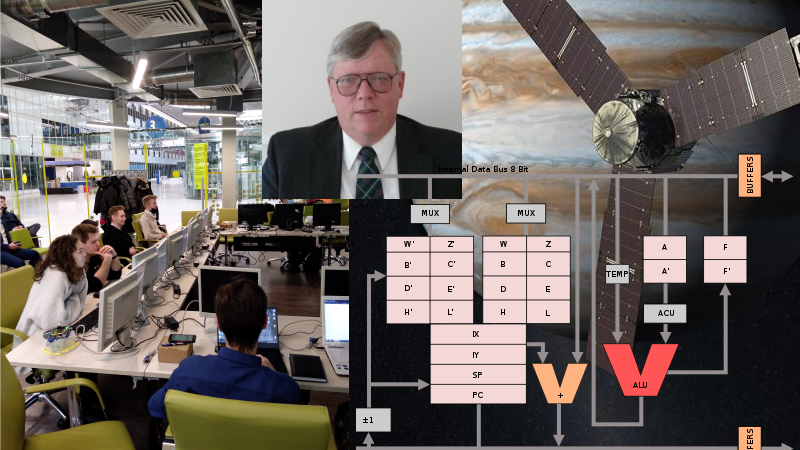

Что общего между популярным у хоббистов компьютером Синклер ZX Spectrum и космической станцией Juno, которая сейчас вращается вокруг Юпитера? И на одном, и на другом стоит процессор с архитектурой Zilog. На Синклере просто Z80, а на Juno - радиационно стойкий Y180-S. Y180-S спроектировал Монте Далримпл (Monte J. Dalrymple), выпускник Беркли, который проработал 16 лет в Zilog, после чего сделал собственный бизнес, компанию под названием Systemide.

Мы связались с Монте и он согласился выступить перед российскими слушателями, рассказать о всяких занятных ситуациях при проектировании процессоров.

This article is a part of a course work for first year bachelor students of Innopolis University. All work is done in a team. The purpose of this article is to show an understanding of the topic, or to help to understand it using simulation.

Principle of work but from the user side should look like:

When working with Verilog, it should be understood that each individual block of the program is represented as a module. As you know, the cache is not an independent part of fast memory, and for its proper operation it needs to take data from another memory block — RAM. Therefore, in order to simulate the work of the cache at the FPGA, we have to simulate whole RAM module which includes cache as well, but the main point is cache simulation.

The implementation consists of such modules:

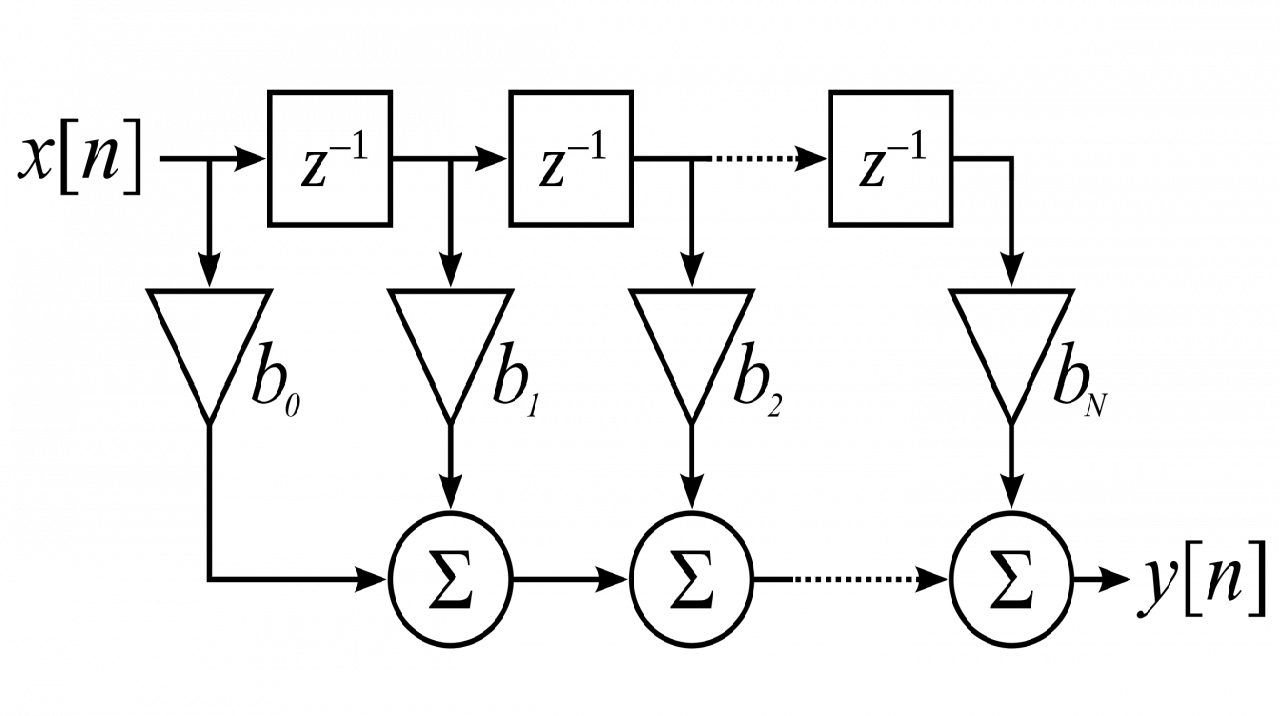

Пару месяцев назад я проходил собеседование, где требовался некоторый опыт в DSP, и на вопрос, является ли CIC фильтр БИХ или КИХ, я ответил, что КИХ, на что мне ответили, что раз там в структуре рекурсия, то он именно БИХ. Я несколько удивился, но понял ход рассуждений собеседующего и в принципе согласился с таким подходом. Мой давний опыт с CIC фильтрами касался программирования DDC GrayChip и Analog Devices и моделирования трактов SDR на С и в Octave, при этом в качестве имплементации CIC для моделей я использовал всем хорошо известную функцию скользящего прямоугольного окна.

Читая Хабр и отмечая постоянный рост сообщений об успехах AI - и микросхемы он разрабатывает, и программы пишет, и даже угрожает Stack Overflow, решил, что пора познакомиться c этой технологией в каким-нибудь проявлении.

Установив в Chrome Merlin, спросил его как сделать эхолот для рыбалки, какие датчики можно для него купить, какой многоканальный быстродействующий АЦП можно купить на Али для RaspberyPI и как посчитать ширину диаграммы направленности антенной решётки из 8 элементов. В целом я не узнал ничего нового, кроме предупреждения, что с АЦП могут быть проблемы подключения по SPI по быстродействию, зато этот бот одобрил применение режима DMA для ввода данных. Ну и программу для расчёта ДН на С мне показали достаточно правдоподобную. Ссылок на товары на Али я не получил, но получил набор фраз для поиска. В общем, несмотря на периодические упоминания сложности обсуждаемых вопросов и потенциальной нехватки квалификации у вопрошающего, общение было если и не очень плодотворным, но вполне профессиональным и дружелюбным.

Этой статьей мы продолжает серию статей, цель которых поделиться опытом создания проектов в среде симуляции для тестирования динамической реконфигурации высокоскоростных интерфейсов (приёмопередатчиков) различных поколений ПЛИС фирмы Intel/Altera. В предыдущей статье мы описали IV поколение, теперь очередь "обуздать" V поколение.

Добрый день! В этой статье я расскажу, как наши заказчики используют ПЛИС в полунатурных стендах и стендовых испытаниях.

В центре инженерных технологий и моделирования «Экспонента» уже много лет мы занимаемся продвижением модельно-ориентированного проектирования в России. Поэтому наш опыт сконцентрирован вокруг инструментов модельно-ориентированного проектирования — то есть различных сред моделирования и симуляции — и применения их в инженерных разработках.

Эта статья написана совместно с нашими хорошими партнерами — компанией «РИТМ». Компания занимается разработкой полунатурных стендов и комплексов полунатурного моделирования «РИТМ» (КПМ «РИТМ»), которые используются нашими заказчиками.

КПМ «РИТМ» представляет собой программно-аппаратное решение для тестирования в реальном времени. Спектр его применений широкий: от быстрого прототипирования алгоритмов управления до полунатурного моделирования объекта управления (Hardware-in-the-Loop или HIL тестирование). РИТМ применяется нашими заказчиками в различных инженерных областях: от авиастроения и ВПК до автомобилестроения и электроэнергетики.

КПМ «РИТМ» поставляется настроенным «под ключ» под задачи проекта или стенда, и оснащен всеми необходимыми модулями ввода-вывода (аналоговыми, цифровыми, специализированными интерфейсами и протоколами). Пользователи могут быстро и бесшовно запускать свои модели в реальном времени (содержащие алгоритмы или модели объекта управления) и подключать их к реальным устройствам (например, блоку управления или исполнительным механизмам) через модули ввода-вывода.

Наши заказчики успешно используют этот подход уже многие годы, но в некоторых узких задачах сталкиваются со следующими проблемами:

• Необходимо существенно сократить шаг расчета алгоритма;

• Не хватает вычислительных ресурсов для решения задачи в реальном времени на процессоре;

• Требуется подключить к алгоритму высокоскоростные цифровые, аналоговые или другие интерфейсы;

• Требуется поддержать заказные интерфейсы или протоколы обмена.

Если вы тоже сталкиваетесь с такими проблемами, то добро пожаловать под кат — даже если вы раньше никогда не слышали о модельно-ориентированном проектировании или ПЛИС.

AMD проводит суперкомпьютерный день в Назарбаевском Университете в Астане, в Казахстане. 29 сентября. Можно подсоединиться по Зуму. Зарегистрироваться можно до 27 сентября по ссылке.

Вообще приезжающие в Астану замечали, что в городе есть амальгамация духа советских городов с духом американского Лас-Вегаса, в частности в элементах архитектуры.

Теперь можно добавить и другое сходство: в Лас-Вегасе помимо казино есть университет, в котором еще в допотопные времена стояли суперкомпьютеры и велись конкурсы на качество распознавания образов. Также там сейчас преподает Сара Харрис, соавтор известного учебника. Кроме этого в Лас-Вегасе иногда проводится конференция DAC по автоматизации проектирования электроники. Почему бы не превратить Астану в евразийский центр такого рода?

Данная статья пишется с несколькими целями: изложить возможные методы повышения быстродействия стековых процессоров, собрать попутно небольшую библиографию, и закрепить на данный момент что мне известно в этой области. Статья или точнее пост, выйдет крайне сухим и лапидарным.

Часть положений не имеет ссылок на литературу., в силу не полной разработанности темы. И еще потому, что это довольно общеизвестные факты, которые легко найти. А так же потому, что упор сделан на то что неизвестно широким массам общественности.

Широко распространено мнение, что стековые процессоры являются тупиковой ветвью развития, я считаю что это не так. Многие люди полагают, что в стековом процессоре нельзя реализовать те же решения, которые в регистровых процессорах являются основными причинами повышения производительности. Поэтому на сегодняшний момент, стековые, форт -процессоры, в основном используются во встраиваемых системах. Это обусловлено не только их принципиальной ограниченностью, но и основным полем деятельности их разработчиков. Я полагаю, что стековые процессоры могут быть не только процессорами реального времени, но и процессорами общего назначения, пригодными для десктопного и серверного использования.

Статья очень обзорная, даже поверхностная и в ней я не буду углубляться в детали реализации, так как основной целью является сбор и публикация в одном месте тех сведений которые остаются малоизвестными широкой общественности, что бы можно было проводить работу вокруг уже стабильного текста. Малоизвестность их, связана и с недоступностью патентных баз, с тем что некоторые исследования либо недавние, либо только относительно недавно попали в открытый доступ и пылились в архивах.

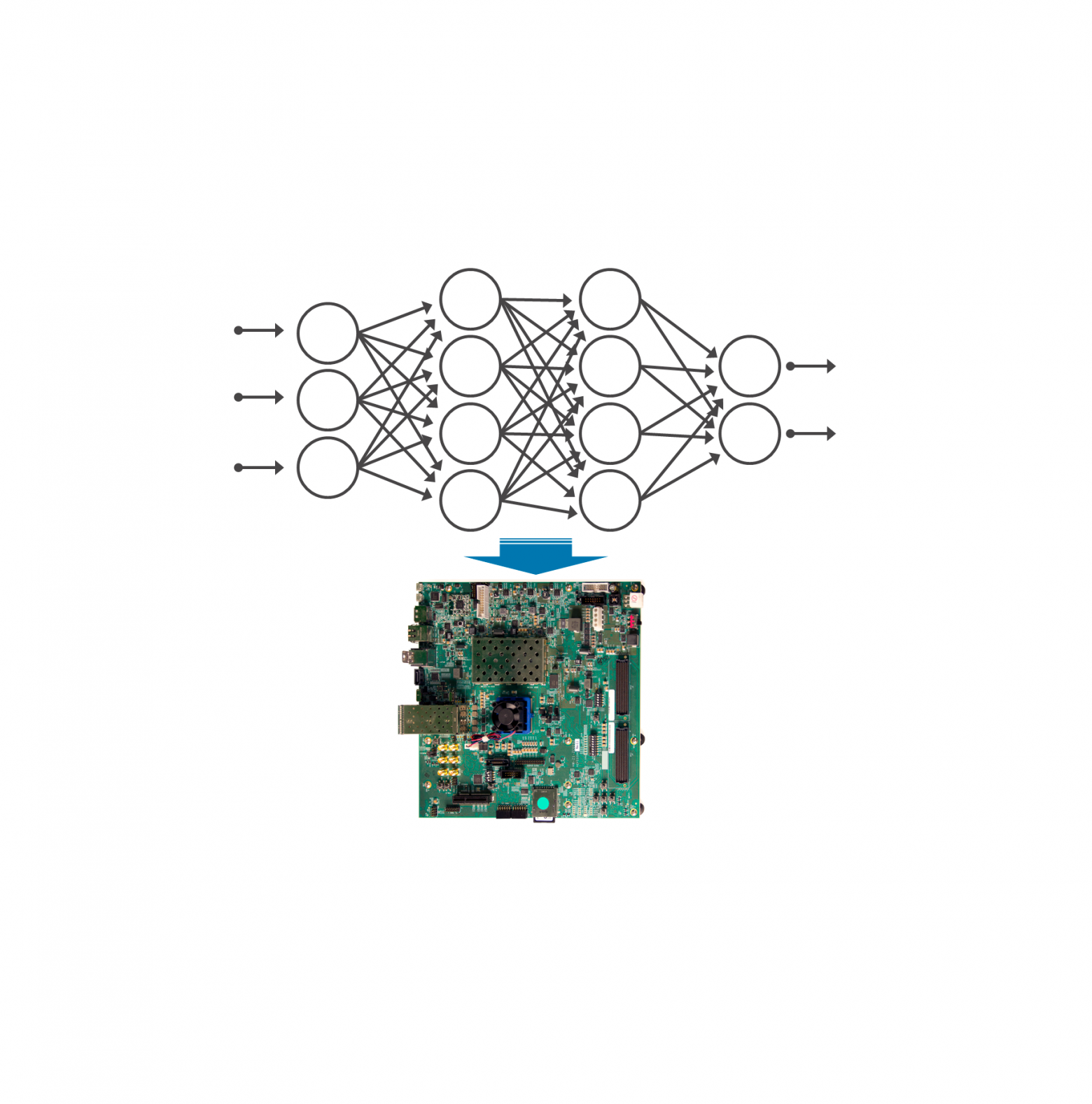

Глубокие нейронные сети (DNN) способны решать сложные задачи в областях, связанных со встроенными системами, таких как обработка изображений и естественного языка. Чтобы эффективно реализовать DNN на конкретной платформе ПЛИС для заданного критерия стоимости, например, энергоэффективности, необходимо учитывать огромное количество параметров проектирования, начиная с топологии и заканчивая конечной аппаратной реализацией. Необходимо учитывать и эффективно исследовать взаимозависимости между различными уровнями проектирования, что делает поиск оптимизированных решений вручную едва ли возможным.

Автоматический, целостный подход к проектированию может значительно улучшить качество реализации DNN на ПЛИС. С этой целью мы представляем метод исследования межслойного пространства проектирования.