Getting Better at Reading Academic Papers: a Brief Guide for Beginners (Part 2)

It runs south and circles north, circling, circling to run with its wind

It runs south and circles north, circling, circling to run with its wind

Nowadays, when VR helmets have become part of our reality and Tesla cars fly in space, you can use all the power of browser engines to create truly interactive, cross-platform and stylish presentations, rather than make a set of PPTX pages or, even worse, a PDF document in "illustrative material for explanatory and calculation report" style.

Since 2015, I have been trying to find the optimal presentation format for myself (apart from graduation projects). And now I think I have almost succeeded. It all started with PowerPoint, and ended with web frameworks based on JavaScript.

There are several JavaScript engines which can be used to create cool presentations: Marp, Reveal, landslide, hacker-slides, slidify and others. In some engines, you can use Markdown, some are embedded in an IDE, and some have their own editors. I have tried the first two engines.

As a demonstration, slide examples and video are available.

Saluting my LED lamp fans!

Saluting my LED lamp fans!At Microsoft, we’re investing in helping our customers as they move to the cloud. We see an opportunity to help support companies in this changing environment by bringing our security, privacy, compliance and intellectual property assets and expertise to bear in order to help them be more successful. We’re excited to now take an additional step that expands innovation protections.

Today, we are pleased to announce the expansion of the Microsoft Azure IP Advantage program to include new benefits for Azure IoT innovators and startups. We first announced Azure IP Advantage in February 2017, to provide comprehensive protection against intellectual property (IP) risks for our cloud customers. A trend we saw at the time – and one that continues today – is a growing risk to cloud innovation from patent lawsuits. Last year, we joined the Open Invention Network (OIN) and the License on Transfer (LOT) Network to help address patent assertion risk for our customers and partners.

We at Verilog Meetup constructed an exam/interview problem that has an interesting property: if a student tries to figure out a solution by thinking by himself, he usually succeeds; however if he dumps the problem on ChatGPT, the solution fails (does not pass the automated test), and the student goes into a death spiral of futility, kicking ChatGPT to get the solution right.

There is nothing weird about the problem, we do this in the industry all the time:

Hi Everyone.

Recently I got Asus E200H laptop, which I would like to use as a portable computer to work with a high-precision equipment.

Within the scope of the article we will perform the experiment about the upgrade of the default 32 GB eMMC capacitor to 256 GB and will test it.

Have a nice reading!

Last week I was doing a seminar on SystemVerilog, ASIC and FPGA at ADA University in Baku, Azerbaijan. I will replicate the last two sessions of this seminar, on RISC-V CPU simulation and synthesis, at the Verilog Meetups on March 3 and March 10 at Hacker Dojo, Mountain View, California. For this reason I am combining the information about Azerbaijan and California seminars in a single post.

First, let's talk about ADA University.

Gleb Kulev, Candidate of Technical Sciences

The rapid exploration of outer space has faced a problem related to the insufficient efficiency of modern rocket engines. As a solution to this problem, the concept of a jet engine based on new operating principles is proposed, using a combination of known physical laws and having advantages over known types of jet engines.The article presents the results of testing three modifications of jet engines based on new operating principles and their analysis. The article discusses the physical principles of operation of a jet engine based on new principles, its advantages and problems arising during its creation.

The team developing a set of portable SystemVerilog examples decided to organize the first event in Silicon Valley on Sunday, January 14 from 2PM till 5PM at Hacker Dojo in Mountain View, CA. If the first event is successful we are going to make it recurrent. You can register for the event on Meetup or LinkedIn.

The current directions of the group:

Ссылка на русскую версию / link to Russian version

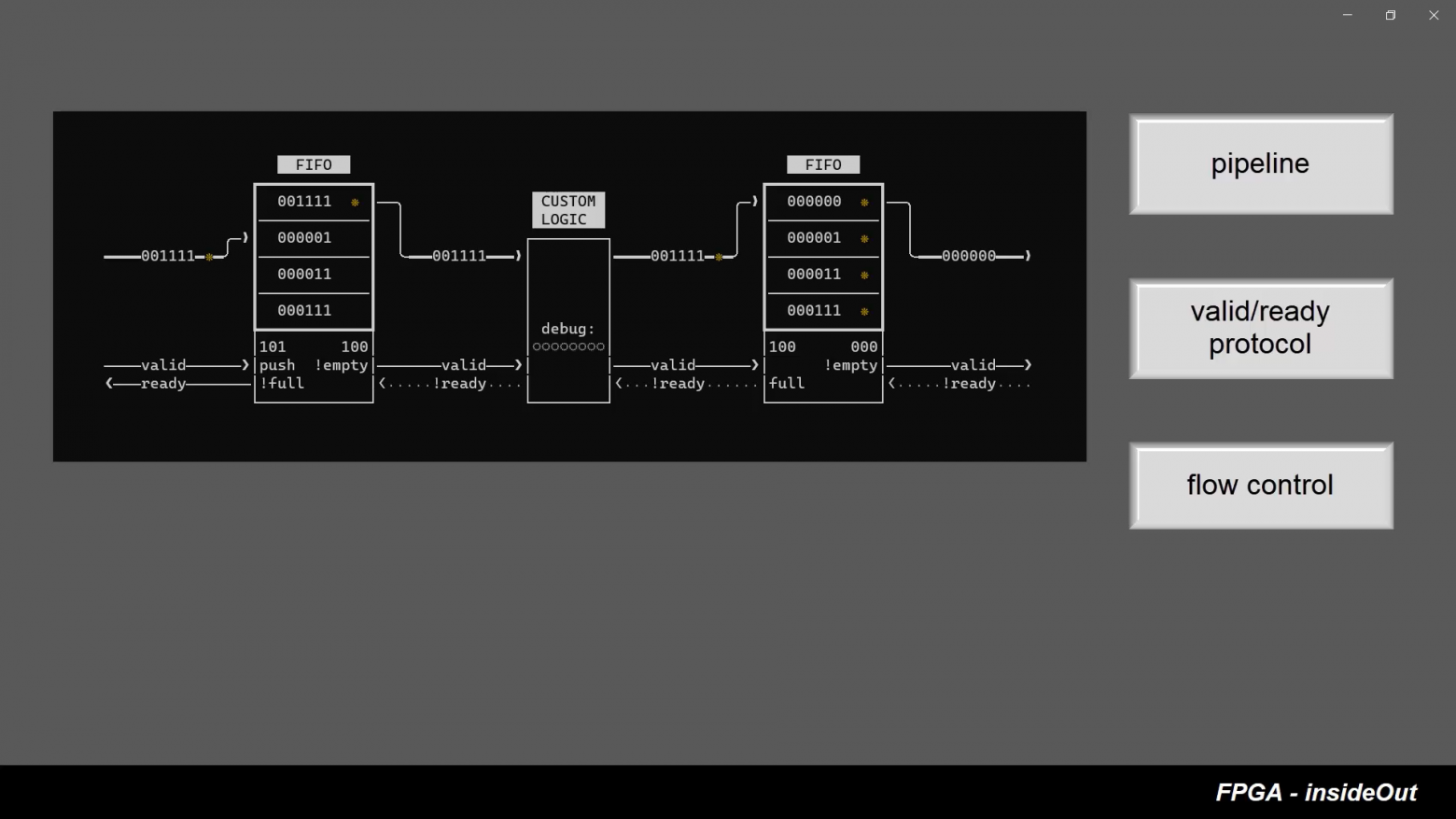

Understanding valid/ready protocol is extremely important for every microarchitect.

Valid/ready is one of the main protocols used to organise flow-control inside a logic block as well as on inter-block (SoC) level.

In the last lesson, we explored FIFO buffer using hdlgadgets - human-in-the-loop HDL training tool.

This time we will take two FIFO buffers (which form a pipeline with valid/ready handshakes) and will experiment with it by changing flow-control logic of the pipeline.

We will show that valid/ready is not only a mechanism for transferring data from one FIFO queue to another, but also a method for organizing various kinds of logical functionality between queues.

If you have not worked with valid/ready protocol before, you will be surprised how easy it is to achieve desired functionality of the design by simply writing couple of lines of Verilog code in the handshaking logic block between two FIFOs.

Great for seamless patterns, abstract drawings, and watercolor-styled images. How to use it and train a neural network on your own pictures?

Download the model here: https://huggingface.co/netsvetaev/netsvetaev-free