Господа! Сегодня мы пройдемся с сибирской девушкой Ириной по Музею истории компьютеров в Маунтин-Вью, Калифорния. Причем пройдемся не как туристы, а для принесения пользы России. Я уже писал в

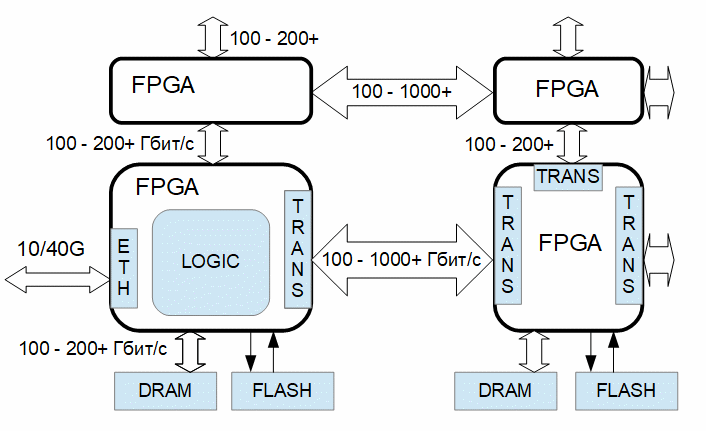

предыдущем посте, что один из эффективных способов для студента изучить проектирование процессоров — это взять какой-нибудь древний, но поучительный процессор, найди документацию по его архитектуре (и какую-нибудь информацию по его микроархитектуре), и спроектировать аналог этого процессора на языке описания аппаратуры SystemVerilog (или VHDL, если он вам больше нравится), после чего реализовать процессор на плате ПЛИС / FPGA (какой именно, не важно — Altera / Intel FPGA, Xilinx или Lattice). В качестве учебника для такого упражнения вы можете начать с

Харрис & Харрис, после чего продолжить с

книгами для более продвинутой стадии обучения, например Шень-Липасти.

Каким образом все это принесет пользу России? Под такие проекты мы собираемся раздавать FPGA платы на

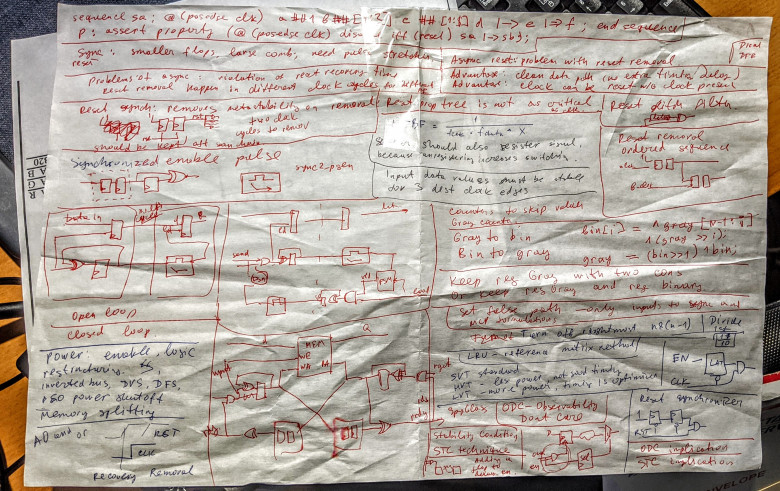

конференции которая пройдет 18-22 сентября в Томске. Туда приедут представители МГУ, МФТИ, МИЭТ, МЦСТ, Imagination Technologies, National Instruments итд. Они будет обсуждать, как обновить программу университетов, чтобы сегодняшние студенты через несколько лет проектировали росийские чипы на уровне передовых западных компаний. Там также будет школа-семинар, на которой будут обсуждать, как делать учебные процессоры — начиная от простейшего

schoolMIPS от

Станислава Жельнио sparf.

Вот первая фотография из музея в Маунтин-Вью — на ней помимо Ирины и ракеты в центре виден небольшой ящичек. Это

бортовой компьютер космической станции «МИР» , который проектировали инженеры советского объединения «ЭЛАС», которое трансформировалось в современную

зеленоградскую компанию «ЭЛВИС»:

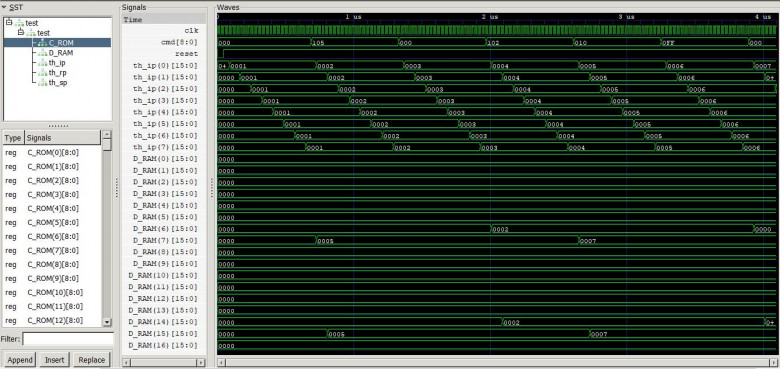

Итак, темы для учебных проектов — начиная из дремучих десятилетий середины XX века:

В

В