Видеокарта VGA для микроконтроллера

Иногда, при разработке устройств на микроконтроллерах, возникает потребность в выводе на дисплей большого количества информации или же в выводе информации на крупный дисплей для возможности ее считывания с большого расстояния. К сожалению, готовых решений этой проблемы нет, а те что есть – весьма дороги. Например, графические ЖК-дисплеи с возможностью подключения к микроконтроллеру обычно имеют диагональ не более нескольких дюймов и достаточно существенную цену (причем, даже монохромные, о цветных вообще можно не говорить).

В то же время есть огромный парк старых ЖК мониторов. Модели с диагональю 15-19 дюймов можно приобрести в рабочем состоянии за 200 – 500 руб. Особенно это касается моделей с немодным сейчас соотношением сторон 4:3. Эти модели достаточно надежные. Лампы CCFL, используемые для подсветки, конечно, теряют яркость за годы эксплуатации и их спектр свечения уходит в неприятный красноватый оттенок, но благодаря большому количеству таких мониторов всегда есть возможность выбрать более-менее живой экземпляр. Кроме того, лампы CCFL относительно несложно заменить обычной светодиодной лентой, подключив ее напрямую к источнику питания 12 В монитора. Однако при этом обычно необходимо заблокировать цепи обратной связи от микросхемы управления подсветкой к контроллеру самого монитора, иначе монитор будет думать что подсветка неисправна и просто выключится. Также придется пожертвовать функцией регулировки яркости. Однако, этой функцией мало кто пользуется. Обычно яркость монитора настраивается один раз в жизни, сразу после его покупки и потом никогда не меняется.

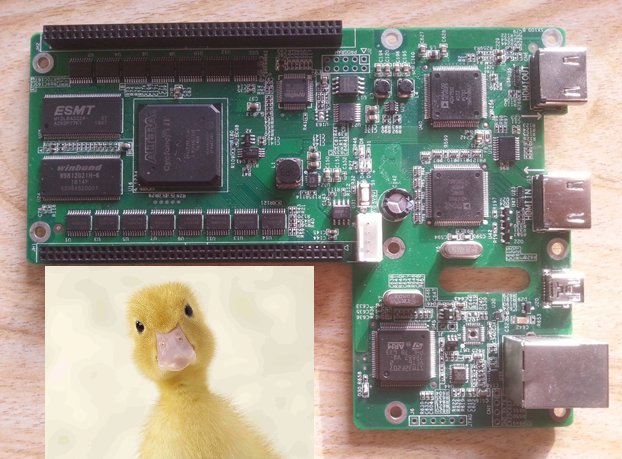

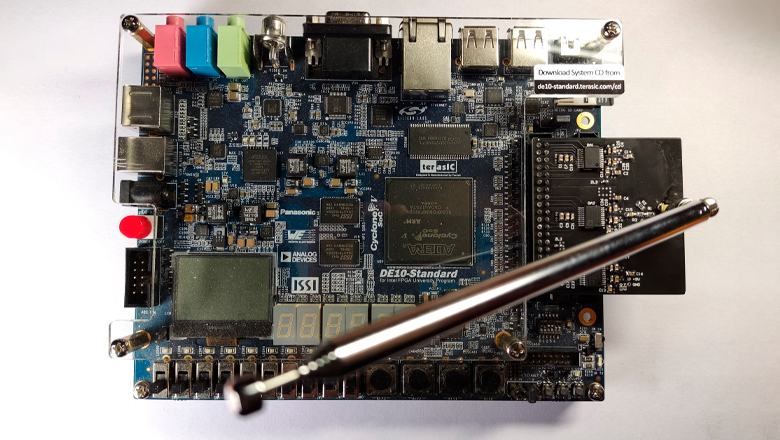

Предлагаемая иерархия инструментов (здесь и далее изображения из оригинальной статьи)

Предлагаемая иерархия инструментов (здесь и далее изображения из оригинальной статьи)