Как я убеждал блондинку Машу перейти с программирования RTOS в проектирование железа (а также Coq, Lisp и Haskell)

В викенд я зашел в кафе Red Rock и встретил там программистку встроенных систем Машу Горбунову. Вообще, у этого кафе в Маунин-Вью, Калифорния можно встретить кого угодно - например однажды на меня прямо из-за угла вылетел основатель Гугла Сергей Брин. Так вот Маша рассказала мне что программирует RTOS (семафоры, мейлбоксы, сигналы), чему выучилась в свое время в питерском институте ГУАП (аэрокосмического приборостроения).

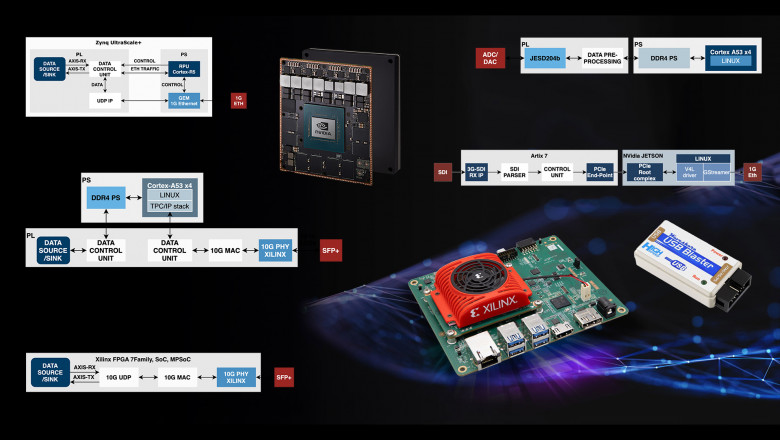

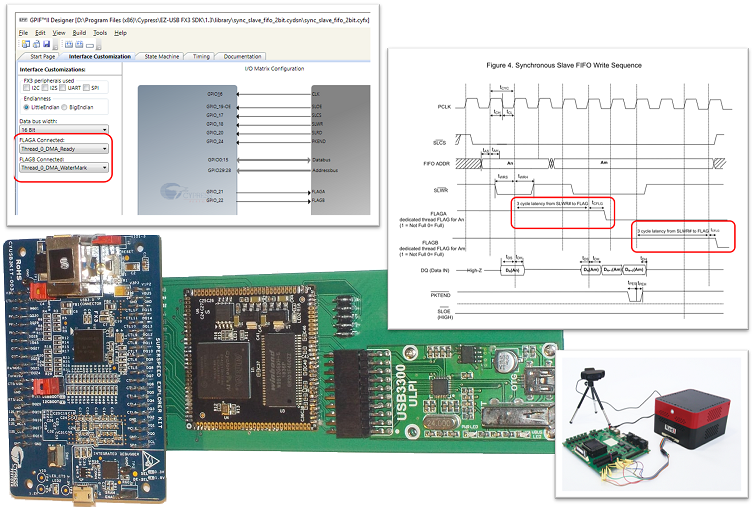

Я решил, что такая девушка не должна оставаться в другой отрасли и показал ей плату ПЛИС, внутри которого можно засинтезировать пару ядер ARM микроконтроллерного класса. На что Маша среагировала так (видео):

Всем привет! Одно из видений

Всем привет! Одно из видений