Когда я видел на Хабре упоминание о ПЛИС Lattice, у меня всегда возникал простой вопрос: «А зачем ещё одна ПЛИС?». Вроде всю жизнь хватало пары базовых. Но полгода назад случилось то, что сняло этот вопрос для меня. Пришёл Заказчик и сказал: «Мы делаем проект на ECP5». Против требований Заказчика не попрёшь!

А пока я осваивал работу с этим железом и пытался понять, как обосновать необходимость попробовать то же самое для остальных, мой знакомый, ныне живущий в Штатах, обрадовал новостью, что у его любимого поставщика подходит к концу запас десятых Циклонов и шестых Спартанов. В целом, через три года будет построен новый завод Intel, но что именно там будут производить, он не в курсе. И три года продержаться в любом случае, будет нужно. Короче, сейчас надо иметь возможность быстро мигрировать с одной ПЛИС на другую.

Итого, вчера делать ознакомительную статью про Lattice было рано, завтра – может быть поздно.

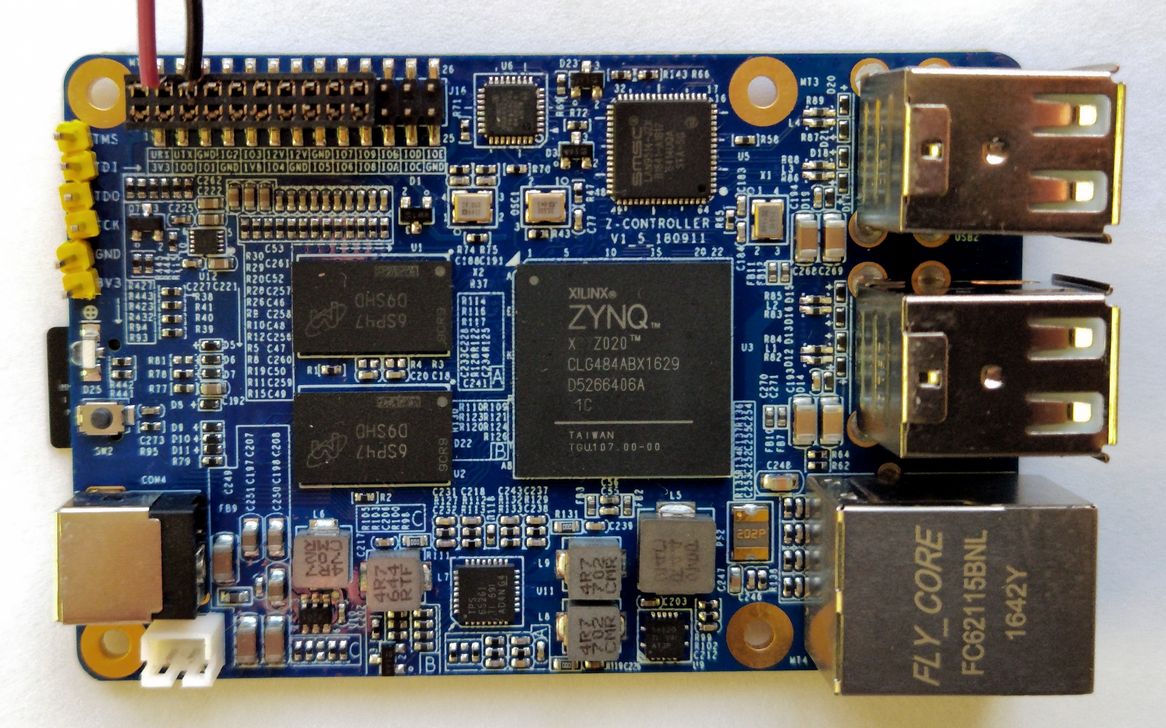

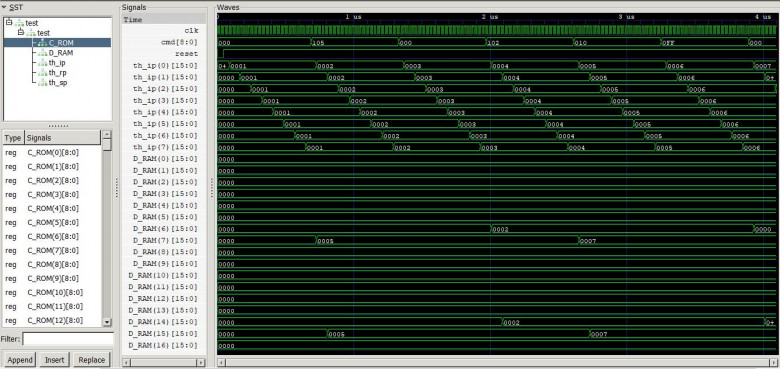

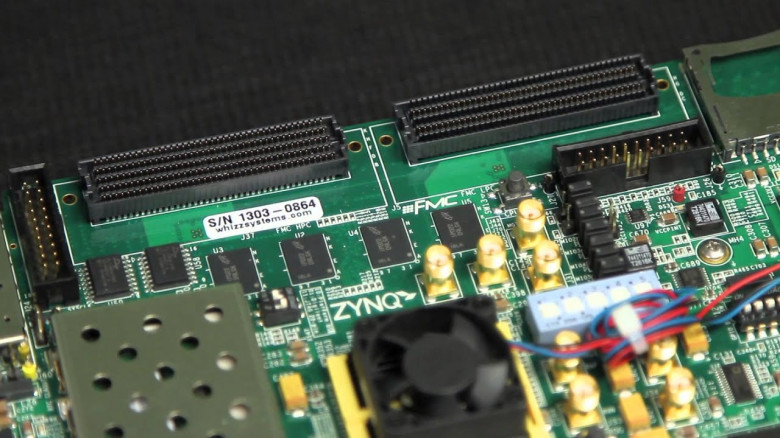

Сегодня я расскажу, где купить более-менее дешёвые платы для опытов, как быстро освоить Open Source среду разработки и какие готовые проекты осмотреть в первую очередь.