Преобразователи Time-To-Digital (TDC): что это такое и как они реализованы в FPGA

На рисунке — первый в мире спутник квантовой связи «Мо-Цзы», который запустили из Китая в 2016 году, в нем летает TDC, реализованная в FPGA.

Объяснить своей девушке (или парню), что такое ADC и DAC, и в каких домашних приборах они используются, может каждый человек, называющий себя инженером. А вот что такое TDC, и почему у нас дома их нет, зачастую можно узнать только после свадьбы.

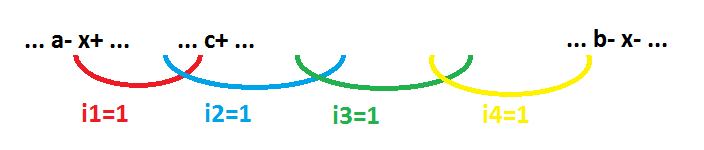

TDC — это time-to-digital converter. По-русски говоря: времяизмерительная система.

Основные потребители быстродействующих TDC — научные группы. Как правило, под определенный исследовательский проект требуется что-то очень специфическое. То каналов надо много, то разрешение очень высокое, то исполнение компактное. А уровень развития современных FPGA и их доступность как раз дают исследователям возможность экспериментировать с реализациями и подстраивать их под собственные нужды.

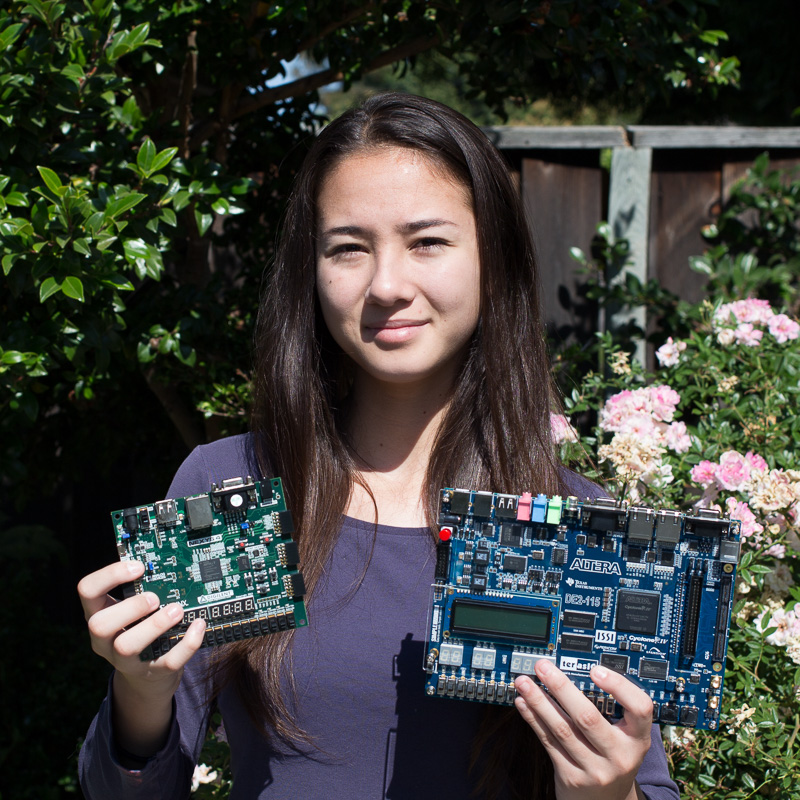

В этой хабрастатье приводится детальное описание простенькой времяизмерительной системы на FPGA Cyclone IV. Статья будет полезна не только для расширения кругозора, но и с методической точки зрения, поскольку реализация системы нетривиальная.

Сделать контроллер елочных гирлянд не просто, а очень просто! Hello World на ПЛИС — это помигать светодиодом. А "С новым годом" на ПЛИС — это помигать несколькими светодиодами. Принцип прост, как и в предыдущих статьях: создаем счетчик, который делит частоту тактового генератора, выбираем биты из слова счетчика, для получения нужной скорости. Несколько бит из этого слова дадут нам определенный шаг отображения (в зависимости от количества выбранных бит 1, 2, 4, 8 и т.д. шагов). В зависимости от номера шага задаем значения для N светодиодов.

Сделать контроллер елочных гирлянд не просто, а очень просто! Hello World на ПЛИС — это помигать светодиодом. А "С новым годом" на ПЛИС — это помигать несколькими светодиодами. Принцип прост, как и в предыдущих статьях: создаем счетчик, который делит частоту тактового генератора, выбираем биты из слова счетчика, для получения нужной скорости. Несколько бит из этого слова дадут нам определенный шаг отображения (в зависимости от количества выбранных бит 1, 2, 4, 8 и т.д. шагов). В зависимости от номера шага задаем значения для N светодиодов.