Новые интерфейсы, шаг в 16 нм и поддержка до 2040 года. Анонсирован новый FPGA линейки Spartan

Компания AMD порадовала публику очередным релизом. На этот раз речь пойдет не об основных и привычных продуктах, хотя компания активно разрабатывает и улучшает архитектуры Zen и Instinct. При этом AMD акцентирует внимание на продвижении и развитии промышленных технологий, унаследованных от Xilinx: AMD объявила о запуске новой линейки FPGA под названием Spartan UltraScale+, которая призвана заменить предшествующие серии Spartan 6 и Spartan 7.

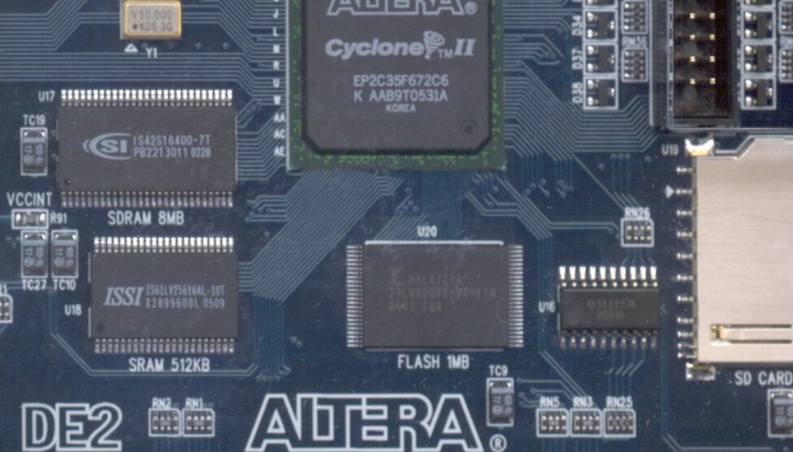

Эти новые программируемые логические интегральные схемы (ПЛИС) отличаются от прочих решений энергоэффективностью и довольно доступной ценой. По сравнению с предыдущими поколениями, Spartan UltraScale+ обеспечивает большую плотность за счет использования 16-нанометрового производственного процесса и предлагает множество новых функций и возможностей.