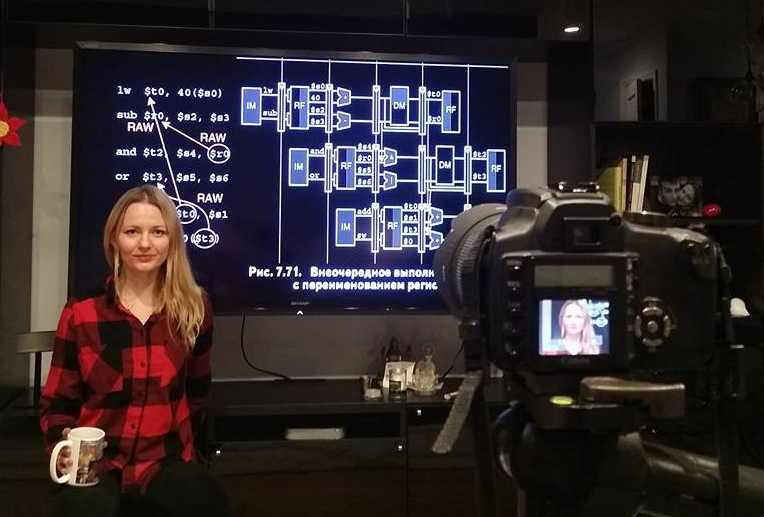

Метастабильность триггера и межтактовая синхронизация

Программируемые логические интегральные схемы

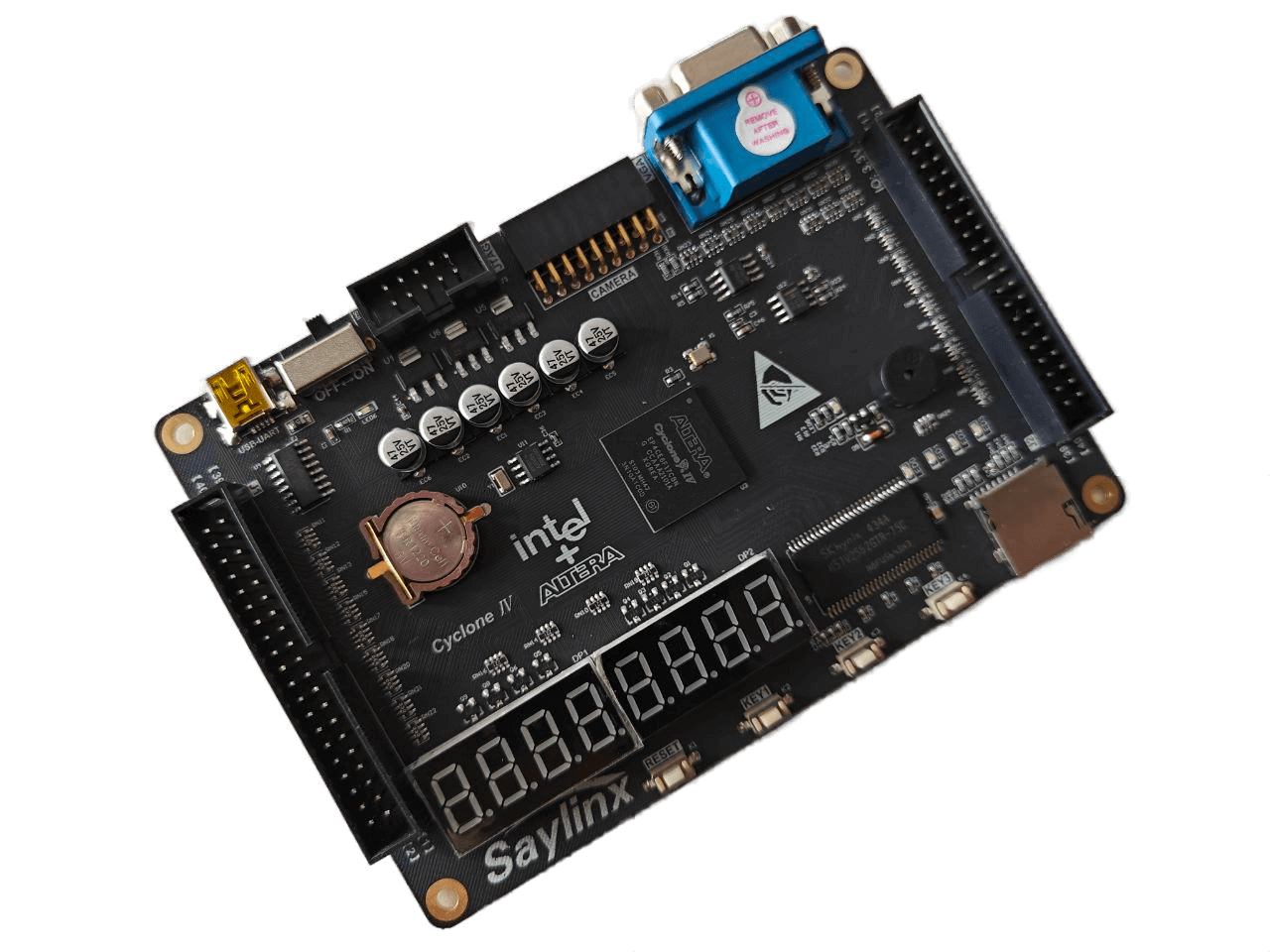

Здравствуйте меня зовут Дмитрий сегодня мы продолжим исследование FPGA плат. Мы напишем контроллер HDMI интерфейса для Altera Cyclone.

Итак, давайте начнем.

Несмотря на то, что предпосылки к отставанию закона Мура от экспоненты обсуждаются ещё с 90‑х, сам закон, с рядом оговорок, справедлив и в наши дни. Это приводит к тому, что если человек поступил в университет в 2010 году, то первые микроконтроллеры STM32F1, выпущенные в середине 2007 года, имели заметные шансы не попасть в его учебные курсы. Как, впрочем, и памяти DDR3 (стандарт также вышел в середине 2007‑го). В момент же получения человеком диплома в 2015‑ом, стандарту DDR4 исполнилось бы три года, STMicroelectronics только что выпустила бы серию STM32F7 со встроенным графическим модулем, а сами STM32 уже два года как имели возможность программироваться при помощи MATLAB и Simulink, минуя код на Си (если верить рекламе).

Подобное положение вынуждает динамично актуализировать знания.

Академические курсы не всегда успевают за прогрессом. А их первоисточник — техническая документация — бывает крайне обширна. Например, базовая документация на микроконтроллеры STM32F103xB насчитывает 1252 страницы. Помимо неё имеются ещё 54 документа типа application note и десятка полтора документов других типов. Поэтому достаточно востребованным источником знаний оказываются профильные сообщества.

Для эффективного получения знаний в подобных сообществах проблема должна быть сформулирована максимально качественно. Ещё в 2001 году появилось (и было переведено на множество языков) фундаментальное руководство «Как правильно задавать вопросы на технических форумах». Представляется, что тезисы данного руководства во многом универсальны и актуальны как для сообществ программистов, так и для сообществ электронщиков, туристов, кулинаров или художников. Однако столь же универсален феномен, когда ответ на сформулированный в соответствии с духом этого руководства вопрос, оказывается не ответом по существу, а чем‑то «идентичным натуральному ответу по существу». Об этом феномене и пойдёт речь в настоящей статье.

В 2015 году скачивания первого русского издания учебника Харрис & Харрис завалили сайт британской компании Imagination Technologies. Книгу стали использовать в МФТИ, ВШЭ МИЭМ, МГУ, МИЭТ, ИТМО и других вузах. С тех пор вышло еще два издания - для ARM и для MIPS, и вот в январе 2022 года выходит новое - для RISC-V и оно уже доступно для предзаказа.

"Цифровая схемотехника и архитектура компьютера: RISC-V" вероятно станет стандартным учебником в российских вузах, как и источником информации для тех, кто хочет попроектировать процессоры на ПЛИС. Ничего лучшего на рынке нет. Паттерсон-Хеннесси не привязан к курсам по языкам описания аппаратуры и не обсуждает тайминг цифровой логики, а Таненбаум устарел.

Кроме этого, архитектура RISC-V становится билетом в будущее для российских процессорных компаний - Ядро купило Syntacore, Байкал Электроникс инвестировал в CloudBear, Миландр выпустил микроконтроллер с архитектурой RISC-V.

Если же вы не хотите работать в российских компаниях, а хотите пройти интервью на проектировщика чипа в Apple, Intel, NVidia, то и в таком случае учебник Харрисов - это самый эффективный способ начать этот путь.

Когда я видел на Хабре упоминание о ПЛИС Lattice, у меня всегда возникал простой вопрос: «А зачем ещё одна ПЛИС?». Вроде всю жизнь хватало пары базовых. Но полгода назад случилось то, что сняло этот вопрос для меня. Пришёл Заказчик и сказал: «Мы делаем проект на ECP5». Против требований Заказчика не попрёшь!

А пока я осваивал работу с этим железом и пытался понять, как обосновать необходимость попробовать то же самое для остальных, мой знакомый, ныне живущий в Штатах, обрадовал новостью, что у его любимого поставщика подходит к концу запас десятых Циклонов и шестых Спартанов. В целом, через три года будет построен новый завод Intel, но что именно там будут производить, он не в курсе. И три года продержаться в любом случае, будет нужно. Короче, сейчас надо иметь возможность быстро мигрировать с одной ПЛИС на другую.

Итого, вчера делать ознакомительную статью про Lattice было рано, завтра – может быть поздно.

Сегодня я расскажу, где купить более-менее дешёвые платы для опытов, как быстро освоить Open Source среду разработки и какие готовые проекты осмотреть в первую очередь.

Я постараюсь в общем рассказать о верификации цифровых схем.

Верификация в данной области — это важный процесс, требующий привлечения опытных инженеров. Например, специалист по верификации, работающий над системами с ЦПУ, как правило должен владеть скриптовыми языками и языками командных оболочек (Tcl, bash, Makefile и т.п.), языками программирования (С, С++, ассемблер), HDL/HDVL (SystemVerilog [10, Appendix C — история языка][11], Verilog, VHDL), современными методологиями и framework’ами (UVM).

Доля времени, затраченного на верификацию, доходит до 70-80% от всего времени проекта. Одна из основных причин такого внимания в том, что к микросхеме нельзя выпустить “патч” после того, как ее отдали в производство, можно только выпустить “silicon errata” (это не касается проектов ПЛИС/FPGA).

Под цифровыми схемами я подразумеваю:

Здравствуйте! Сегодня мы познакомимся с новым семейством дешевых и малопотребляющих ПЛИС от Lattice Semiconductor семейств iCE40LP/HX/LM, научимся работать с фирменным компилятором iCEcube2 и редактором кода Sublime Text 3, а также программировать чип на отладочной плате Lattice iCEstick с помощью прошивки, написанной на SystemVerilog.

Здравствуйте! Сегодня мы познакомимся с новым семейством дешевых и малопотребляющих ПЛИС от Lattice Semiconductor семейств iCE40LP/HX/LM, научимся работать с фирменным компилятором iCEcube2 и редактором кода Sublime Text 3, а также программировать чип на отладочной плате Lattice iCEstick с помощью прошивки, написанной на SystemVerilog.

Пока одни пытаются учить других как надо что-то там делать на ПЛИСах, я продолжаю постигать дзен в имплементации никому ненужных идей не несущих какой-либо практической ценности. Я уже делал и сумматор с одним уровнем логики, и рисовал картины-на-кристалле виваде, и делал ненормальное проектирование в вивадском ECO флоу (txt, видео), и даже делал Трахтенберга на ПЛИСах.

Сегодня мы продолжим путь издевательства над нашей дорогой областью программируемой логики и попробуем што-то новенькое: а именно мы перевернем типичную фразу "Да у нас в плис все параллельно" и сделаем последовательный сумматор на одном Full Adder, но который может складывать числа любой положительной разрядности ну на оооочень высокой тактовой частоте доступной простой смертной логике.

Наконец-то пришла пора продолжить изучение возможностей платы Zynq QMTech и SoC XC7Z020. Следующая интересная задача, которую я для себя придумал в качестве обучающей - оснастить плату Wi-Fi модулем Realtek RTL8822CS и, если Wi-Fi модуль будет не нужен, а нужна будет ещё одна флешка - вторым портом для SD-карточки. Если интересны подробности того, как я это всё реализовал - добро пожаловать под кат.

ПЛИС-культ привет, FPGA-хаб! На днях я релизнул третий номер народного FPGA журнала, которым спешу с вами поделиться

Разработка процессора и вообще программируемых микросхем — процесс сложный и длительный. От старта проектирования до получения первых образцов в кремнии проходит больше года. При этом ПО желательно писать и отлаживать параллельно процессу производства, чтобы оптимизировать сроки выхода продукта. Но как это делать, если «железо» еще не на руках или оно есть в очень ограниченном количестве, а нужно многим?

Спойлер: делать имитацию. О том, какие подходы существуют и как выжать из них максимум эффективности для имитации сложных многоядерных систем, рассказали инженеры-программисты отдела разработки системного ПО YADRO Светлана Бурлака и Александр Солдатов.