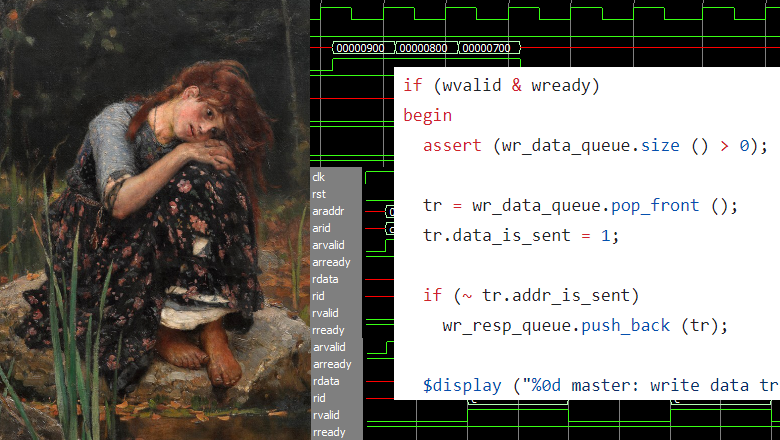

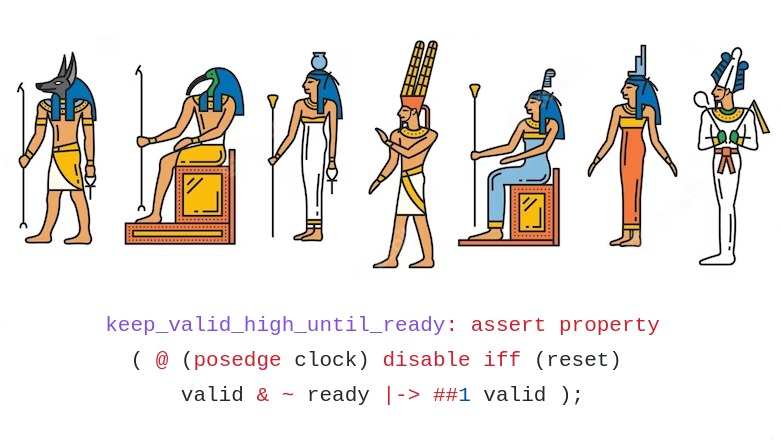

For the last 30 years digital chip design is not a schematic entry anymore: hardware engineers write code just like software engineers.

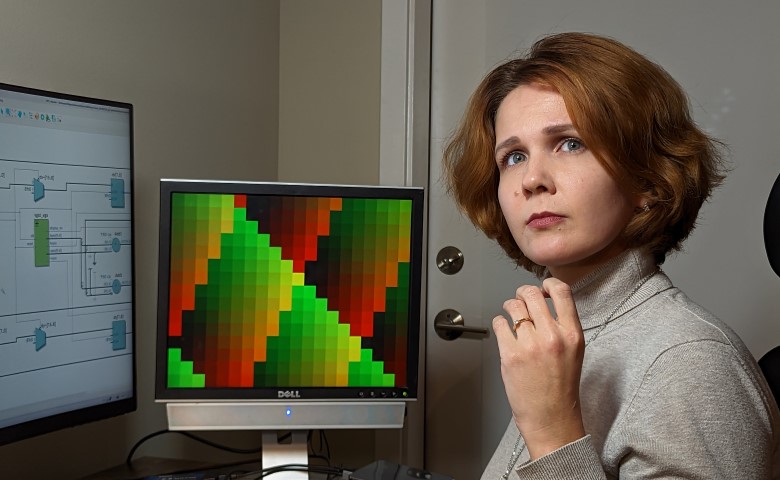

The difference is that the code software engineer writes becomes a chain of CPU instructions stored in memory, while the code in a hardware description language (HDL) becomes the CPU itself, its transistors and metal connections. And not only a CPU: the same technique is used to design processor-less ("fixed function") blocks in GPU that shuffle triangles and pixels, as well as network router chips that edit packet headers 100 times faster than CPU.

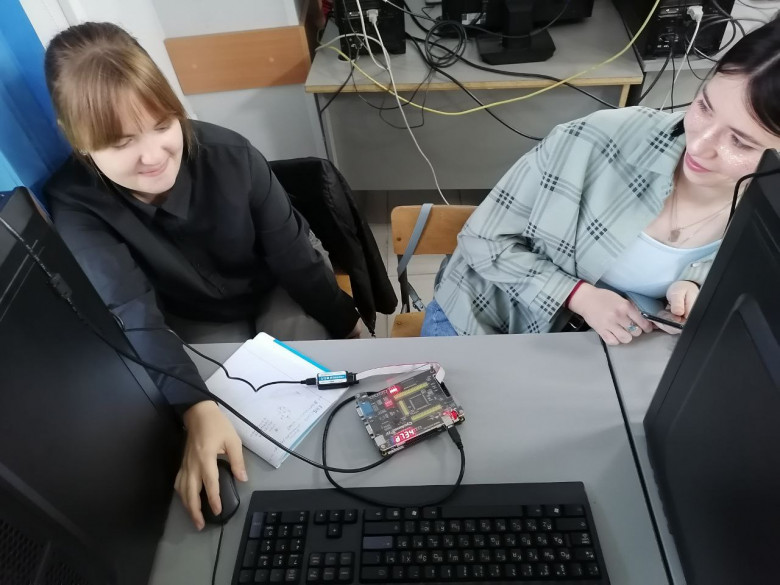

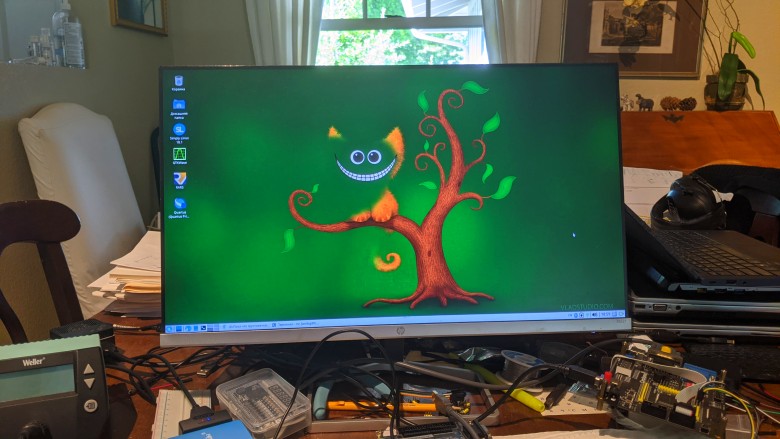

There are ways to experience this workflow without paying a million dollars to a silicon fab. One way is simulation, and another way is to use a matrix of reconfigurable logic cells, a Field Programmable Gate Array (FPGA). You can come on January 14 to Hacker Dojo in Mountain View, California. We have a bunch of computers and FPGA boards, and we will show you how to use them not only to blink LEDs but also to output graphics and recognize music.

This will change your perspective of what the code is.