Защитим вдов и сирот от хищных ИИ-стартаперов

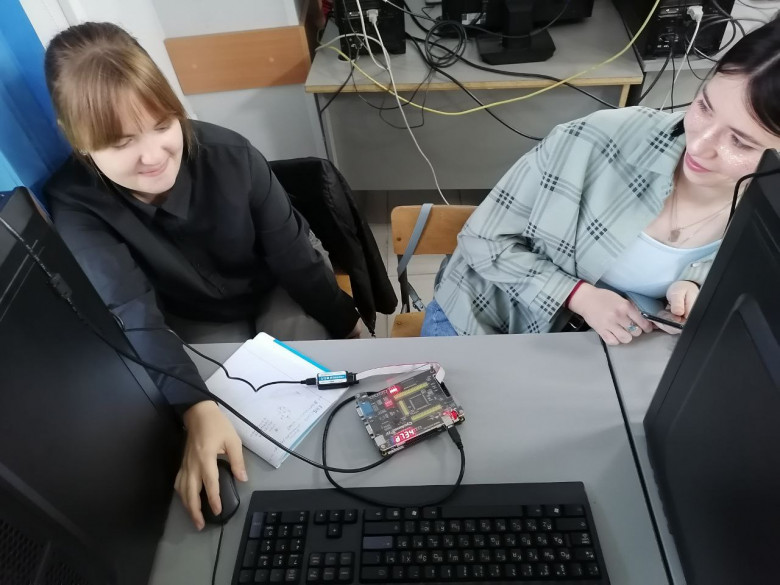

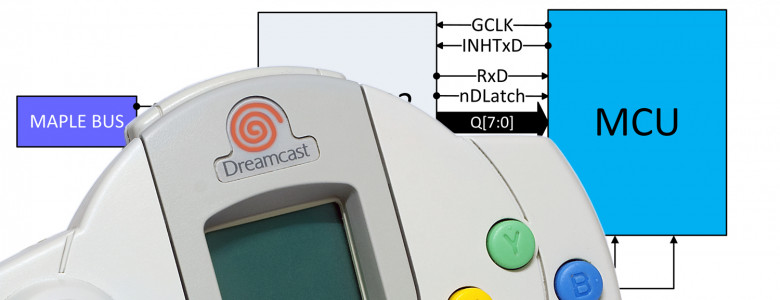

Ко мне на днях обратились сначала два стартапера, а потом и из большой компании по вопросу EDA с помощью AI. Я дал всем троим одну и ту же задачку и думаю сделать еще несколько таких задач, так как два тула эту задачку решили, один тул на ней лег, а еще четыре произвели некий код на языке описания аппаратуры SystemVerilog, который не проходил мой тест, то есть не являлся решением.

В чем социальная значимость таких задачек? Дело в том, что венчурные капиталисты тратят не свои деньги, а деньги, которые институциональные инвесторы, в частности пенсионные фонды - вкладывают в фонды венчурных капиталистов. Тем самым, хотя в США существуют законы, запрещающий неопытным инвесторам ("widows and orphans laws" - "законы о защите вдов и сирот") вкладывать в стартапы напрямую - вдовы и сироты все равно не защищены, так как живут на выплаты из пенсионного фонда, в который вкладывал их безвременно почивший отец семейства.

Также не открою Америку, что стартапер стартаперу рознь. Одни честно делают прототипы и решают задачки от потенциальных пользователей. А другие занимаются shmoozing - то есть ходят по тусовкам и пытаются что-то впарить VC говорением в стиле Остапа Бендера.

И вот чтобы защитить венчурных капиталистов (а через них - вдов и сирот) от стартаперов второго типа, мы с соратниками сделали задачку под названием SystemVerilog Microarchitecture Challenge for AI No.1: