Год назад вышло бесплатное электронное издание на русском языке всеохватного вводного учебника Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера». Книга попала в струю, ее скачивания завалили британский сайт Imagination Technologies (дважды —

1,

2), после чего учебник стали использовать преподаватели московских МФТИ, МГТУ, питерского ИТМО, киевского КНУ, КПИ и других вузов. Интересной особенностью учебника является то, что его перевод на русский сделала группа энтузиастов: преподавателей российских и украинских университетов, русских сотрудников компаний в Silicon Valley (AMD, Synopsys, Apple, NVidia ...) и российских компаний (НИИСИ, МЦСТ, Модуль ...).

При этом, электронное издание Харрис-энд-Харрис сформатировано для планшета, и уже после первых скачиваний посыпались емейлы, когда же учебник будет и на бумаге. И вот час настал —

Учебник Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера» можно заказать на бумаге (выходит в новогоднюю ночь). В этом посте я покажу, чем этот учебник отличается от других. Бонус: фотки участников и участниц проекта!

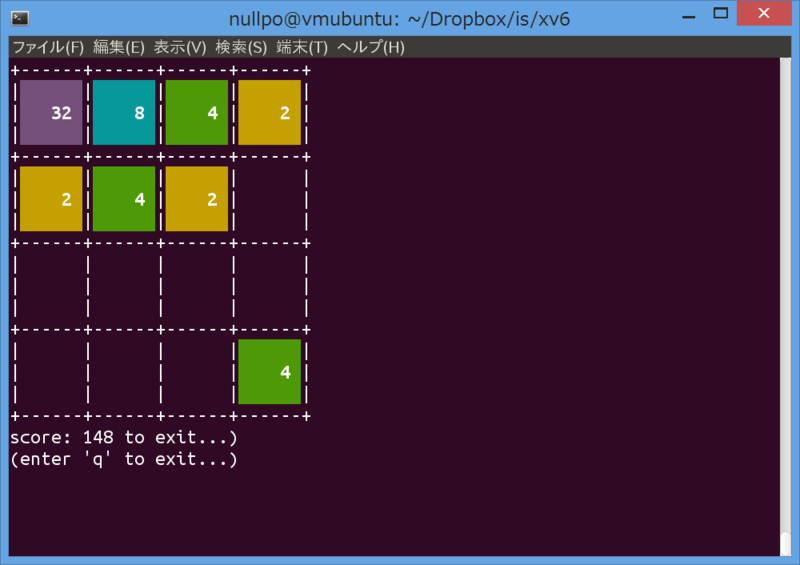

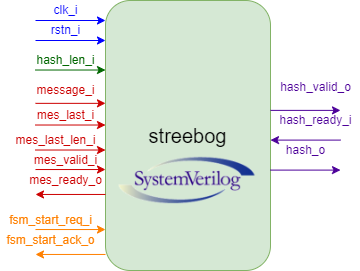

Есть много учебников, которые хорошо вводят в цифровую логику на уровне триггеров и мультиплексоров, или в программирование готовых микроконтроллеров на ассемблере, или показывают красивые диаграммы процессорных конвейеров, или обучают синтаксису Verilog или VHDL. Но если учить скажем микроархитектуре без HDL, или если например пропускать уровни между триггером и программированием микроконтроллера, то получатся студенты, которые могут сдать экзамен и спорить умными словами в интернете, но ничего не могут сделать практически.

Учебник H&H решает эту проблему:

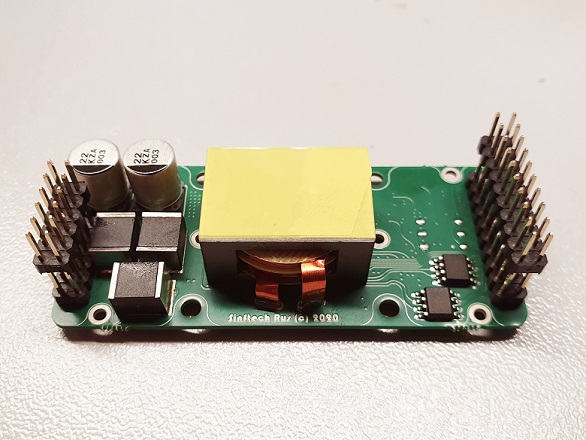

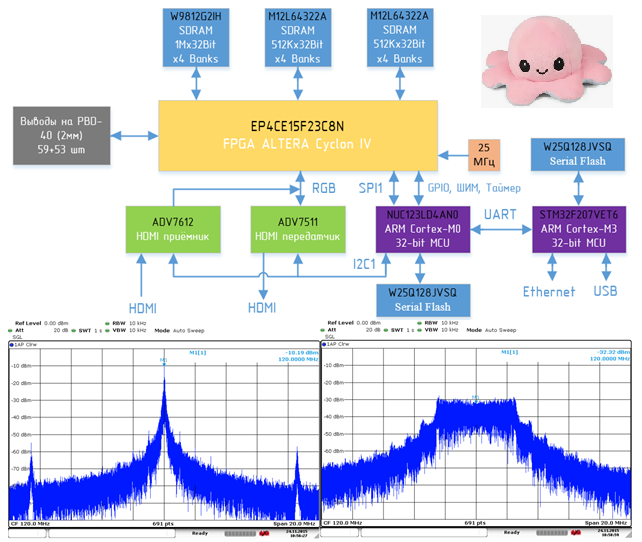

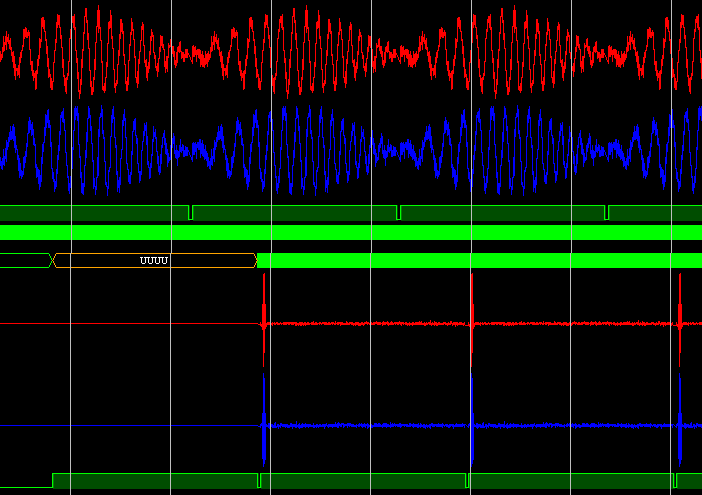

Недавно мы применили плату

Недавно мы применили плату