В данной статье хочу немного рассказать о небольшом исследовании реализации expected, в которой используется стирание типа ошибки.

Пользователь

В данной статье хочу немного рассказать о небольшом исследовании реализации expected, в которой используется стирание типа ошибки.

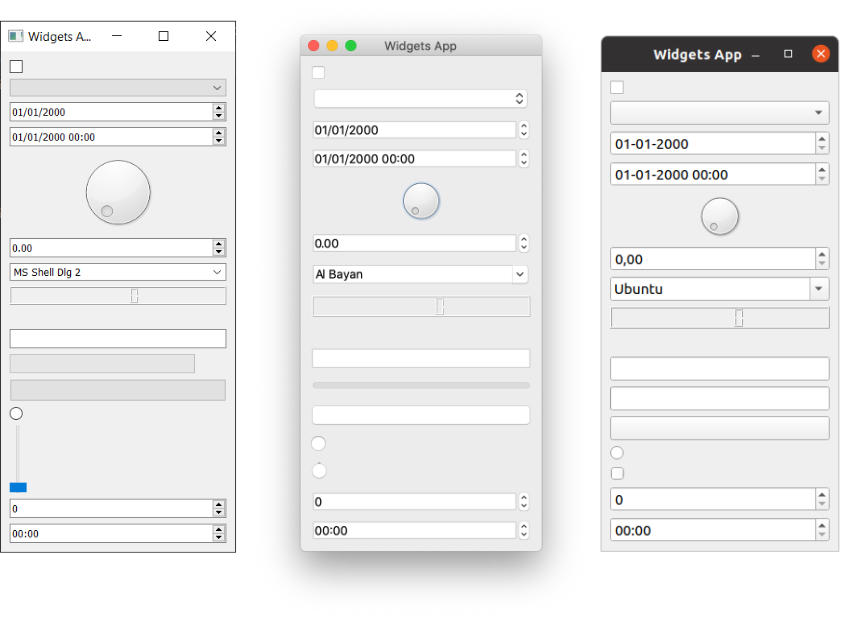

К старту курса по разработке на Python делимся детальным руководством по работе с современным PyQt для новичков. Чтобы читать было удобнее, мы объединили несколько статей в одну:

3. Виджеты

За подробностями приглашаем под кат.

Многие слышали про Midjourney, но про то, что есть локальная Stable Diffusion, которая может даже больше, знает уже куда меньше людей, или они не знают, что она локальная. И если они пробовали её онлайн, то быстро приходили к выводу, что она сильно хуже чем Midjourney и не стоит обращать на неё более внимания. И да, SD появился раньше Midjourney. Для запуска хватит и cpu или 4гб видеопамяти.

Аналогично с chatGPT, про попытку сделать его локальную версию, не требующую супер компьютер, тоже мало кто слышал и знает, несмотря на то, что выходило несколько статей.

Привет! В этой статье мы научимся добавлять WebAuthn в веб‑приложения со стороны frontend‑разработчика. WebAuthn представляет собой новый метод аутентификации, который обеспечивает более высокий уровень безопасности, заменяя устаревшие пароли и SMS‑подтверждения на аутентификацию на основе публичных ключей.

В этой статье мы поговорим о том, чего нам стоят безопасные доступы к элементам массива, и как современные компиляторы пытаются сделать код снова быстрым.

Итак жил был фреймворк Qt и последние 10 лет ничего в нем не менялось. И захотел один чел написать свой QTableView с нужным ему функционалом, а именно захотелось ему выводить ячейки в несколько рядов (по горизонтали) в одной строке. Ещё ему хотелось растягивать одну из ячеек по ширине двух других.

Искал, искал чел готовый пример в интернете и не находил. И вот однажды подумал он посмотреть как сделан внутри сам QTableView и стало плохо ему от количества строк кода, не одна тысяча там.

Чем же так занимательно число 6174? Казалось бы, это обычное натуральное чётное четырёхзначное число. Не лучше и не хуже, чем, скажем, соседние 6173 и 6175. Оно даже не является простым. Тем не менее, это число имеет своё собственное название — постоянная Капрекара. А ещё оно относится к так называемым «числам великой радости».

Давайте разбираться, что же в этом числе такого особенного. Займёмся несложными вычислениями...

Главная идея была в том, чтобы проверить возможно ли из старого Android устройства сделать "полноценный" сервер с nginx, php-fpm, MariaDB и запустить на этом Wordpress. Оказывается можно и при этом с хорошим результатом.

Устройство: Xiaomi Mi 4c 2015 года, разблокирован разгрузчик, TWRP, Android 10 (Havoc OS 3.0), Gapps не устанавливались для экономии ресурсов, root отсутствует.

Сравнительно недавно в stdlib плюсов появилось форматирование строк «как в питоне», а точнее, как в библиотеке fmt. И я, как смелый и отчаянный, решил этим воспользоваться. Возможно, аксакалы и настоящие разработчики скажут, что я всё делаю не так, и вообще не то, но я буду рад такой критике, если она поможет легче жить ;)

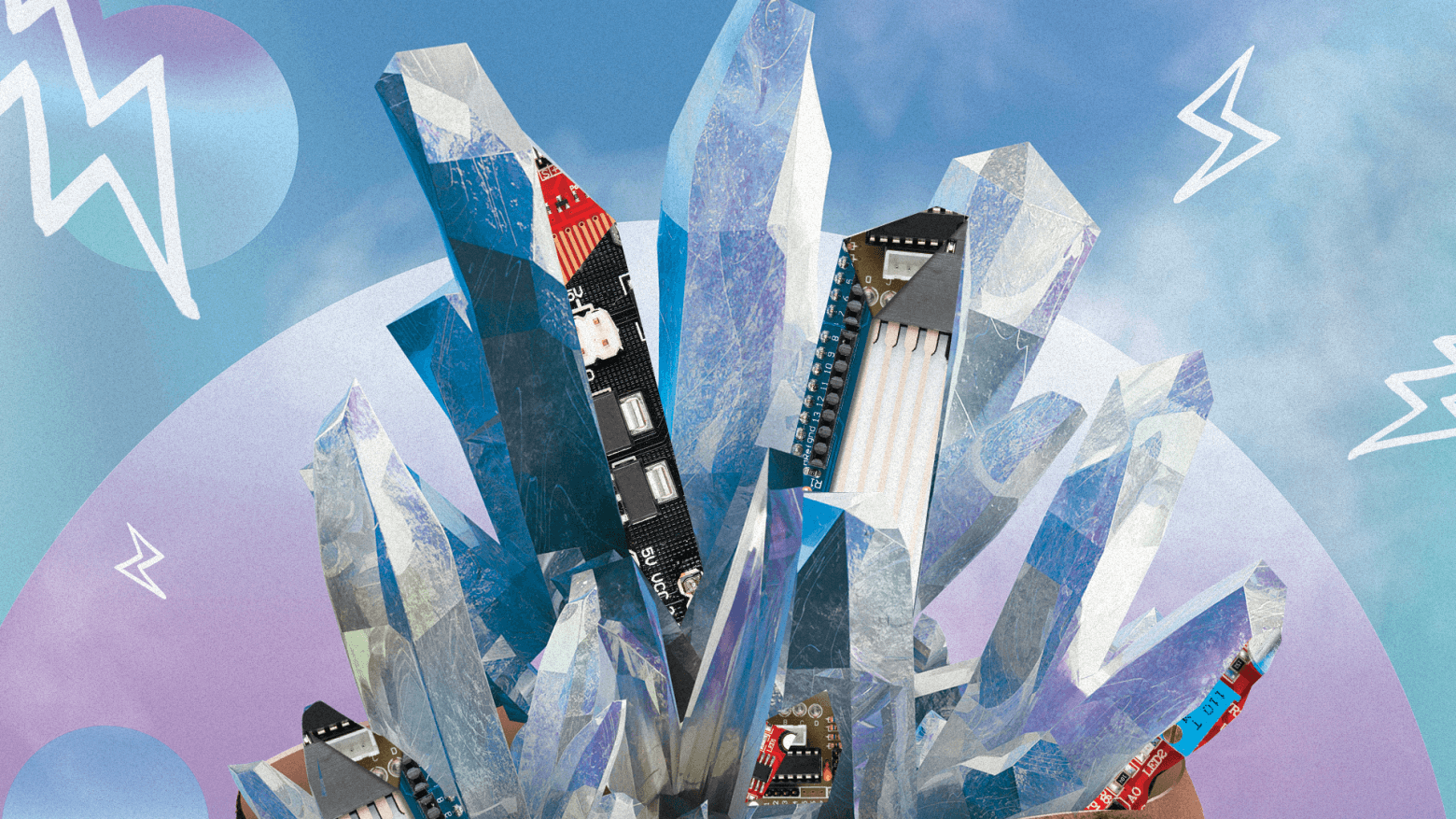

Практически любой природный ресурс, в особенности полезные ископаемые, нужно пропускать через серьёзные технологические процессы, прежде чем этот ресурс можно будет использовать. Так дело обстоит с нефтью, газом, рудами и т. п.

С кварцем всё несколько иначе: его можно просто добывать, немного очищать, измельчать и пускать в дело. Ничего особенного, всё достаточно просто. Тем не менее добываемый кварц не всегда соответствует критериям, предъявляемым промышленностью — электронной и другими отраслями. Поэтому кварц научились ещё и синтезировать. Обо всём этом поговорим под катом. Надевайте строительные каски — и поехали!

В последнее время появилось много микроконтроллеров на ядрах ARM Cortex-M*, которые поддерживают аппаратную реализацию математики плавающей запятой (FPU). В основном FPU работают с одиночной точностью (float) и её вполне достаточно для работы с сигналами, полученными с АЦП. FPU позволяет забыть о проблемах дискретизации и проблемах переполнения целочисленных вычислений. FPU быстр - все математические операции с одиночными float, кроме деления и взятия корня, занимают на Cortex-M4F один такт. Поэтому после перехода на Cortex-M4F мы вздохнули свободно и стали писать математику на float. Как же мы удивились, найдя в скомпилированном коде математические операции над double с программной, очень медленной эмуляцией.

В статье рассказывается, как обнаружить и исправить присутствие double в прошивках, где ядро аппаратно поддерживает тип float, но не поддерживает double.

Работа ведётся в среде IAR Embedded Workbench на примере реального кода на языке Си.

Один античный оратор говорил, что всем людям свойственно ошибаться. Прошло много веков, а человек продолжает совершать ошибки каждый день. Даже беглое заполнение формы на сайте не обходится без опечаток.

Хороший UI/UX помогает пользователю избежать большинства таких проблем. Инструментов контроля огромное количество, сегодня расскажу про один их них — создание маски для поля ввода силами Javascript.

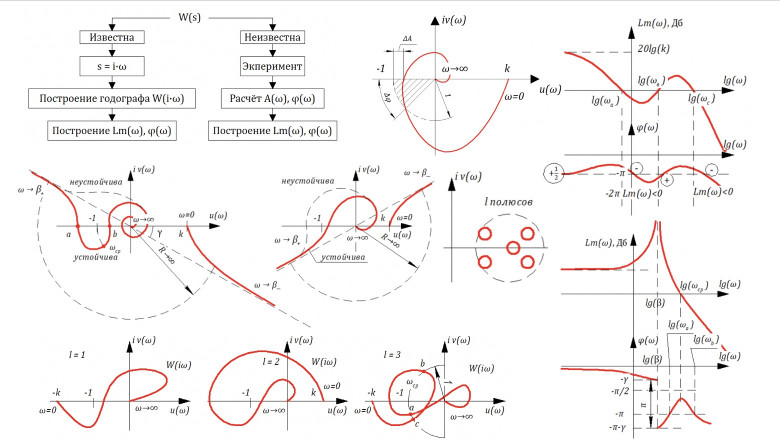

Продолжаем лекции по управлению в технических устройствах (УТС). Данные лекции читаются в МГУТ им. Баумана. Автор лекций к.т.н. Козлов Олег Степанович, кафедра Ядерные Энергетические Установки, факультета машиностроения. За что ему огромное спасибо!

1. Введение в теорию автоматического управления.2. Математическое описание систем автоматического управления 2.1 — 2.3, 2.3 — 2.8, 2.9 — 2.13.

3. ЧАСТОТНЫЕ ХАРАКТЕРИСТИКИ ЗВЕНЬЕВ И СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ РЕГУЛИРОВАНИЯ. 3.1. Амплитудно-фазовая частотная характеристика: годограф, АФЧХ, ЛАХ, ФЧХ. 3.2. Типовые звенья систем автоматического управления регулирования. Классификация типовых звеньев. Простейшие типовые звенья. 3.3. Апериодическое звено 1–го порядка инерционное звено. На примере входной камеры ядерного реактора. 3.4. Апериодическое звено 2-го порядка. 3.5. Колебательное звено. 3.6. Инерционно-дифференцирующее звено. 3.7. Форсирующее звено. 3.8. Инерционно-интегрирующее звено (интегрирующее звено с замедлением). 3.9. Изодромное звено (изодром). 3.10 Минимально-фазовые и не минимально-фазовые звенья. 3.11 Математическая модель кинетики нейтронов в «точечном» реакторе «нулевой» мощности.

4. Структурные преобразования систем автоматического регулирования.

5. Передаточные функции и уравнения динамики замкнутых систем автоматического регулирования (САР).

Недавно для популярного пакета для работы с мультимедиа устройствами (в основном камерами) появилась возможность сборки через meson. В данной статье мы рассмотрим как это осуществить. Собирать будем в Ubuntu 22, но подойдёт и любой другой популярный современный дистрибутив.

NULL. Shit happens, как говорится…